Предлагаемое устро йютво Может быть использовано для Построения надежных переС1чет1ных схем IB уст.ройствах автоматики и вычислительной техиики.

В устройствах а1ВТО|Мати1КИ, вычислительной техники и При ореобразова.нии информации и;апользуют |пересчетные схе-мы с избыточаюстью, т. е. требующи-е зиачительного количества дополнительного оборудования. Так, для коррекции любых ошибок в одной лереочетной схеме необходимо утроение оборудования и мажоритарный, элемент, выбирающий два совпадающих сигнала из трех.

Лредлагаемая схема лозволяет 0|Существить корр екцию ошибок при ср.а В Нитель1НО небольшой затрате дополнительноло оборудо.вания. Это достигается тем, что выходы п-2-R основных и 2R избыточных ячеек соединены с п входами порогового элемента с весами входов, равными единице, выход которого подключен к выходу устройства и к входам синхронизации.

Здесь и в дальнейшем под ошибками понимаются 1ка.к посто-янные отказы, вызванные конструкт и вны МИ неисправностями, так и сбои, вызванные действием шомех.

бы получить ИМпульс на ее выходе. Пересчетные схемы можно строить как последовательным включением элементарных пересчегных ячеек (например, триггеров или их наборов) с коэффидиента.ми пересчета Ki, К2, .. , Кп, так и параллельным их включением, если числа ki, kz, ..., kn взаимно простые. При этом в обоих случаях должно выполняться неравенство

,.. , КпПримем, что

. ..kn

и что для однозначного представления числа /(требуется

п - S чисел ki, т. е.

. . .kn SТогда, если числа ki, kz...kn взаимно простые, то пересчегная схема может быть построша такИМ образом, что она остается работоспособной при ошибках в любых г пересчетных ячейках (если S 2r) или обнаруживает любые ошибки в S пересчетных ячейках.

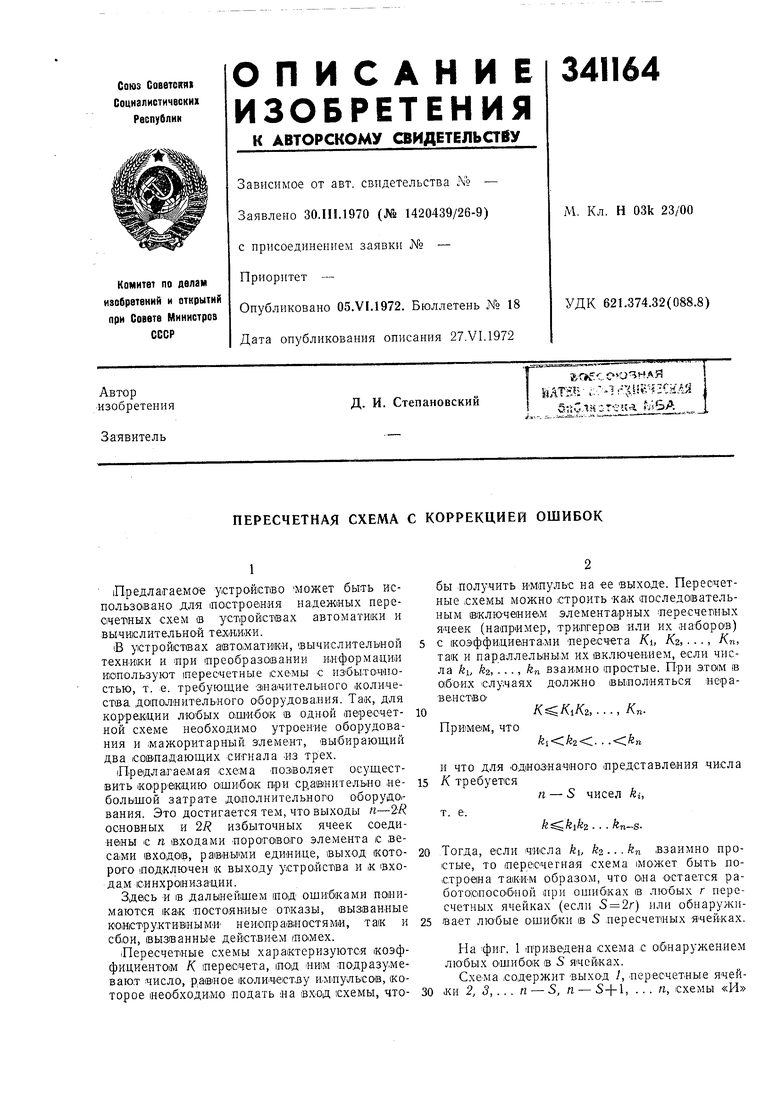

4, 5, и 6, схему 7 запрета, шину 8 сигаала ошибки, шину 9 .выходного сигнала.

По1ложи.м, ЧТО сИГиалы на выходе t-й ячейки ложвляются в случае выпол еиия сравиения (mod Ki), т. е. когда состояние ячейки ui ,соот1вет,ст1вует остатку от деления числа К. 1иа /С,-. В .случае иормальиой сигналы на выходах всех ячеек, а, следовательно, и «а входах схем совиадеиия 4, 5 и 6 и схемы запрета 7 появятся оде овр ем ей но после прихода «а вход 1 .схемы точио К импульсов. В этом случае на шине 8 сигнал ошибки отсутствует, а :иа шиие 9 появится импульс, соот1ветст1вуюи1,ий окончанию цикла пересчета. Этот .имт1ульс служит выходным сигналом пересчетиой схемы и одновремеяио подается для устаповки всех ячеек в (пулевое состоя1иие. .В случае ошибок IB любых S или меньшем числе ячеек сигналы иа выходах схем 4 н 5, а Следовательно, и «а входах схемы 7 ие совпадут. При этом на 1пине 5 появится сигнал ошибки, что свидетельствует о нарушении (Нормальной работы устройства.

ОбоояоваНие этото факта можно получить, если рассмотреть схему на фиг. 1 как схему арифметического .контроля по модулю

Kn-S+iKn--S+Z.--KnВ такой схеме 01шибка «е обнаруживается, если она кратна модулю. Такая ошибка характеризуется из-менением состояния по меньшей S+1 ячеек. Если обеспечить первоначальную устаиовку .состояяия - k (mod Ki) «а всех нересчетных ячейках, то состояние, соот1веТ|СТ1вуюЩее ЧИслу К, также соответствует окончанию цикла пересчета, т. е. моменту, обнуления всех ячеек.

Схе.ма .для случа.я исправления онгибок в г иересчетных .ячейках .может быть посгроена с числО|М избыточных ячеек 5 2г на основе приведеиной вьшге .схе.мы об-иаружения ошибок. ДлЯ этого необходимо .различные со.четания п - г сигналов с выходов ячеек подать на С схеМ обнаружения ошнбок, а с .выходов этих схем - на схему «ИЛИ.

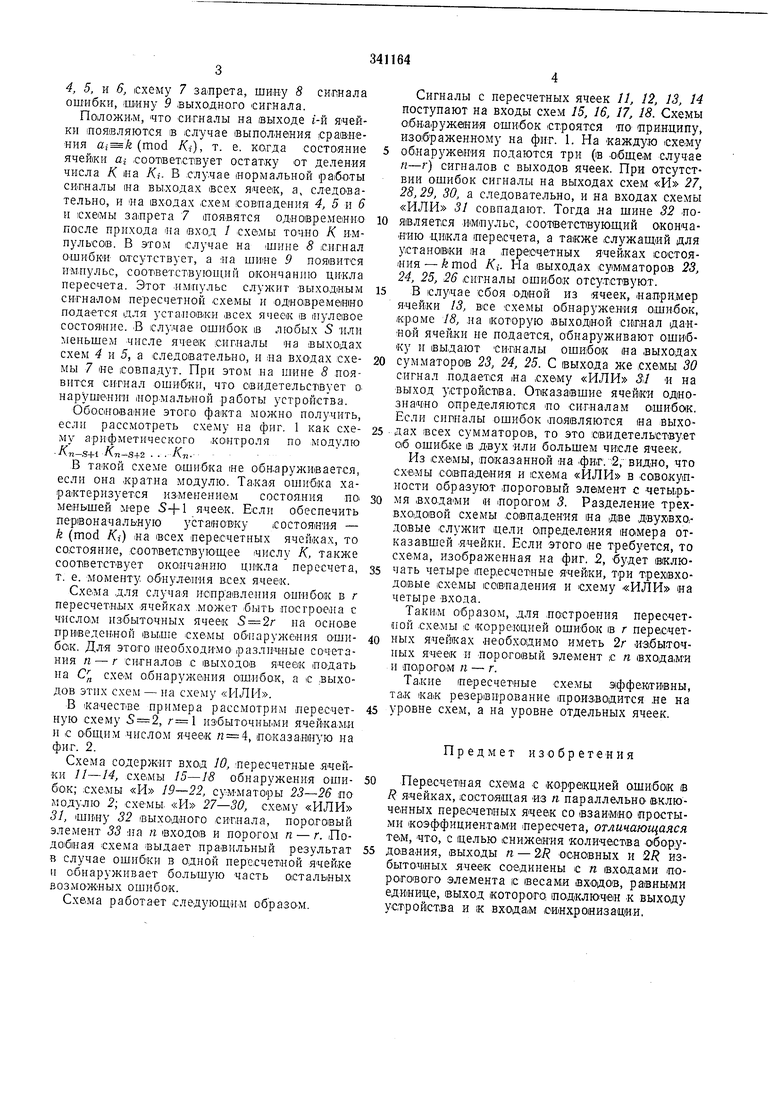

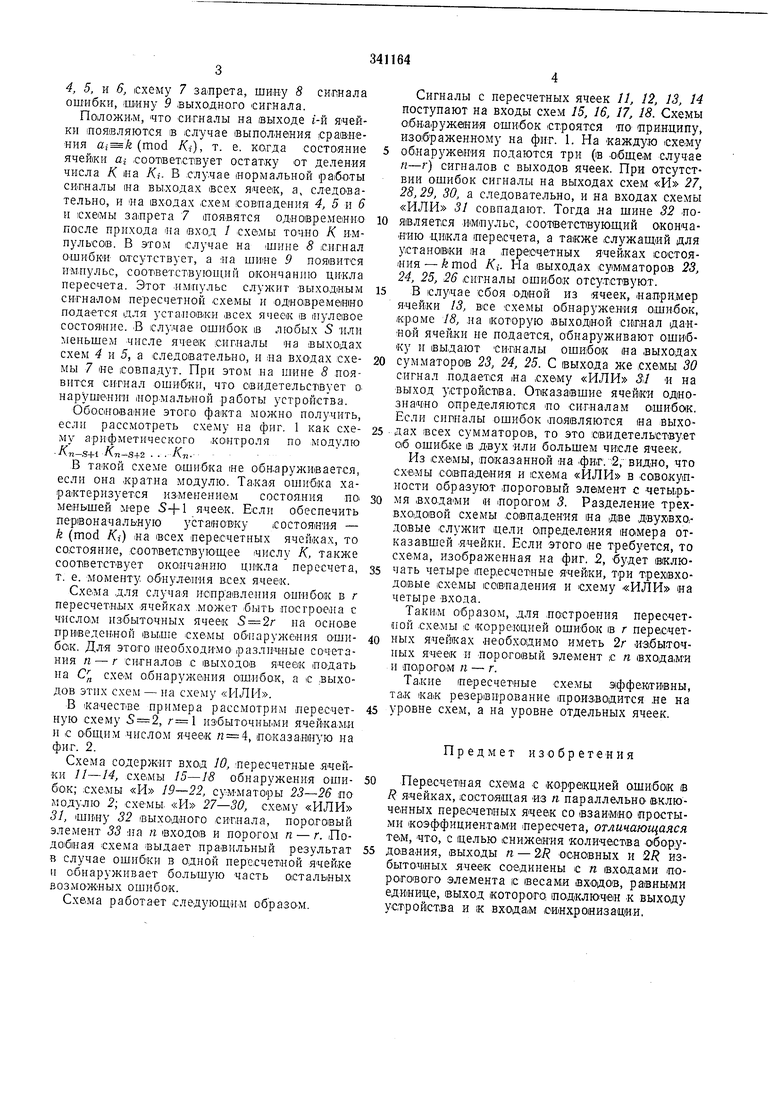

В ка.честве примера рассмотрим нере.счетную схему 5 2, избыточны.ми ячейкам.и и с числом ячеек п 4, |ПО«аэа.Н1ную на фиг. 2.

Схема содержнт вход 10, /пересчетн.ые .ячейки 11-14, схе;МЫ 15-18 обнаружения ошибок; схе-мы «И 19-22, суММаторы 23-26 по модулю 2; схемы, «И 27-30, схему «ИЛИ 31, шину 32 выходного сигнала, пороговый элемент 33 на п входов и порогом п - г. Подобная схема выдает правильный результат в случае ошибки в о.диой пересчетной ячейке II о-биаруживает большую часть остальных возможных ошибок.

Схема работа.ет следующим образОМ.

Сигналы с пересчетных ячеек 11, 12, 13, 14 поступают на входы схем 15, 16, 17, 18. Схемы

.яаруж.внИЯ оши.бок (Строятся по а1ри.н.ципу, изо бражен:ному на фиг. 1. На каждую icxe.My обнаружения подаются три (в .01бш;е,м п-г) сигналов с выходов ячеек. При отсутствии ошибок сигиалы на выходах схем «И 27, 28,29, 30, а следовательно, и на входах схемы «ИЛИ 31 совпадают. Тогда .на шине 32 поЯ1вляет;ся иАшульс, сооте етспнующий окончанию цикла пересчета, а также с.лужащий для установки на нересчетных ячейках состояния - k mod Кг. На выходах .сумматоров 23, 24, 25, 26 сигналы ошибок отсутствуют.

В случае сбоя одной из ячеек, например ячейки 13, все схемы 0|бнаруже.ния ошибок, кроме 18, на которую выходной сигнал даннон ячейки ие подается, обнаруживают о.ши|б«у и вы.дают сигналы ошибок иа .выходах

сумматоров 23, 24, 25. С 1выхо.да же схемы 30 сигнал подается на схему «ИЛИ 3i/ н на выход устройства. Отказавшие ячейки однозначно о.пределяются по сигналам ошибак. Если сипналы ошибок появляются «а выходах .всех сумматоров, то это свидетельствует 0:6 ошибке в .двух ИЛИ большем числе ячеек,

Из схемы, показанной на .фиг. -2, видно, что схемы совпадения и 1схема «ИЛИ в совокупности образуют .пороговый элемент с четырьмя .вхо.дами и (Порогом 5. Разделение трехВХО.Д01ВОЙ схемы .совпадеНИя на две двухвхо.до.вые служит цели определения иомера отказавшей .ячейки. Если этого не требуется, то схема, изображенная на фиг. 2, будет включать четыре пер.есчетные ячейки, три трехвхоД01вые схемы совпадеиия и схему .«ИЛИ на четыре входа.

Таким образом, .для построения пересчетпой схе.мы с коррекцией ошибок в г пересчетных ячейках необхо-димо иметь 2г .иабыточиых ячеек и пороговый элемент с п входалги и порогом п л

Та.кие (иересчетные схемы эффективны, так как ре.зервирование производится .не на

уровне схем, а иа уровне отдельных ячеек.

Предмет изобретения

Пере.счетная схема с (Коррекцией ошибок е R ячейках, состо.Я(Щая из п паралле.льнО а.ключенных пересчетяых ячеек со (Взаимно простыми коэффициентами пересчета, отличающаяся тем, что, с щелью снижения количества оборудования, выходы п - 2R основных и 2 избыточных ячеек соединены с п вхО(Дами порогового элемента с |весам,и входов, равными единице, выход 1котор.ого 1по.Д(КЛЮче(Н к выходу устройства и к входа|М синхрояизащии,

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНЫЙ СЧЕТЧИК ИМПУЛЬСОВ с КОНТРОЛЕМ ОШИБОК | 1971 |

|

SU315294A1 |

| Делитель частоты с коррекцией ошибок | 1975 |

|

SU514441A1 |

| УСТРОЙСТВО для СЧИТЫВАНИЯ символов, НАПЕЧАТАННЫХ МАГНИТНОЙ КРАСКОЙ СТИЛИЗОВАННЫМ ШТРИХОВЫМШРИФТОМ | 1970 |

|

SU271923A1 |

| Устройство формирования переменных временных интервалов | 1975 |

|

SU547031A1 |

| ПЕРЕСЧЕТНАЯ ЯЧЕЙКАВСЕСОЮЗНАЯJUlTHTHO-KKil^SClWЬИ6.ПИОТЕНА | 1971 |

|

SU305687A1 |

| РЕВЕРСИВНАЯ ПЕРЕСЧЕТНАЯ ДЕКАДА | 1969 |

|

SU238249A1 |

| УСТРОЙСТВО для РЕГУЛИРОВАНИЯ ЭТАЛОННОГО СИГНАЛАВРЕМЕНИ | 1971 |

|

SU309465A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО КОНТРОЛЯ УРОВНЯ ВЕЩАТЕЛЬНОГО СИГНАЛА | 1973 |

|

SU394948A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ТРИГГЕРОВ | 1972 |

|

SU353218A1 |

| ПЁРЁСЧЁТНОЁ УСТРОЙСТВО | 1971 |

|

SU307523A1 |

Даты

1972-01-01—Публикация