Изобретение Относится к автоматике и вычислительной технике.

Известны устройства для регулирования сигнала времени, содержащие сдвигающие регистры, формирователи и кольцевые пересчетные схемы.

Предложенное устройство отличается тем, что оно содержит корректор, подключенный к кольцевой пересчетной схеме и связанный с ней внутренними логическими связями.

Целью изобретения является создание отHocиteльнo простого, надежного, дещевого устройства, позволяющего формировать сигналы эталона времени в широком временном диапазоне (от долей сек. до нескольких десятков суток), плавно регулировать эталон времени, получать высокую точность отсчета в эталоне времени во всем временном диапазоне при постоянной относительной ошибке отсчета, определяемой стабильностью частоты задающего генератора, согласовывать выходные сигналы с внешними исполнительными и накопительными устройствами.

Предложенное устройство отличается от известных тем, что оно содержит корректор, выполненный на сдвоенном переключателе, подключенный к ячейкам кольцевой параллельной пересчетной схемы, реализуюшей систему счисления в остаточных классах и выполненной из групп кольцевых сдвигающих регистров независимого действия с логическими обратными связями; к выходу корректора подключена схема совпадения, связанная через корректор со входом сброса и через линию

задержки с входом запуска параллельной пересчетной схемы.

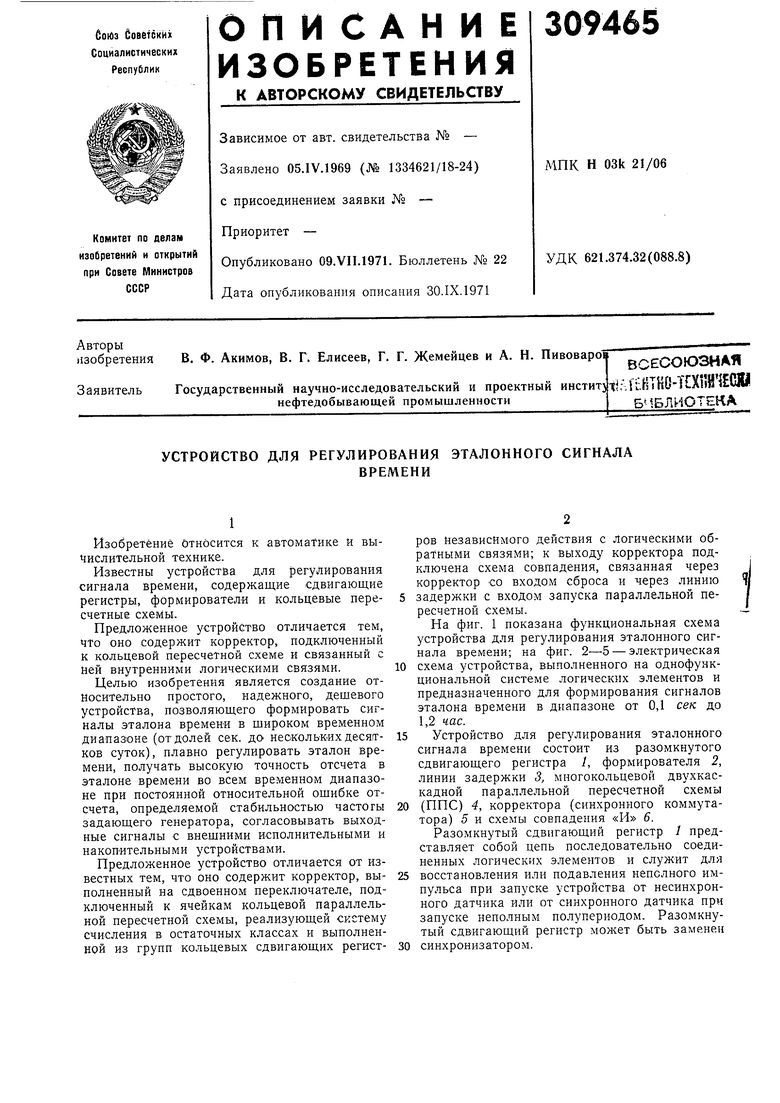

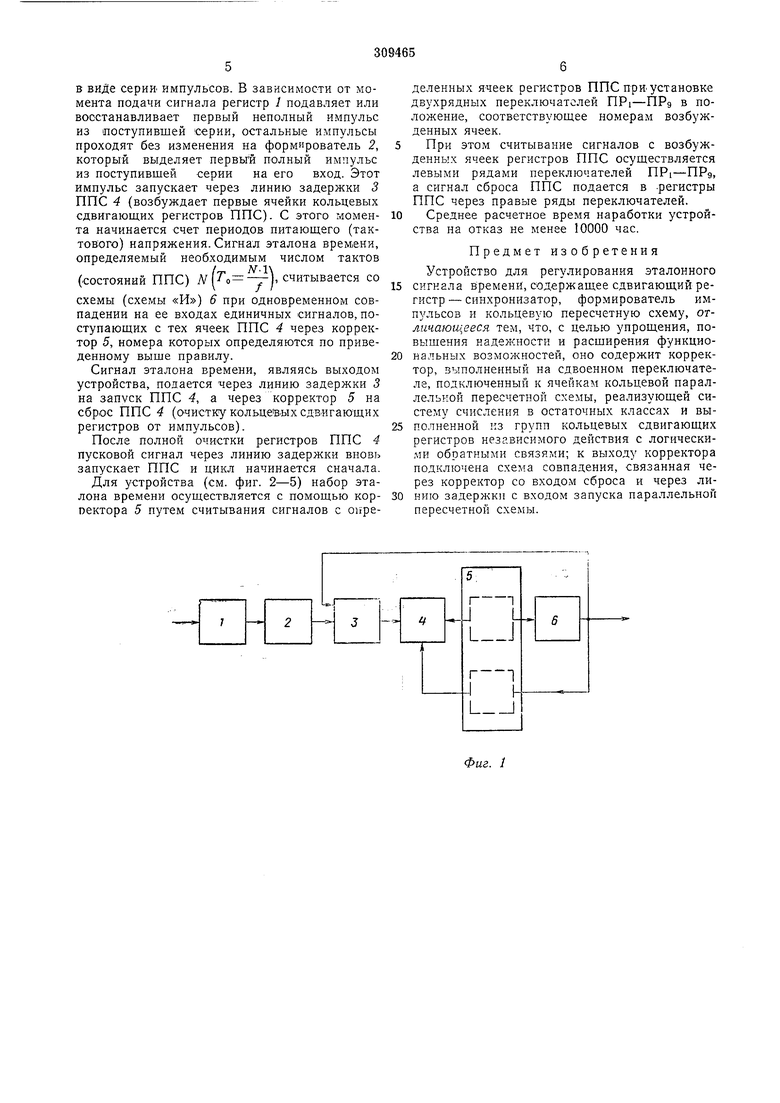

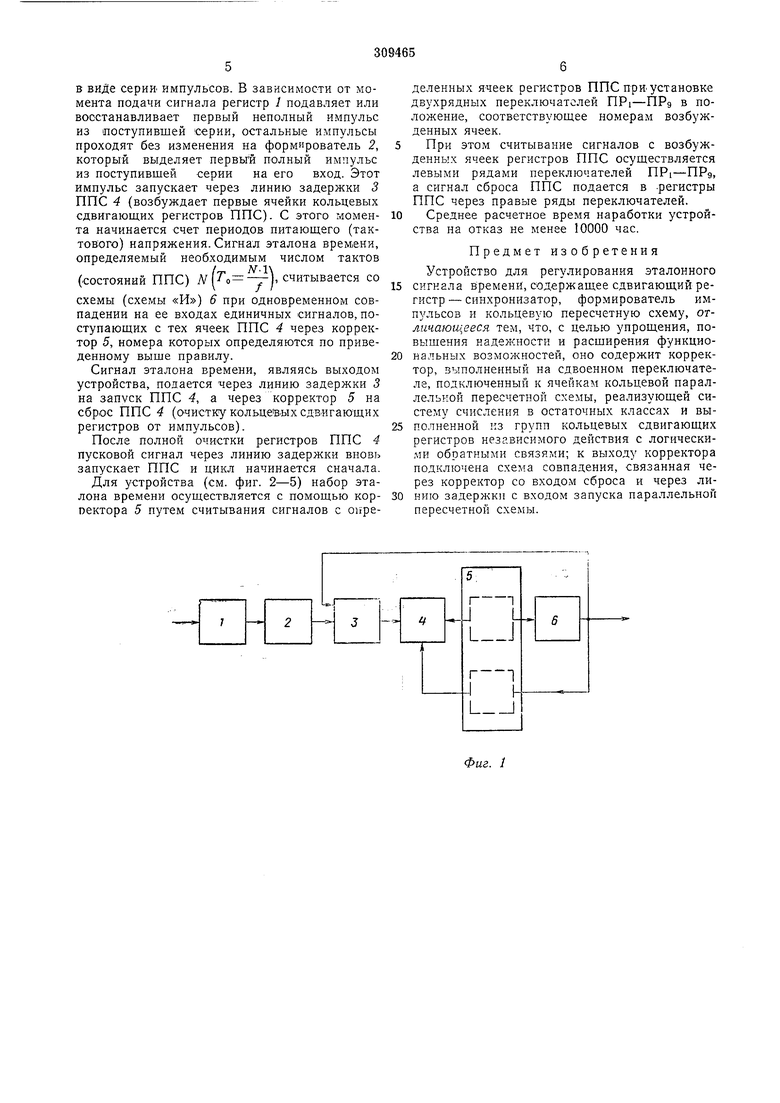

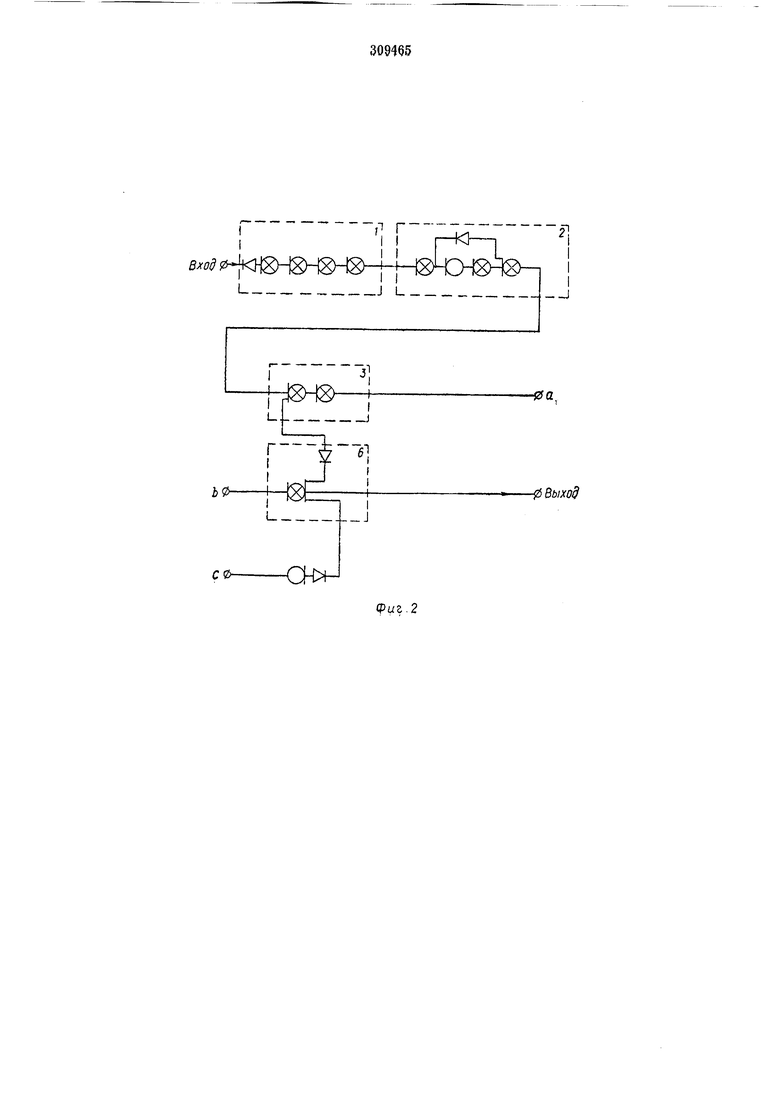

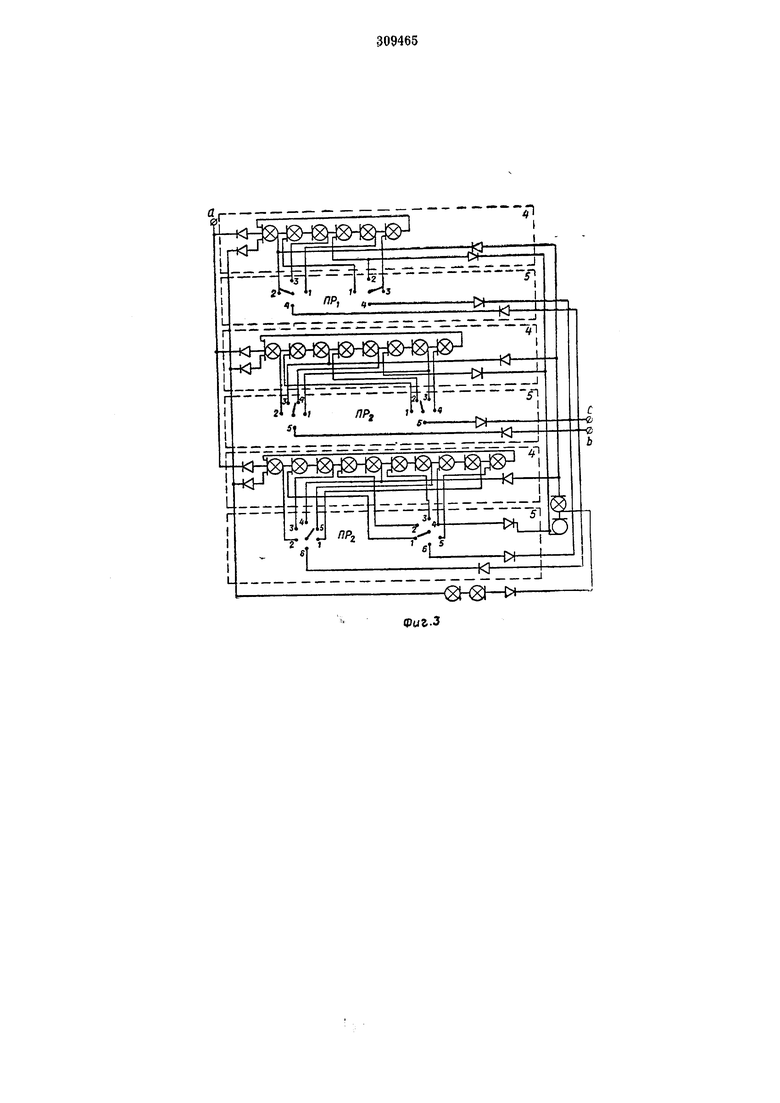

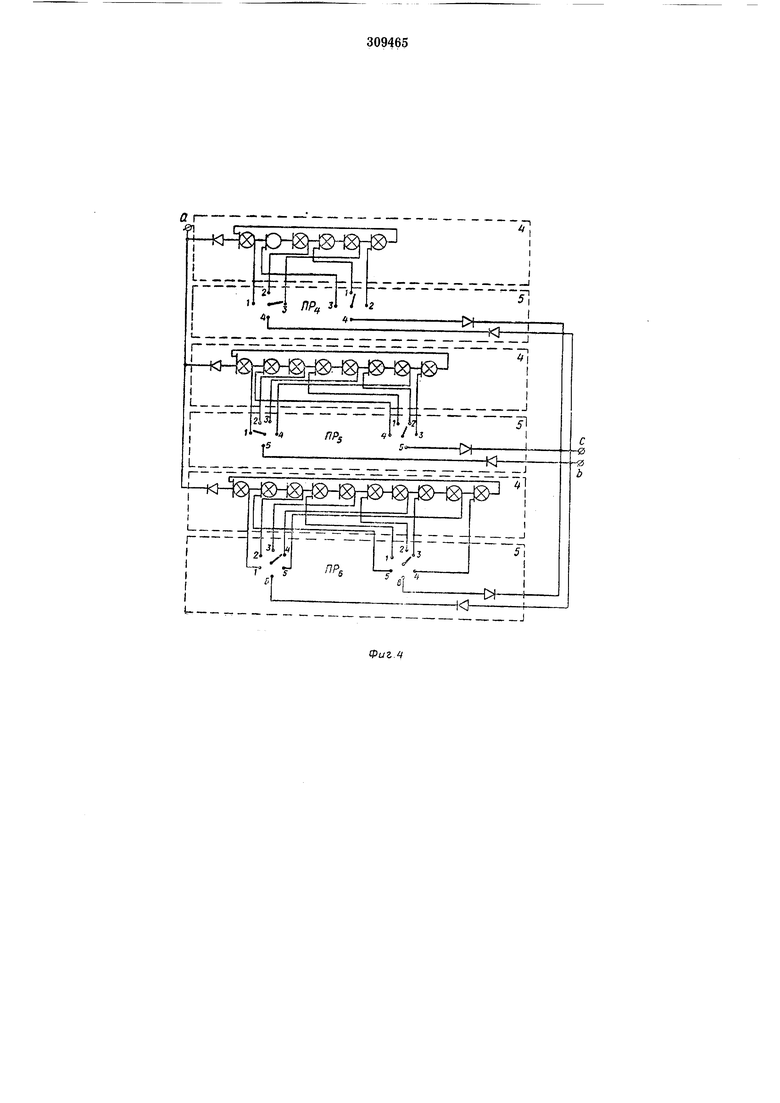

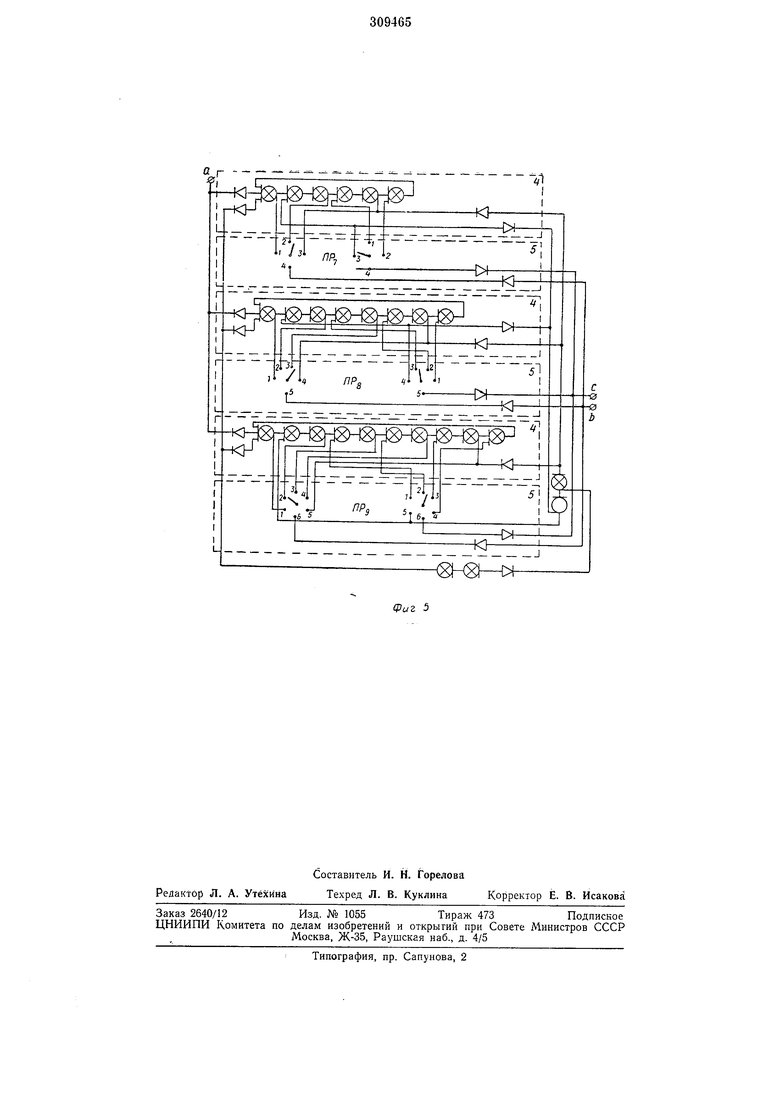

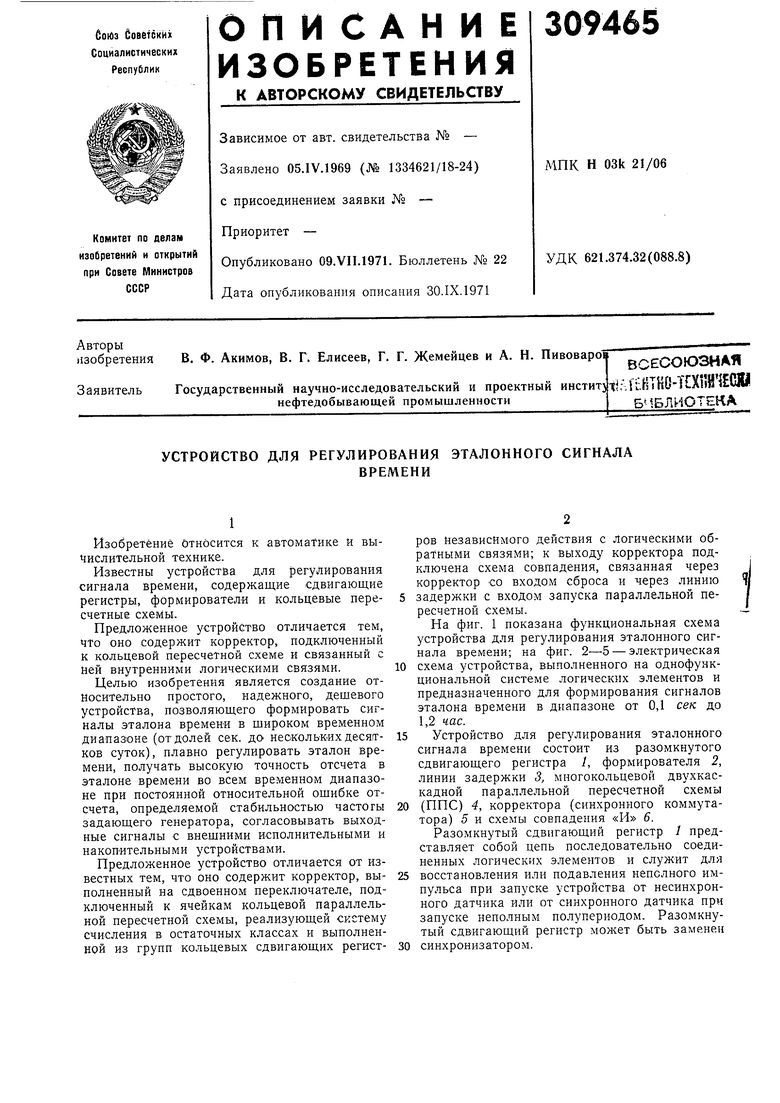

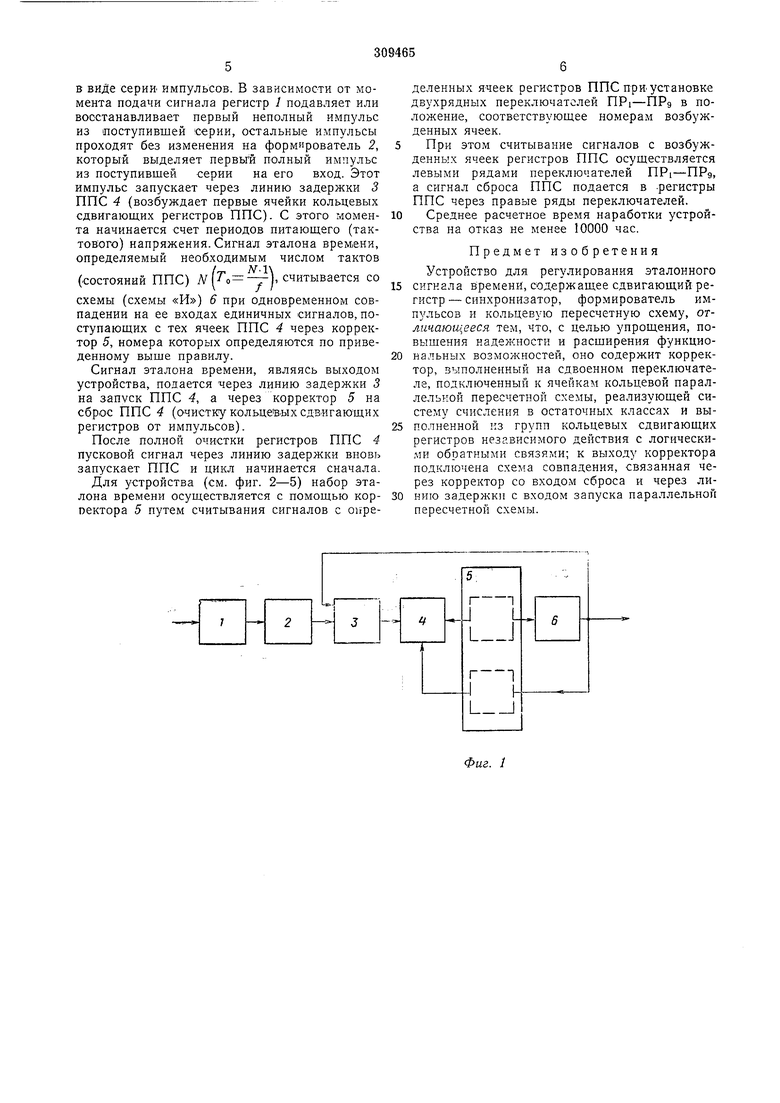

На фиг. 1 показана функциональная схема устройства для регулирования эталонного сигнала времени; на фиг. 2-5 - электрическая

схема устройства, выполненного на однофункциональной системе логических элементов и предназначенного для формирования сигналов эталона времени в диапазоне от 0,1 сек до 1,2 час.

Устройство для регулирования эталонного сигнала времени состоит из разомкнутого сдвигающего регистра }, формирователя 2, линии задержки 3, многокольцевой двухкаскадной параллельной пересчетной схемы

(ППС) 4, корректора (синхронного коммутатора) 5 и схемы совпадения «И 6.

Разомкнутый сдвигающий регистр / представляет собой цепь последовательно соединенных логических элементов и служит для

восстановления или подавления неполного импульса при запуске устройства от несинхронного датчика или от синхронного датчика при запуске неполным полупериодом. Разомкнутый сдвигающий регистр быть заменен Формирователь 2 служит для преобразования произвольной серии импульсов напряжения в момент зануска в одиночный однополупериодный импульс. Линия задержки 3 необходима для задержки сигналов, поступающих на запуск параллельной пересчетной схемы (ППС). Линия задержки осуществляет задержку запускающих сигналов на число тактов (периодов), необходимьгх для полного сброса (очистки) ППС, чтобы исй лючить возможность появленик ложных импульсов в кольцевых регистрах ППС или прекращения счета (сбоя) ППС. Многокольцевая двухкаскадная параллельная пересч«гдач; .схема (ППС) , представляющая собой совокупность кольцевых сдвигающих регистров с логическими обратными связями, реализует систему счисления в остаточных..-Класс.ах. и. подклассах, основанную на неремножении попарно взаимно простых чисел. Максимальная емкость счета ППС равна произведению классов. Н-апример, для ППС (см. фиг. 3-5), состоя:Шей из системы.. кольцевых регистров (подMaccoB.«i; «2; «з), соответственно на 3-5 ячеек4й1 3,,/гз-5), классы (Ki; Kz; Кз) можно представить как подсистемы, состоящие из трех кольцевых сдвигающих регистров (подклассов)./;;;.: г .) Подклассами ni 3, , можно образовать следующие классы (фиг. 3, 4, 5): 1-3X4X5-1 59, /С2 ЗХ4Х5 60, з -ЗХ4Х5+1 61, прячем ,каКклассы. (, 60, ), та1,.и ггрдклассы; (,.,, ) суть цоП-.арно взадашо-простые, числа. ,Максимальная ;емкость счета Стах ППС олр-ел еляется. произведением-,- классов С,,59X60X61 215940. . .Корректгор 5-ос;уще :твляет задание масштаба,, времени и .предста вляет собой синхронный коммутатор,.подключающий цепи считывания С.ППС сигнала эталона времени к цепи сброса, ППС. . .;; ; ,:, :. , ,, .. . .;-Схема со.Бпаденяя-,-схема И 6 выдает сигнал эталона времени только при условии совпадецц врех;;Прстуц;а:Ющих единичных сигналрв-,на. ее вхрдаХ; от ка: кдого кольцевого сдвигакзщего,-регистра: ППС. . Этал.он времени 7 о можно .выделить .с дискретностью.; в один перй.ад -пита1ющр.го- (тактового).напряжения зад ющег-о генераторами определить.:ПО формуле ...,,.. . .:,:;г.:п..я±:,.;.:,:. где.,л/ -ЧИ.СЛО,тактов,...... . . ,,. .fn.-.4.acTora. ,питающего... (тактового) на ,.пряжения. . - , ., ..,...: ,.Для, опр-еделения. номеров Лп.ц ::ВОзбужденных:Ч-чеек1 крл,ьцевых сдвигающих регистров ППС, : ,КОТ,ррЫХ.. производится- eчитывaниe т. е. требуемого эталона времени TQ N-, не обходимо определить минимальные положительные вычеты unikj по модулям подклассов ftj от минимальных положительных вычетов Kkj по модулям K.J соответствующих классов . /Сй(modл,-); A(modAy); ,;„ „ -номер возбужденной ячейки кольцевого сдвигающего регистра П; ячеек (подкласс «г), входящего в класс /Cj. Для ППС (см. фиг. 3-5) п принимает значения из множества 3, 4,5 («г 3, , 3 5) и лз множества 59, 60, 61 Ki 59, К2 60, Кз 61). В качестве пояснения приводится пример определения номеров возбужденных ячеек кольцевых сдвигающих регистров ППС при считывании произвольного числа тактов (состояния) ППС, например, (так как при считывании сигнала времени масщтаба То 2403 Класс Ki 59 Кк, 2403 (mod 59), т. е. Кл-. 43 (mod 59), КА-, 43. Номер возбужденной ячейки , кольцевого сдвигающего регистра ППС на «1 3 ячеек, входящего в класс /Ci 59, определится как йпА 43 (mod 3) или «лл 1 (mod 3), в кольцевом сдвигающем регистре ППС на «1 3 ячеек будет возбуждена первая ячейка. Аналогично определяются номера возбужденных ячеек кольцевых сдвигающих регистров ППС на «2 4 и «3 5 ячеек: an,k, 43 (mod 4)3 (mod 4), , 43 (mod 5)3 (mod 5). Класс К2 60 КА-, 2403 (mod 60), Кл 3 (mod 60), КА-, 3 Аналогично определяются а„,й, 3 (mod 3)0 (mod 3), fln,ft 3 (mod 4); an,k, 3 (mod 5). Класс Kj 61 Кл-з S32403 (mod 61), K/f, 24 (mod 61), Кл-з 24 Аналогично определяются о„,-н24 (mod 3)0 (mod 3); a,,,ft 24 (mod 4)0 (mod 4); a,,,k, 24 (mod 5)4 (mod 5). При запуске устройства на вход разомкнутого сдвигающего регистра 1 подается сигнал Минимальным положительным вычетом чисяа Л

в виде сериИ импульсов. В зависимости от момента подачи сигнала регистр 1 подавляет или воССтанавливает первый пеполный импульс из поступившей серии, остальные импульсы проходят без изменения на формирователь 2, который выделяет первый полный импульс из поступившей серии на его вход. Этот импульс запускает через линию задержки 3 ППС 4 (возбуждает первые ячейки кольцевых сдвигаюших регистров ППС). С этого момента начинается счет периодов питающего (тактового) напряжения. Сигнал эталона времени, определяемый необходимым числом тактов

(состояний ППС) N (7о -, считывается со

схемы (схемы «И) 6 при одновременном совпадении на ее входах единичных сигналов, поступающих с тех ячеек ППС 4 через корректор 5, номера которых определяются по приведенному выше правилу.

Сигнал эталона времени, являясь выходом устройства, подается через линию задержки 3 на запуск ППС 4, а через корректор 5 на сброс ППС 4 (очистку кольце1вых сдв-игающих регистров от импульсов).

После полной очистки регистров ППС 4 пусковой сигнал через линию задержки вновь запускает ППС и цикл начинается сначала.

Для устройства (см. фиг. 2-5) набор эталона времени осуществляется с помощью корректора 5 путем считывания сигналов с оиределенных ячеек регистров ППС при установке двухрядных переключателей nPi-ПРд в положение, соответствующее номерам возбужденных ячеек.

При этом считывание сигналов с возбужденных ячеек регистров ППС осуществляется левыми рядами переключателей nPi-ПРд, а сигнал сброса ППС подается в -регистры ППС через правые ряды переключателей.

Среднее расчетное время наработки устройства на отказ не менее 10000 час.

Предмет изобретения

Устройство для регулирования эталонного сигнала времени, содержащее сдвигающий регистр - синхронизатор, формирователь импульсов и кольцевую пересчетную схему, отличающееся тем, что, с целью упрощения, повышения надежности и расширения функциональных возможностей, оно содержит корректор, выполненный на сдвоенном переключателе, подключенный к ячейкам кольцевой параллельной пересчетной схемы, реализующей систему счисления в остаточных классах и выполненной из групп кольцевых сдвигающих регистров независимого действия с логическими обратными связями; к выходу корректора подключена схема совпадения, связанная через корректор со входом сброса и через линию задержки с входом запуска параллельной пересчетной схемы.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ИНДИКАЦИИ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ | 1973 |

|

SU363971A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО ВЫБОРА ПРЕДЕЛОВ ИЗМЕРЕНИЯ ЦИФРОВЫХ ПРИБОРОВ | 1969 |

|

SU241539A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

| НЕПРЕРЫВНЫЙ ЦИФРОВОЙ ИНТЕГРАТОР | 1969 |

|

SU241121A1 |

| УСТРОЙСТВО для АНАЛИЗА СЛУЧАЙНЫХ ПРОЦЕССОВ | 1973 |

|

SU378860A1 |

| Распределитель | 1983 |

|

SU1130901A1 |

| АНАЛОГОВЫЙ РЕГИСТР СДВИГА | 1971 |

|

SU305480A1 |

| АНАЛИЗАТОР ДЛЯ КОНТРОЛЯ ХАРАКТЕРИСТИК ДИНАМИЧЕСКИХ СИСТЕМ | 1971 |

|

SU300875A1 |

Фиг. 1

5 s {KH8H8H8 -l --f- IJ 1

; Г

-0a.

-0 Выход

фуг.2

.6

gHSf

Авторы

Даты

1971-01-01—Публикация