Изобретение относится к области антОМатики и вычисл-ительной техники и предназначено для преобразования параллельны.ч двоичных кодов в число-им пульсный код.

Известен преобразователь параллельного двоичного кода в число-импулЕзоный код, содержащий регистр, счетчик, вентили, соединенные с выходами соответствующих разрядов регистра « счетчика, схему «ИЛИ, входы которой соединены с выходами вентилей, дололиительиый /уг-раарядпый счетчи1к., в.чод которого соединен с выходом схемы «ИЛИ, схему «пуск-стон, соединенную через триггер со входом общего счетчика, две схемы «исключающее ИЛИ.

Предложе 1иое устройство отличается тем, что общ11й счетчик содержит т дополнительных разрядов, причем выходы всех разрядов общего счетчика и схемы «ИЛИ соединены со .входами первой схемы «исключающее ИЛИ, выход которой соединен с первым входом сброса триггера, выходы дополнительного счетчика через вторую схему «исключающее ИЛИ соединены со вто-рым входом сброса того же триггера, а выход сигнала иереполнепня общего счетчика соединен со входами сброса регистра и схемы «пуск-стоп.

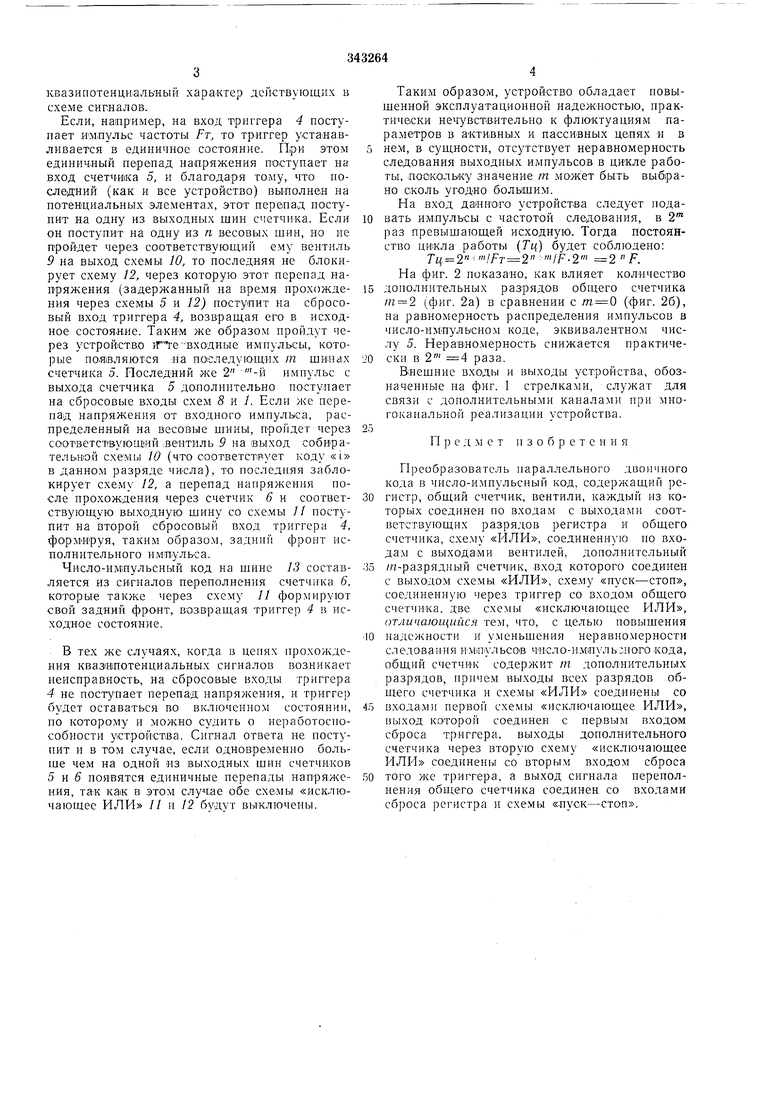

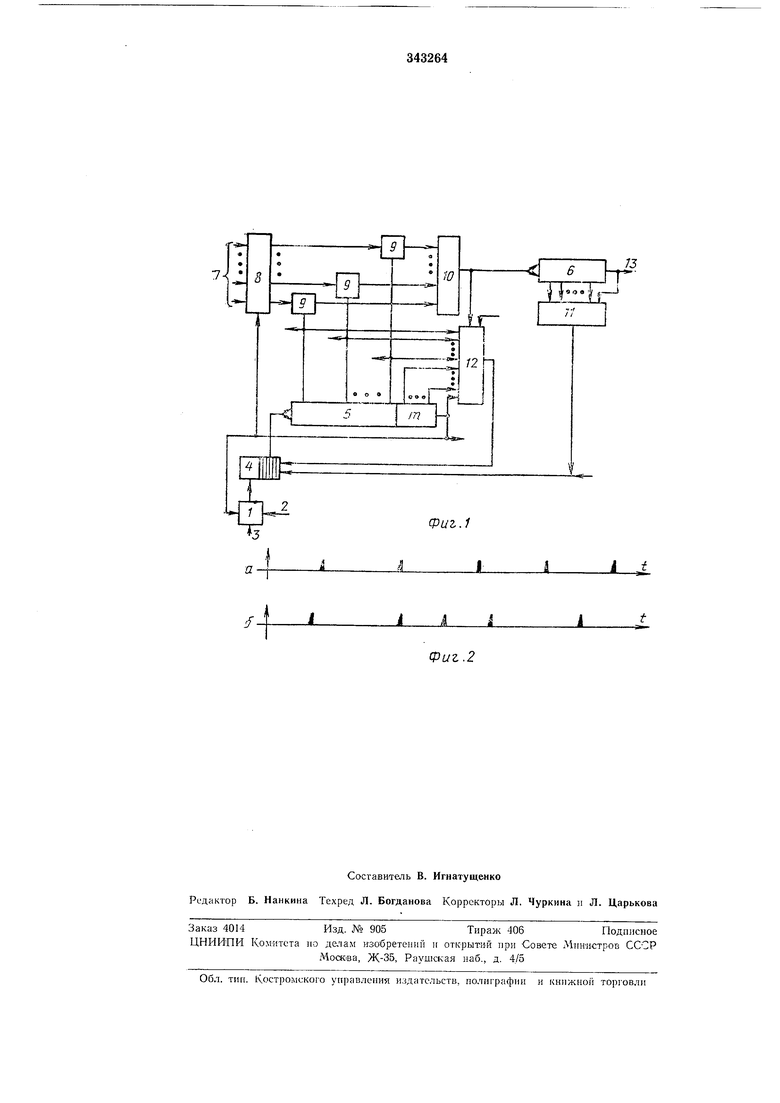

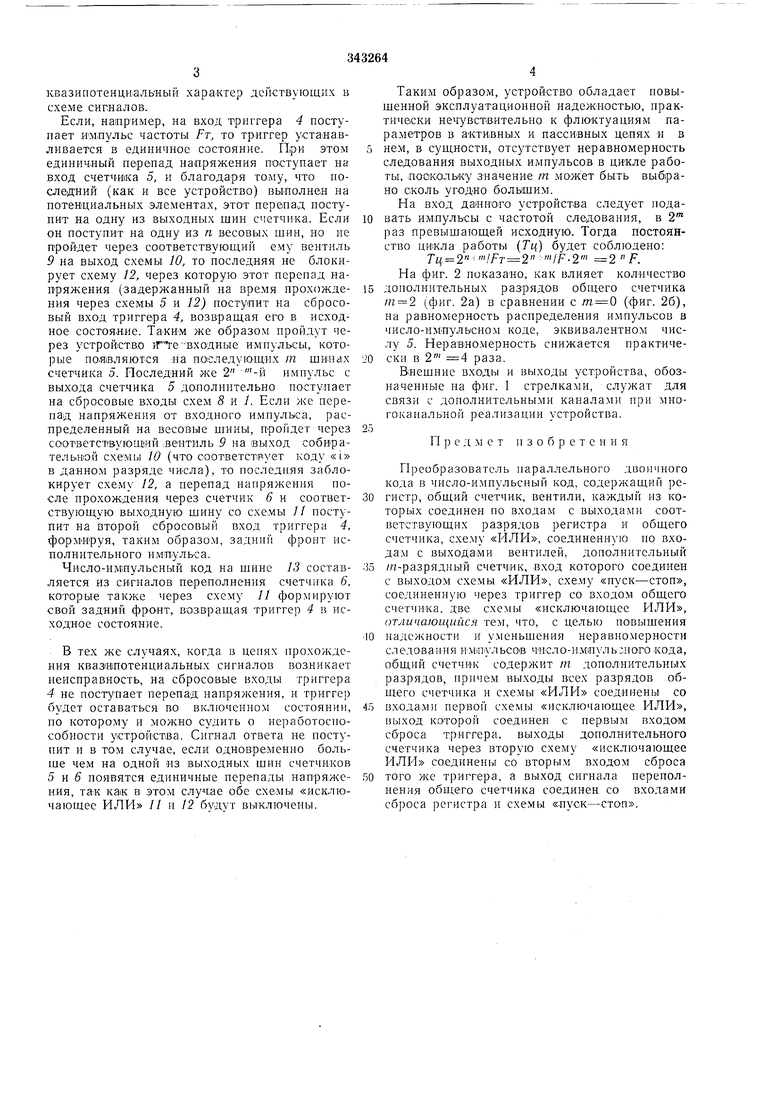

На фиг. 1 изображена схема }стройства; на фиг. 2 - диаграммы распределения импульсов выходиого кода г зависи-.мости от ni.

Устройство содержит (фиг. I) схе 1у«иуск- стоп / триггериого типа с шинами сигнала «пуск 2 и тактово частоты 3, триггер 4, общий счетчи к 5 иа (л+ш) разрядов, дололнительпый /7 -:разрядный счетчик 6, входные шины 7 па;раллельного двоичного кода, регистр 8, веитили 9. схему «ИЛИ W, схемы «исключающее ИЛИ // и 12, выход /-.

Устройство работает следующим образом.

После записи двоичного кода в регистр 8

ио шиме 2 включается схема «пуск-стоп 1, через которую с шины 3 иа триггер 4 поступают им;пульсы тактовой частоты F/-.3a цикл работы счетчика 5, равный Г,, 2 FT, на калодый ,из п вентилей 9 поступит 2 взвеи1е ь

ных по двоичному закону сериГ импульсов, распределенных по циклу, равному 2 Гт. Эти серии логически умножаются на значения соответствующих им разрядов регистра 8, и частные произведения суммируются на схеме

«ИЛ11 JO. С выхода последней с помощью счетчика 6 суммарная последовательность импульсов делится иа в результате чего с выходной щины 13 снимается результирующий число-им1пульсный код.

квазипотенциальный характер дснствующпх в схеме сигналов.

Если, наоример, на вход триггера 4 поступает импульс частоты FT, то триггер уста навливается в единичное состояние. При этом единичный перепад нааряжения поступает на вход счетчи1ка 5, и благодаря тому, что последний (как и все устройство) выполнен на потенциальных элементах, этот перепад поступит на одну из выходных шин счетчика. Если он подступят на одну из п весовых шин, но не пройдет через соответствующий ему вентиль 9 на выход схемы 10, то последняя не блокирует схему 12, через которую этот перепад напряжения (задержанный на время прохождения через схемы 5 и 12) поступит на сбросовый вход триггера 4, возвращая его в исходное состояние. Таким же образом пройдут через устройство }Г ге Входные импульсы, которые появляются :на последующих /п счетчика о. Последний же 2 импульс с выхода счетчика 5 дололнительно поступает на сбросовые входы схем 8 и /. Если же перепад напряжения от входного импульса, расвределеЕный на весовые шины, пройдет через соответствующий ;вентиль 9 на выход собирательной схемы 10 (что соответструет коду «t в данном разряде числа), то последняя заблокирует схему 12, а перепад напряжения после прохождения через счетчик 6 и соответствующую выходную шину со схемы // поступит на второй сбросовый вход триггера 4, формируя, таким образом, задний фронт исполнительного импульса.

Число-импульсный код на шине 13 составляется из сигналов переполнения счетчика 6, которые также через схему И формируют свой задний фронт, воз:вращая триггер 4 в исходное состояние.

В тех же случаях, когда в цепях прохождения квазипотенциальных сигналов возникает неисправность, на сбросовые входы триггера

4не поступает перепад напряжения, и триггер будет оставаться во включенном состоянии, по которому и можно судить о неработоспособности устройства. Сигнал ответа не поступит и в том случае, если одновременно больше чем на одной из выходных шин счетчиков

5и 5 появятся единичные перепады напряжения, так KaiK в этом слу-чае обе схемы «исключающее ИЛИ // и 12 будут выключены.

Таким образом, устройство обладает новышенной эксплуатационной надежностью, практически нечувствительио к флюктуациям параметров в активных и пассивных цепях н в нем, в сущности, отсутствует неравномерность следования выходиых импульсов в цикле работы, поскольку значение т может быть выбрано сколь угодно большим.

На в.ход данного устройства следует подавать импульсы с частотой следования, в 2 раз превышающей исходную. Тогда постоянство цикла работы {Тц} будет соблюдено:

Тц 2 ЧF2 2 F. На фиг. 2 показано, как влияет количество дополнительных разрядов общего счетчика т 2 (фиг. 2а) в сравнении с т 0 (фиг. 26), на равномерность распределения импульсов в число-импульсиом коде, эквивалентном числу 5. Неравномерность снижается практически в 4 раза.

Внешние входы и выходы устройства, обозначенные на фиг. 1 стрелками, служат для связи с дополнительными каналами при многоканальной реализации устройства.

Предмет и з о б р е т е и и я

Преобразователь параллельного двоичного кода в число-импульсный код, содержащий регистр, общий счетчик, вентили, каждый из которых соединен по входам с выходами соответствующих разрядов регистра и общего счетчика, схему «ИЛИ, соединениую но входам с выхода ми веитилей, дополнительный

/«-разрядный счетчик, вход которого соединен с выходом схемы «ИЛИ, схе.му «пуск-стоп, соединенную через триггер со входом общего счетчика, две схемы «исключающее ИЛИ, отличающийся тем, что, с целью повышения

надежности и уменьшения неравномерности следова11ия им1пульсо1В Число-ил 1пуль:ис1 гокода, общий счетчи1ч содержит /и дополнительных разрядов, нричем выходы всех разрядов общего счетчика и схемы «ИЛИ соединены со

входами первой схемы «искл Очающее ИЛИ, выход которой соединен с первым входом сброса триггера, выходы дополнительного счетчика через вторую схему «исключающее ИЛИ соединены со вторым входом сброса

того же триггера, а выход сигнала переполнения общего счетчика соединен со входами сброса регистра и схемы «пуск-стоп.

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО ДВОИЧНО-п-ИЧНОГО КОДА | 1973 |

|

SU387360A1 |

| МАСШТАБИРУЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU360661A1 |

| Задающее устройство для цифрового следящего привода | 1985 |

|

SU1325412A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2014 |

|

RU2570116C1 |

| Преобразователь интервалов времени в цифровой код | 1976 |

|

SU665401A1 |

| Преобразователь кодов | 1987 |

|

SU1444957A1 |

| Многоканальный преобразователь частоты в код | 1990 |

|

SU1837396A1 |

| ИНТЕРПОЛИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ВРЕМЯ-КОД | 2008 |

|

RU2385479C2 |

| УСТРОЙСТВО для ИНТЕГРИРОВАНИЯ ФУНКЦИЙ в ДВОИЧНО-ДЕСЯТИЧНОМ ЦИКЛИЧЕСКОМ КОДЕ | 1967 |

|

SU203321A1 |

| Устройство для контроля модулей коммутации | 1984 |

|

SU1273931A1 |

Авторы

Даты

1972-01-01—Публикация