Изобретение относится к Области вычислительной техники.

Известные устройства сравнения, содержащие две пираМидальные схемы «ИЛИ и я однотипных, Соединенных последовательно, ячеек сравнения, каждая из которых состоит из трех элементов «НЕ-ИЛИ, сложны и имеют недостаточную надежность и быстродействие.

В предлагаемом устройстве с целью упрощения и повышения его надежности и быстродействия, элементы в жаясдой ячейке соединены таК, что выход первого элемента «НЕ- ИЛИ соединен со входом двух других элементов «НЕ-ИЛИ, .причем входная щина первого числа соединена со входами первого и второго элементов «НЕ-ИЛИ, а входная шина второго числа соединена со входами первого и третьего элементов «НЕ-ИЛИ, выходы второго и третьего элементов «НЕ- ИЛИ соединены со входами пирамидальных схем «ИЛИ, выходы которых соединены с третьими входами второго и третьего элемента «НЕ-ИЛИ следующего разряда.

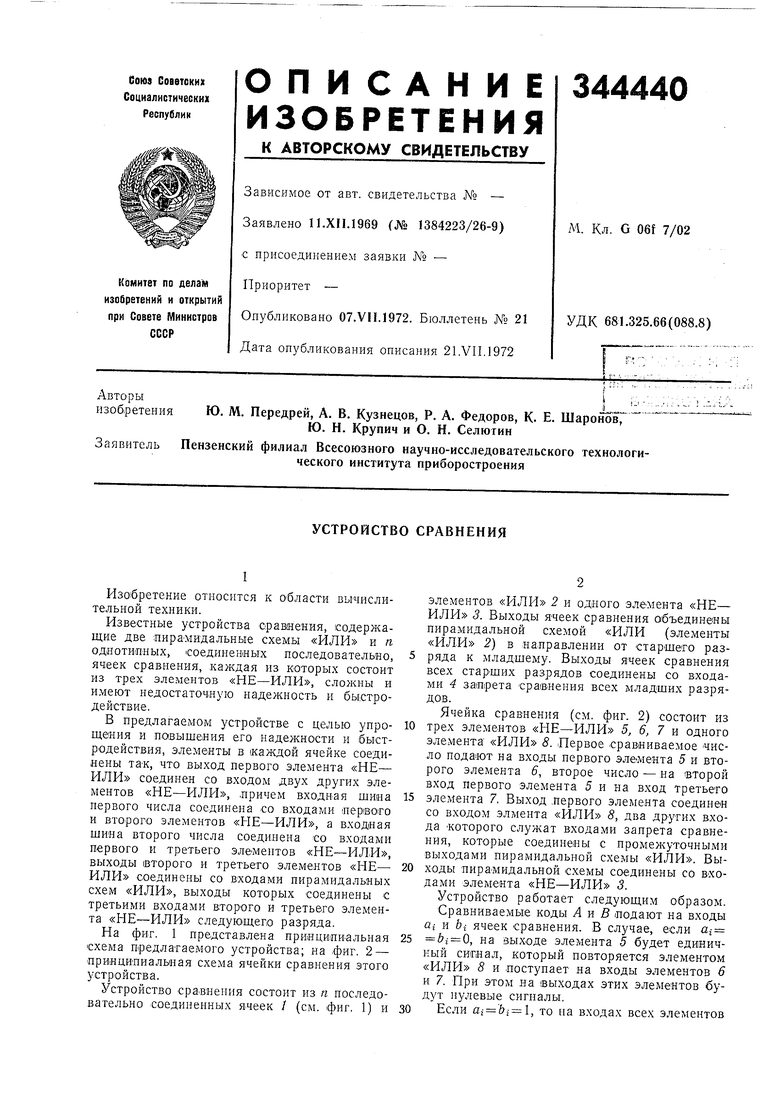

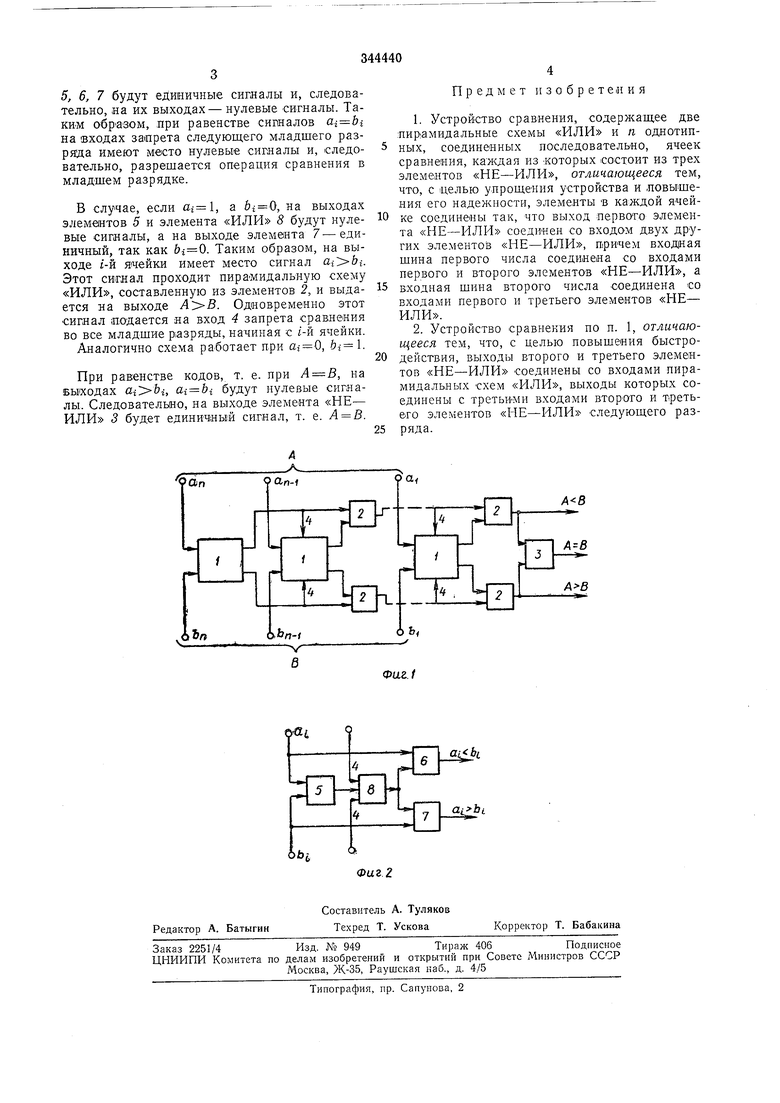

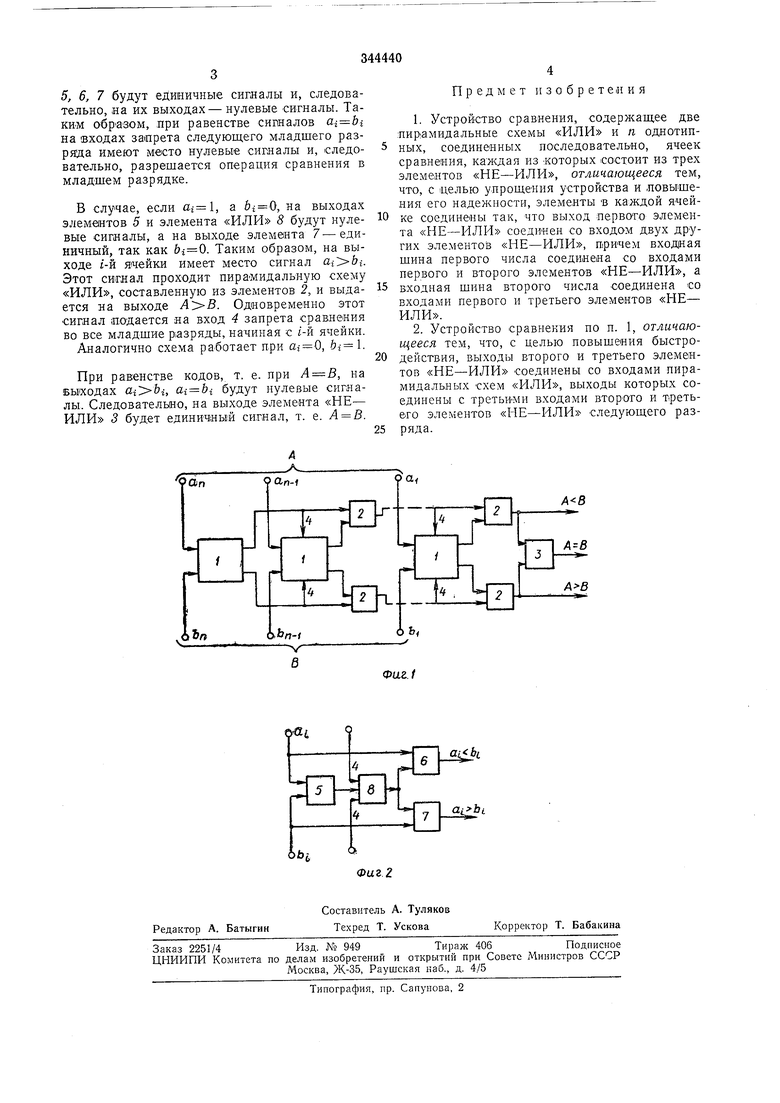

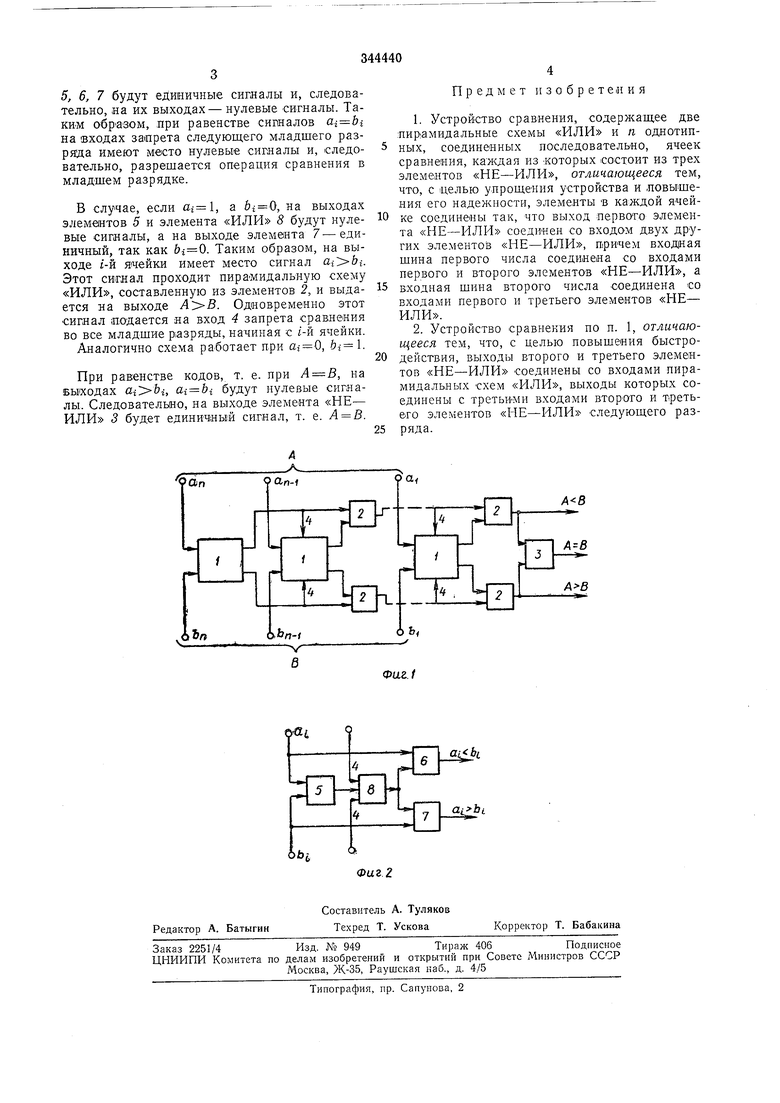

На фиг. 1 представлена принципиальная схема предлагаемого устройства; на фиг. 2 - принципиальная схема ячейки сравнения этого устройства.

элементов «ИЛИ 2 и одного элемента «НЕ- ИЛИ 3. Выходы ячеек сравнения объединены пирамидальной схемой «ИЛИ (элементы «ИЛИ 2) в направлении от старшего разряда к младшему. Выходы ячеек сравнения всех старщих разрядов соединены со входами 4 запрета сравнения всех младших разрядов. Ячейка сравнения (см. фиг. 2) состоит из

трех элементов «НЕ-ИЛИ 5, 6, 7 н одного элемента «ИЛИ 8. Первое сравниваемое число подают на входы первого элемента 5 и второго элемента 6, второе число-на второй вход первого элемента 5 и на вход третьего

элеамента 7. Выход .первого элемента соединен со входом элмента «ИЛИ 8, два других входа Которого служат входами запрета сравнения, которые соединены с промежуточными выходами пирамидальной схемы «ИЛИ. Выходы пирамидальной схемы соединены со входами элемента «НЕ-ИЛИ 3.

Устройство работает следующим образом.

Сравниваемые коды Л и S подают на входы

а, и bi ячеек сравнения. В случае, если ai

bi - 0, на выходе элемента 5 будет единичный сигнал, который повторяется элементом «ИЛИ 8 и .поступает на входы элементов 6 и 7. При этом на выходах этих элементов будут нулевые сигналы. 5, 6, 7 будут единичные сигналы н, следовательно, на их выходах- нулевые сигналы. Таким образом, при равенстве сигналов на входах запрета следующего младшего разряда имеют место нулевые сигналы и, следовательно, разрешается оиерация сравнения в младшем разрядке. В случае, если , а bi-Q, на выходах элементов 5 и элемента «ИЛИ 8 будут нулевые сигналы, а на выходе элемента 7-единичный, так как . Таким образом, на выходе г-й ячейки имеет место сигнал . Этот сигнал проходит пирамидальную схему «ИЛИ, составленную из элементов 2, и выдается на выходе . Одновременно этот сигнал подается на вход 4 запрета сравнения во все младшие р1азряды, начиная с i-й ячейки. Аналогично схема работает п.ри , bi. При равенстве кодов, т. е. при Л В, на выходах , ui - bi будут нулевые сигналы. Следовательно, на выходе элемента «НЕ- ИЛИ 3 будет единичный сигнал, т. е. Л В. Предмет изобретения 1.Устройство сравнения, содержащее две :пир:амидальные схемы «ИЛИ и п однотипных, соединенных последовательно, ячеек сравнения, каждая из «оторых состоит из трех элементов «НЕ-ИЛИ, отличающееся тем, что, с целью упрощения устройства и .повышения его надежности, элементы в каждой ячейке соединены так, что выход первото элемента «НЕ-ИЛИ соединен со входОМ двух других элементов «НЕ-ИЛИ, П ричем входная шина первого числа соединена со входами первого и второго элементов «НЕ-ИЛИ, а входная шина второго числа соединена со входами первого и третьего элементов «НЕ- ИЛИ. 2.Устройство сравнения но п. 1, отличающееся тем, что, с целью повышения быстродействия, выходы второго и третьего элементов «НЕ-ИЛИ соединены со входами пирамидальных схем «ИЛИ, выходы которых соединены с третьими входами второго и третьего элементов «НЕ-ИЛИ следующего разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения двоичных чисел | 1979 |

|

SU898420A1 |

| Распределитель импульсов | 1982 |

|

SU1050105A1 |

| УСТРОЙСТВО для КОНТРОЛЯ ОПЕРАТИВНЫХ НАКОПИТЕЛЕЙ | 1972 |

|

SU341087A1 |

| ДЕКАДНЫЙ СЧЕТЧИК | 1971 |

|

SU320060A1 |

| Устройство для сравнения двоичных чисел | 1977 |

|

SU628486A1 |

| В П Т Б ЧП r^f'n'^f'nTrii т bnOiiiiPiyi | 1973 |

|

SU408303A1 |

| Устройство для сортировки двоичных чисел | 1983 |

|

SU1104504A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СТАРШЕГО РАЗРЯДА РАЗНОСТИ ДВУХ ДВОИЧНЫХ ЧИСЕЛ | 1960 |

|

SU134071A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Логическое запоминающее устройство | 1974 |

|

SU608199A2 |

Авторы

Даты

1972-01-01—Публикация