Изврстно яогическре запоминающее устройство, которое содержит числовые линейки, раз-. рядный и адресный блоки управления, регистр слова, выходной регистр, элементы И 1J.

Однако ограниченные функциональные юзможностн этого устройства не позволяют, например, вести сортировку хранящихся в нем масснвов.

Нанболее близким техническим решением к изобретению является устройство по основному авт. свнд. № 492934, содержащее числовые линейки, разрядные шины которых подклкзчены к выходам разрядного блока управления, линейные шины - к выходам адресного блока . управления, шнны чтения - к входам выходного регистра, выходы которого соединены с входами элементов И первой группы, регистр слова, входы которого подключены к выходам элементов И второй группы, а выходы - к входам разрядного блока управления, управляющие шины, шнны йндикацни, шины начальной установки, блок модификации адреса и блок фор: мирова.ния массивов, входы которого подключены к выходам регистра адреса и блока модифнкацнн адреса, соединенным с входами элейеИтов И второй группы, а выходы - ссютветсгвенно к входам адресного блока управления

и шинам индикации, выходы элементов И первой группы подключены к входам регистра адреса и одним входам блока модификации адреса, другие входы которого соединены соот. ветственно с управдяющими шинами и шннами 5начальной установки (2).

Это логическое, запоминающее .устройство им.еет невысокую достоверность результатов обработки из-за возможности появления катастрофических: отказов в числовых линейках накопи-. JO теля, что может привести к искажению правильного результата обрабоч-ки информации в нако.пителе. .

Целью изобретения является повышение надежности устройства за счет повышения достоверности результатов обработки.. Достигается это благодаря тому, что устройство содержит эл ;менты И и элемент И-НЕ, входы которого подключены к шинам чтения, а выход - к одним из входов элементов И, другие входы элементов И соединены срответQ .ственно с одной из управляющих/шин и управляющими выходами соответствующих ячеек блока формирования массивбв, а выходы элементов И подключены к соответствующим входам ячеек блока формирования массивов.

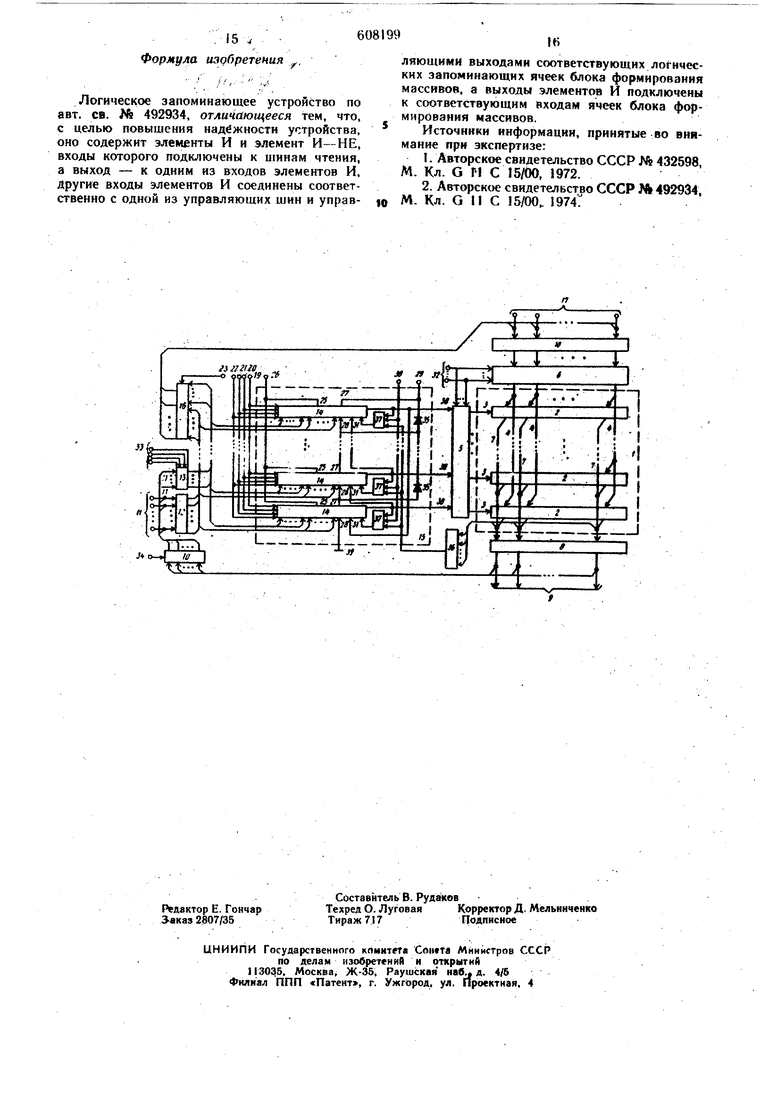

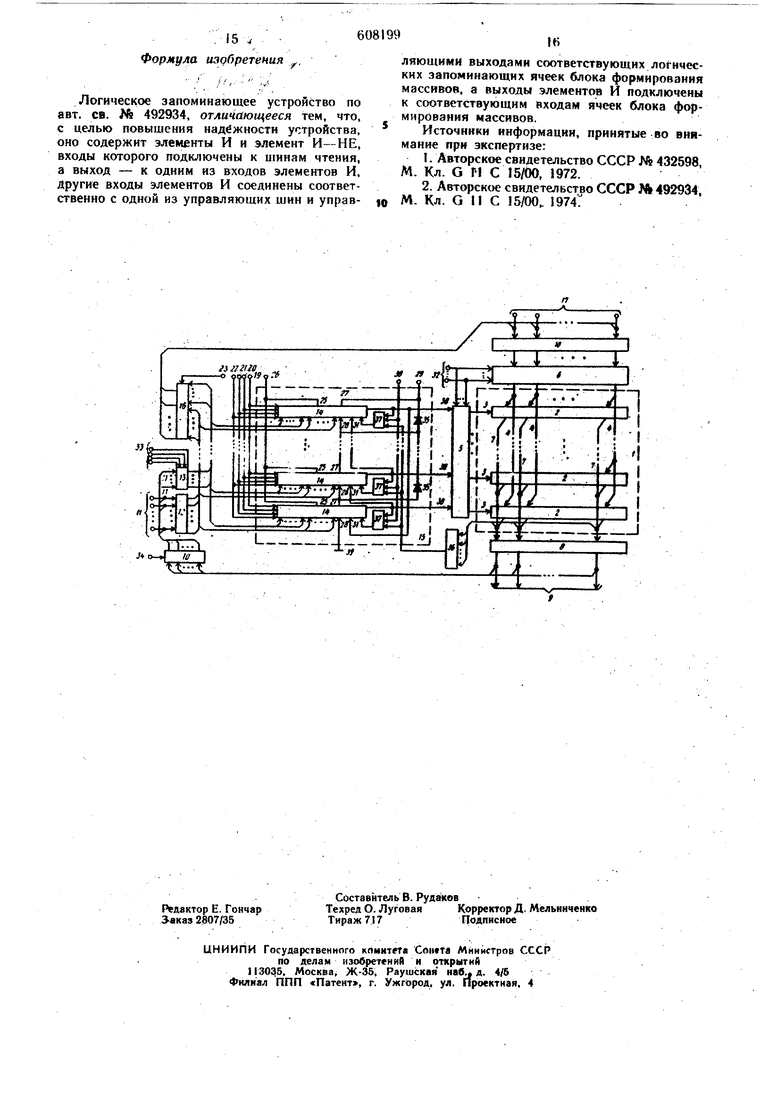

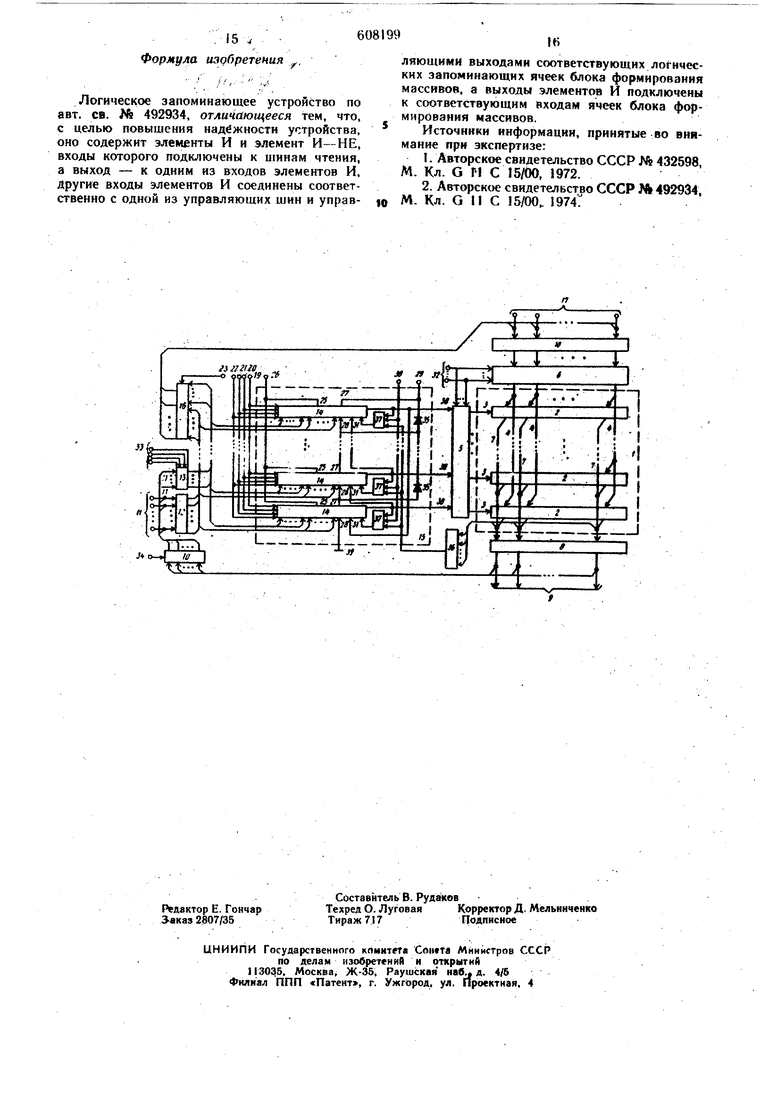

На чертеже изображена блок-схема логи5 ческогс запоминающего уетройстна.

Устройство содержит (шкопитель 1, состоящий из числовых лнисек 2, линейные 3 н разрядные 4 шины которых подключены соответственно к выходам адресного 5 и разрядного 6 блоков управления, а шины чтения 7 соединены с входам выходного регистра 8. Выходные шины 9 выходного регистра 8 соединены через элементы И первой группы 10 с вхОл1ами П регистра адреса 12 и блока модификации адреса 13, выходы которых подключены к функциональным входам логических запоминающих ячеек 14 блока 15 формирования массивов и к входам элементов И второй группы 6.

Выходы элементов И }6 соединены с входными шинами 17 регистра слова 18, выходы которого подключены к входам разрядного блока управления 6.

Управляющие входы ячеек 14 соединены с шимзми управления 19-22, управляющие входы элементов И 16 подключены к шине управления 23, а счетные входы первого и второго разрядов блока 13 соединены с шинами управления 24.

Выход 25 признака модификации каждой ячейки 14 подключен к шине индикации 26.

Выход 27 индикации состояиия первой ячейки 14 блока формирования массивов 15 соединен с входом запрета записи 28 второй ячейки 14. Вход 28 запрети записи каждой последующей ячейки 14 подключен к выходу 27 индикации состояния предыдущей ячейки 14, а выход 27 индикации состояния последней ячейки 14 соединен с шиной 29 индикации состояиия накопителя.

Управляющий выход 30 каждой ячейки 14 блока 15 формирования массивов подключен к соответствующему входу адресного блока управления 5 и, кроме последней, к разрешающему входу 31 последующей ячейки 14, а управляющий выход 30 последней ячейки 14 соединеи с разрешающим входом 31 первой ячейки 14. Кроме того стройство содержит щииы управления 32 адресным 5 и разрядиым 6 блоками управления, щины начальной установки:33 блока 13, шину управления 34 первой группой элементов И 10, Вход 28 заnpiera записи каждой ячейки 14 подключен че.рез раздел 1тельный диод 35 к входу 28 запрета записи предыдущей ячейки 14, а вы3(ОД 27 последней ячейки 14 через разделительный диод 35 - к входу 28 запрета записи згой ячейки.

Входы элемеита И--НЕ 36 соединены с шийамй чтения 7, а выход - с одним из входов .элементов И 37. Вторые входы элементов И 37 подключены к управляющей щиие 38, иа которую подается «Признак контроля. Третьи входы элементов И 37 соединены с управляющими выходами 30 ячеек 14, Входы запи0 едймицы в младший разряд ячеек 14 подключены к выходам элементов И 37, . .

Предложенное логическое запоминающее устройство имеет три режима работы: режим записи массивов информации, режим логической обработки Массивов информации и режим «e w ratnt «мюйвтела..

Каждому массиву информации присваивается признак, называемый начальным адресом/ массива. Запись массивов ииформа И И производится в незанятые к моменту записи числоJ вые линейки 2 накопителя I, причем необязательно следующие друг за другом. Часть массива, записанная в следующих по порядку числовых линейках 2, называется подмассивом данного массива информации. Каждому подиассиву присваивается соответствующий приз0 нак„ называемы текущим адресом массива, iifve craRffHsoiJtiHS собой ()-paзpядный код, в котором, k старших разрядов образованы полем начального адреса массива, а I младших разрядов - полем константы модификации, являющейся порядковым номером подмассива

в данном массиве информации.

Текущий адрес, соответствующий каждому последующему подмассиву некоторого массива информации уве,яичивается на единицу младшего разряда по сравнению с текущим адресом предыдущего подмассива.

Будем считать, что в режиме записи различиые массивы информации могут поступать от периферийных устройств (иа чертеже не показаны) по частям, причем, отдельные части одного и того же массива могут следовать через произвольные промежутки времени, в течение которых устройство может производить запись отдельных частей других массивов информации.

Для организации правильной очередиости

0 подмассивов каждого массива ииформации после окончания записи отдельной части массива текущий адрес увеличивается на единицу младшего разряда и хранится в одной из числовых линеек 2 накопителя 1 до поступления очередной части этого массива информации.

5 При поступлении от периферийиых устройств очередной части некоторого массива информации в накопителе I производится выборка и считывание текущего адреса этОго массива. При этом логическое запоминающее устройство работает во вспомогательном режиме - в режиме обращения к текущему адресу. Выборка требуемой числовой линейки 2 в накопителе I производится по признаку. Числовые линейки 2, в которых записаны слова одного и того же подмассива, имеют одинаковый признак, представляющий собой текущий адрес, соответствующий этому подмассиву. При знак каждой числовой линейки 2 хранится в ячейке 14, соответствующей этой числовой лИ нейке..,

Общее число разрядов каждой ячейки 14 ра вно (ic+l-f2), в (k-ft-f I) старщнх разрядах xpaiwfc признаки соответствующих числовых линеек 2, а младший разряд используется для хранения признака работоспособности соответ5 епвующей числовой линейки 2 (нулевое; значение признака С1ЮТветствует исправной чнсловой лйнейке 2, единичное -- числовой линейке 2, имеющей катастрофический отказ).

Числовая линейка 2 считается выбранной, если код текущего адреса массива,, фор мируемый в регистре адреса 12 н в блоке 13,

совпадает с колом, хранящимся в ячейке 14, соответствующей этой числовой линейке 2.

Признак числовой линейки 2. в котором хранится код текущего адреса массива, представляет собой (k + t-f 1) - разрядное двоичное число, в k старших разрядах которого записан код начального адреса массива, а в младшем разряде записана единица, если в этой числовой линейке 2 хранится код текущего адреса записи массива информации, или же в младшем разряде записан нуль, если в этой числовой линейке хранится код текущего адреса обработки массива информации. В остальных разрядах этого двоичного числа записаны нули.

Коды признаков тех числовых линеек 2, в которых хранятся коды текущих адресов массивов, формируются в регистре адреса 12 и блоке 13. Поэтому общая длина разрядной сетки регистра адреса 12 и блока 13 составляет k + f-f 1 разрядов, k + l старших разрядов используются для формирования текущих адресов массивов, а младший разряд используется только при формировании кодов признаков числовых лииеек 2, в которых хранятся коды текущих адресов массивов.

Считаем, что код, поступающий от регистра адреса 12 и блока 13 в ячейки 14, представляет собой (k + t + 2) - разрядный код, (lt-1-f-fl) старщие разряды которого формируются в регистре адреса 12 и блоке 13 , а в младщем разряде содержится нуль.

При подобной кодировке код, поступающий от регистра адреса 12 и блока 13 в ячейки 14, может совпасть только с кодом, содержащимся в ячейке 14, соответствующей исправной числовой линейке 2, так как в млад щем разряде ячейки 14 соответствующей неисправной числовой линейке 2, записана единица.

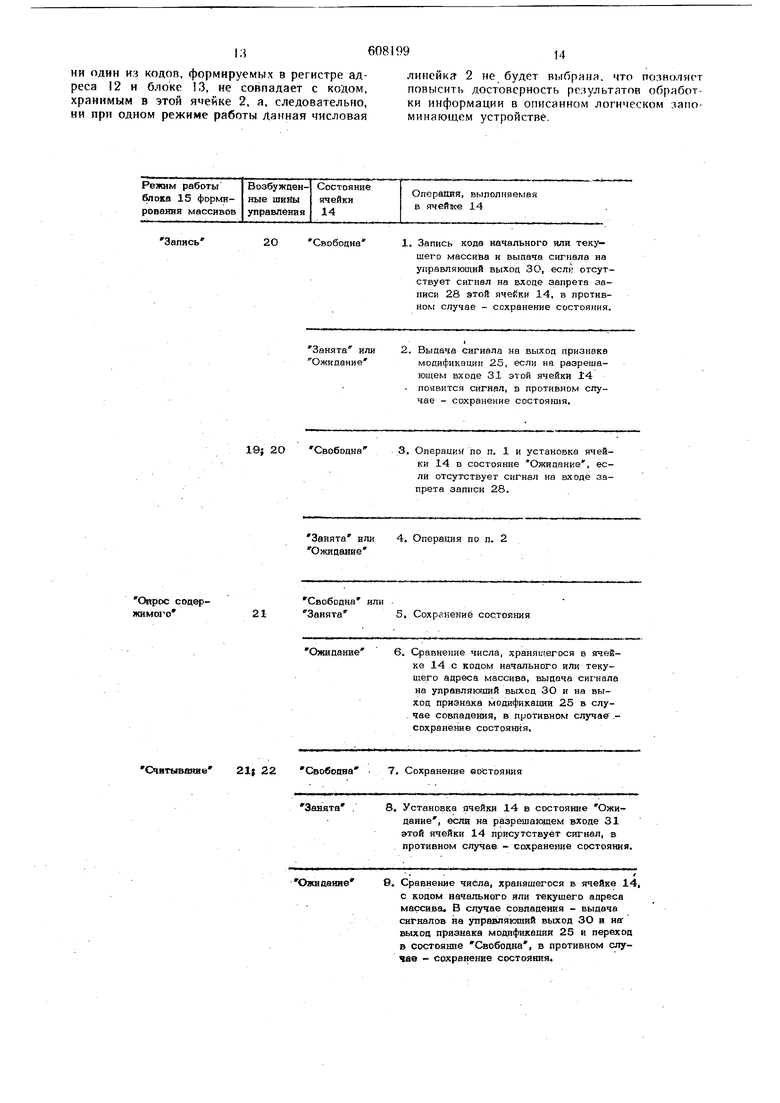

Для упрощения описания работы логического запоминающего устройства, рассмотрим отдельно логику работы ячеек 14 блока 15 формирования массивов, отраженнуй} в таблице.

Блок 15 формирования массивов может работать в трех режимах: «Запись, «Считывание н «Опрос содержимого, а каждая ячейка 14 мЬжет находиться, в трех состояниях: «Занята, «Свободна и «Ожидание.

При состоянии «Занята в ячейке 14 записано отличное от нуля число, при, состоянии «Свободна записан нуль, при состоянии «Ожидание записано отличное от нуля число и данная ячейка 14 способна к. возбуждению, если при работе блока 15 формирования массивов в режимах «Считывание и «Опрос содержимого код текущего адреса массива совпадает с кодом числа, хранящегося в ячей ке 14.

. Операдии, выполняемые в ячейке 14 при различных режимах работы блока 15 формиррвания массивов, приведены в таблице.

Сигал на выходке 27 иидикации состояния любой из ячеек 14 присутствует в .том случае, если ячейка 14 находится в состоянии «Свободна.

Перед началом работы в логическом запоминающем устройстве для всех массивов формируются исходные текущие адреса записи массивов и исходные текущие адреса обработки массивов. Формирование исходных текущих адресов записи и обработки массивов происходит следующим образом. Перед началом работы все ячейки 14, регистр адреса 12 и блок 13 устанавливаются в нулевое состояние.

В первогм такте на входы 11 регистра адреO са 12 от периферийных устройств поступает код начального адреса массива и заносится в регистр адреса 12, а по щинам управления 24 во второй разряд блока 13 записывается единица.

Во втором такте на шину управления 23

поступает сигнал, переключающий вторую группу элементов И 16 в проводящее состояние и . исходный текущий адрес записи или обработки массива, сформированный в регистре адреса 12 и блоке 13, заносится в регистр слова 18.

0 В третьем такте по шинам 33 производится сброс в нуль содержимого блока 13, если формируется исходный текущий адрес обработки массива, либо сброс в нуль с записью единицы в первый разряд блока 13, если формируется исходный текущий адрес записи мас5 сива.

В четвёртом такте на щины управления 19 и 20 поступают сигналы, которые настраивают одиу из ячеек 14, находящихся в состояниях «Свободна, на запиА начального адреса за. писи либо начального адреса обработки, сформированного в предыдущем такте в регистре адреса 12 ив блоке 13. ЕСЛИ в состоянии «Свободна находится несколько ячеек 14, то записать код начального или текущего адреса сможет только ячейка 14 с наименьшим

5 порядковым номером. Подобная зависимость обеспбчи1зается логикой работы ячеек 14 (см. таблицу, и. 1) и системой подключения выходов индикации состояния 27 и входов запрета записи 28. Например, если все ячейки 14 окажутся в состояниях «Свободны, то произвести запись сможет только первая ячейка 14, так как только на ее вход запрета записи 28, подключенный к шине нулевого потенциала 39 не будет поступать сигнал запрета.

5 В этом же такте подаются сигналы на шины управления 32, настраивающие адресный 5 и разрядный б блоки управления на организацию записи содержимого регистра слова 18 в эдсловую лииейку 2, соответствующую возбужденному управляющему выходу 30. .

В результате, в одной из ячеек 14 будет записан код начального адреса записи или рбработки. Эта ячейка 14 перейдет в состояние «Ожидание, а в соответствующей числовой линейке 2 будет записан код исходного текуще5 го адреса записи или обработки.

В режиме обращения к текущему адресу работа логического запоминающего устройстна происходит следующим образом.

В первом такте на входы II регнстра адреса 12 подается код начального адреса массива

Р и заносится в регистр адреса 12, а блок 13 76 сигналами, поступающими no шннам 33 начальной установки либо устанавливается в нуль, если производится обращение к текущему адресу обработки, либо устанавливается в нуль с записью единицы в первый разряд, если производится обращение к текущему адресу записи. В результате, в регистре адреса 12 и в блоке 13 будбг сформирован начальный адрес обработки или записи. Во втором такте на щину управления 21 поступает сигнал, по которому в ячейках 14, находящихся в состояниях «Ожидание, производифся операция по п. 6 (см. табл.). В этом же такте на шины управления 32 подаются сигналы, производящие настройку адресного 5 и разрядного 6 блоков управления, организующих считывание текущего адреса записи или обработки из числовой линейки 2, соответствующей возбужденному выходу 30, то есть управляющему выходу 30 той ячейки 14,. .содержимое которой совпало с начальным адресом записи или обработки. Резуль- ат считывания поступает в в з5ходной регистр 8. На этом заканчивается работа устройства в режиме обращения к текущему адресу. Работа логического запоминающего устройства в режиме записи массивов информации. Допустим,что I накопителе 1 перед началом записи имеются числовые линейки 2, хранящие записанную ранее информацию (будем называть эти числовые линейки 2 занятыми) и, что йчейки 14, соответствующие занятым числовым линейкам 2, находятся в состояниях «Заняты либо «Ожидание, остальные ячейки 14 находятся в состояниях «Свободны. При работе устрЪйства в режиме записи массивов информации имеют место три цикла функционирования устройства: начальный цикл, текущий цикл и конечный цикл. Рассмотрим начальный цикл функционирования устройства-. В первом такте на шину управления 34 поступает сигнал, разрещающий работу перёой группы элементов И 10. В этом же такте по входным шинам 17 в регистр слова 18 поступает первое слово подмассива записываемой информации, а по входам-1 1 подключенным через открытые элементы И Ш к выходным шинам 9, в регистр адреса 12 и а блок 13 поступает считанный с выходноГО: регистра 8 код, текуш его адреса записи, занесенный в выходной регистр 8 nj окончании работы устройства в режиме обращения к текущему адресу. Во втором такте на шины управления 19 и 20 подаются сигналы, в. соответствие с которыми в той ячейке 14, из чнсла находящихся в состояниях «Свободны, которая имеет наименьший порядковый номер, вь1полнится операция по п. 3 (см. табл.). В том же такте на ипяы управления 32 Поступают сигналы, настраивающие адресный 5 и разрядный 6 блоки управления на выполнение операции затаен содержимого регистра слова 18 в числовую линейку 2, соответствующую возбужденному управляющему выходу 30. Сигнал с в)збужденного управляющего выхода 30 поступает также на разрещающий в.ход 31 последующей ячейки 14, в которой выпо.пиястся операция но П; 4, если эта ячейка 14 находилась в состоянии «Занята или «Ожидание. Если же последующая ячейка 14 находилась в состоянии «Свободна, то она сохранит свое состояние, так как сигнал на ее входе запрета записи 28, подключённом к выходу ииднкации состояния 27 ячейки 14, записавщей код текущего адреса записи, исчезнет только по окончании второго такта. Результатом иачального цикла является запись первого слова записываемого подмассива информации в; одну из числовых линеек 2, запись текущего адреса записи массива в соответствующую этой числовой линейке 2 ячейку 14, установка этой ячейки 14 в состояние «Ожидание и формирование. 1Г& шнне индикации 26 сигнала в случае, если последующая ячейка 14 находится в состоянии «Занята или «Ожидание, За начальным циклом функционирования устройства в режиме записи следуют текущие циклы по числу оставшихся слов в записываемом подмассиве. Работа устройства в текущем цикле осуществляется следующим образом. В первом такте по входным щинам 17 в регистр слова 18 заносится очередное слово записываемого подмассива, а по шинам упрап.пення 24 на счетный вход второго разряда блока 13 поступает сигнал, увеличивающий текущий адрес записи на единнцу второго разряда, если в последнем такте предыдущего начального или текущего цикла был сформирован сигнал на шине нндикации 26, в противном случае, текущий адрес записи останется без изменения. В этом же такте на шину улравления21 подае1-ся сигнал, переводящий блок формирования массивов 15 в режим «Опрос содержимо го, и в ячейках 14 выполняются операции по пи. 5 и 6 (см. табл.). Опрос, содержимого ячеек 14 производится для того, чтсУбы выявить возможное совпадение текущих адресов записи одного и того же массива при переполнении блока 13. В этом случае появление сигиала на шияе иидикации 26 говорит о том, что необходимо либо вывести из накопителя I чщсть записываемого массива, либо приступить к его обработке. Второй такт протекает аналогично второму такту начального цикла, если во втором такте предыдущего цикла а шине индикации 26 был сформирован сигнал, в противном случае, во втором такте сигналы подаются не по шинам упразления 19, 20 и 32, а только, по шинам управления 20 и 32. Вследствие чего, в ячейка% 14 будут выполняться операции по пп, t и 2 (см. табл.).., В результате выполнения текущего цикла функционирования устройства в режиме записи . осуществляется запись очередного слова записываемого подмассив а водну из числовых, линеек 2, запись текущего адреса записи массива в соответствующую этой числовой .линейке 2 ячейку 14, перевод этой ячейки 14 в состоя-

ние «Ожидание или «Занята в зависимости от того, был ли сформирован во втором такт предыдущего цикла сигнал на шине индикации 26 или нет, и формирование на шине индика цин 26 сигнала в случае, если последующая ячейка 14 находится в состоянии «Ожидание или «Занята.

После записи последнего слова подмассива следует конечный цикл функционирования устройства в режиме записи.

В первом такте по шинам 24 во второй разряд блока 13 заносится единица, что увеличи| ает текущий адрес записи массива на единицу второго разряда.

Второй, третий и четвертый такты протекают аналогично второму, третьему и четвертому тактам работы устройства при формировании исходных текуш,их адресов записи или обработки.

По завершении конечного цикла записываемый подмассив информации окажется распределенным произвольным образом по ранее свободным числовым линейкам 2 накопителя 1 логического запоминающего устройства, а в одной из числовых линеек 2 будет записан код текущего адреса записи.

Следует отметить, что, если часть массива записана в следующих друг за другом числовых линейках 2, то в соответствующих им ячейках 14 будут записаны одинаковые текущие адреса и эти ячейки 14 будут находиться в состоянии «Заняты, кроме той из них,которая имеет младший порядковый номер. Эта ячейка будет находиться в состоянии «Ожидание.

Если в режиме записи массивов информации все числовые линейки 2 окажутся занятыми, то иа шине 29 индикации состояния иакопите я., подключенный к выходам индикации состояния 27 ячеек 14, сигнал будет отсутствовать, что служит признаком прекраш,еиия работы в режиме записи массивов информации,

Работа логического запоминающего устройства в режиме логической обработки массивов ииформации осуществляется следующим образом.

При работе устройства в этом режиме также различается три цикла функционирования: иачальный, текущий и конечный и существует три видалогической обработки: массив- массив (последовательно по словам), массив-ело-. во (последовательно по словям) и массив-слово (параллельно по словам).

Работа логического запоминающего устрой стса в режиме логической обработки вида массив - массив (последовательно по словам).

Будем полагать, что один из обрабатываемых массивов ииформации распреде-иен произвольным образом по числовым линейкам 2 iaкопителя I, а второй массив информации поступает извие последовательно по словам на регистрту1ова 18...

В первом такте начального цикла на шину уиравлеиия 34 подается сигнал, разрешающий работу элементов И iO, по входным шинам 17 в регистр слова 18 поступает первое слово второго массива, а по входам П через элементы И 10 в регистр адреса 2 и в блок 13

пост;)1ает считанный с выходного регистра 8 код текущего адреса обработки, занесенный в выходной регистр 8 по окончанию работы устройства в режиме обращения к текущему адре У

Во втором такте поступают сигналы на шины управлении 2 и 22, в соответствие с которыми в ячейках 14, находящихся в состояниях «Ожидание, выполняется операция по п. 9, (см. табл .). Отсутствие сигнала на шине индикации 26 указывает на то, что в накопителе I отсутствует массив информации, имеющий начальный адрес, записанный в регистр адреса 12. В этом случае устройство прекращает логическую обработку заданных -массивов информации.

В этом же такте на шины управления 32 подаются сигналы, настраивающие адресный 5 и разрядный 6 блоки управления иа выполнение в числовой линейке 2, соответствующей возбужденному управляющему выходу 30, заданной операции над содерж 1мым этой числовой линейки 2 и содержимым регистра слова 18. ..

-i

Результат операции либо остается в этой шсловой линейке 2, либо поступает иа выходвые шины 9. Кроме того, сигнал с возбужденного управляющего выхода 30 поступает и на разрешающий вход 31 последующей ячейки 14, в которой выполняется операция по п. 8 (см. табл.).

Результатом начального цикла является выпатнение операции над первыми словами обрабатываемых массивов информации и перевод последующей ячейки 14 в состояние «Ожидание, если она находилась в состоянии. «Занята. EoiH же. (юследующая ячейка 14 находилась в состоянии «Свободна или «Ожидание, то состояние этой ячейки 14 сохраняется.

После окончания начального цикла следу5от текущие циклы функционирования устройства в режиме логической обработки массивов.

В первом Такте текущего цикла подаются сигналы на управления 21 и блок формирования массивов 15 переходит в режим «Опрос содержимого, а в ячейках 14, находящихся в состоянии «Ожидание, выполняется операция по п. 6 (см. табл.). Появление сигиала на шине индикации 26 указывает иа то, что по данному текущему адресу можно производить логическую обработку, а отсутствие сигнала-на необходимость увеличения текуще-i го адреса обработки. В этом же такте в регистр слова 18 заносится очередное слово второго массива.

Во втором такте содержимое блока 13 либо остается неизменным, либо увеличивается на единицу второго разряда сигналами , поступающими по шинам управления 24 в зависимости от того, присутствовал или нет в первом такте сигнал иа шине индикации 26.

В остальном второй такт протекает акалогичио второму такту начального цикла функ- , циоиироваиия устройства в режиме логической обработки Отсутствие сигнала иа шине иидикации 25 по окончании второго такта говорит

о том, что массив информации, хранящийся в накопнг..-лс 1, обработан гюлностью.

Переход к конечному циклу осуществляется в двух случаях: либо кончился массив, поступающий на регистр слова, либо закончилась обработка массива, хранящегося в накопитеie I.

В первом слууае функционирование уст юйства протекает аналогично конечному 1иклу режима записи массивов информации, а во втором случае в первом такте но шинам 33 производится начальная установка блока 13 в нуль.

Во втором такте управляющие сигналы подаются по шинам управления 24 и производят запись единицы во второй разряд блока 13.

В третьем такте по шине управления 23 поступает сигнал, переводящий вторую группу элементов И 6 в открытое состояние, и исходный текущий адрес, сформированный во втором такте, поступает из регистра адреса 12 и блока 13 в регистр слова 18.

В четвертом такте по шинам 33 производится установка блока 13 в нуль. Одновременно на , шину управления 21 подается сигнал, настраивающий блок формирования массивов 15 на «Опрос содержимого, в ячейках 14 которого выполняется операция по п. 6 (см. табл.).

В этом же такте на шины управления 32 подается сигналы, в соответствии с которыми в числовой линейке 2, хранившей ранее текущий адрес обработки, записывается исходный текущий адрес, находящийся в регистре слова 18.

Аналогичным образом происходит логическая обработка массивов вида массив - слово (последовательно по словам). Однако, в этом случае в регистре слова 18 постоянно хранится одно и то же слово, участвующее в логической обработке «ассива, записанного в накопитель 1.

При организации логической обработки вида массив - слово (параллельно по словам) необходимо, чтобы в текущем цикле при функцнонировании устройства в режиме записи. управляющие сигналы во втором такте постоянно, подавались по шинам управления 19, 20 и 32. В результате все ячейки 14, в которых ,записей текущий адрес массива, окажутся в сбсгояииях «Ожидание. Кроме этого, при записи иасснаа остается неизменный текущий адрес. При этом будет производиться одновременная логическая обработка всех слов массива, хранящегося в накопителе 1.

Работа логического запоминающего устройства в режиме контроля йакопителя происходит следующим образом.Считаем, что к началу контроля накопителя все ячейки 14 находятся в состоянии «Свободна, а регистр слова 18 установлен в «нуль, либо в « единицу,

В первом такте на шины управления 19 и 20 поступают сигналы, настраивающие ячейки 14 на прием кода поступающего от регистра адреса 12 и блока 13 (код может быть произвольным). Как указывалось ранее, логика рабо ы ячеек 14 и блока формирования массивов 15 такова, что в данном случае поступающий код будет записан в первую ячейку, которая перейдет в состояние «Ожидание и выдаст сигнал на свой управляющий выход 30.

В этом же такте на шины управления 32 поступают снгналы, настраивающие разрядный 6 и адресный 5 блоки управления на запись содержимого регистра слова 18 в числовую линейку 2, соответствующую возбужденному управляющему выходу 30.

Во втором и последующих тактах (число которых равно количеству числовых линеек 2) управляющие сигналы поступают только по шинам 20 и 32. Ячейки 14 последовательно, иачиная со второй, производят прием кода из регистра адреса 12 и блока 3 if .ереходят в состояние «Занята а в соответствующих им числовых линейках 2 производится запись содержимого регистра слова 18.

В результате, в предпосче, ;.чгм такте окажется заполненной последняя числовая линейка 2 иакопителя 1.

В последнем такте по шиигш 17 в регистр слова 18 заносится слово, выполняя определеииую логическую операцию.иад которым и содержимым какой-либо числовой линейки 2 можно по результату операции судить о-работоспособиости числовых линеек 2.

В серии последующих тактов (по числу числовых линеек 2) на шины управления 21 н 22 поступают сигналы, настраивающие ячейки 14 .иа выполнение операций по. пп. 8 и 9 табл., а по шинам управления 32 поступают сигналы, нас1раивающие разрядный 6 и адресный 5 блоки управления на организацию в числовой линейке 2, соответствующей возбужденному управляющему выходу 30 логической операции

над содержанием этой числовой линейки 2 и регистра слова 18, по результату которой можно судить о работоспособности элементов паия ти этой числовой линейки 2. Если один из эЙемеитов памяти числовой линейки 2 имеет отказ, приводящий к искажению результата операдни, то сигнал в шиие чтеиия 7, соответствующей этому элементу памяти, будет отличаться от сигналов в остальных шинах чтения 7 и на выходе элемента И-НЕ 36, подключенного к шинам чтения, появится сигнал, поступающий на один из входов каждого из элементов И 37. В этой же серии тактов подается сигнал на шину 38, поступающий иа вторые «ходы элементов И 37.

.. fit

Наличие сигнала (сигнала об отказе) ца выходе элемента И-НЕ 36 вызовет срабатывание того элемента И 37, третий вход которого подключен к возбужденному управляющему выходу 30 14, соответствующей числовой линейке 2, контролируемой в данном такте.

Выхбдной сигнал сработавщего элемента И 37 произведет запись единицы вмладший разряд ячейки 14, соответствующей числовой линейке 2, имеющей отказ.

Запись единицы в младший разряд ячейки 14 эквивалентна отк.лючеиию соответствующей числовой линейке 2, имеющей отказ, так как

ни один из кодов, формируемых в регистре адреса 12 н блоке 13, не совпадает с кодом, хранимым в этой ячейке 2, а, следовательно, ни при одном режиме работы Данная числовая

линейка 2 не будет выбрана, что позноляот повысить достоверность результатов обработки информации в описанном логическом запоминающем устройстве.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| Логическое запоминающее устройство | 1974 |

|

SU492934A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Логическое запоминающее устройство | 1986 |

|

SU1316047A1 |

| Логическое запоминающее устройство | 1979 |

|

SU858103A2 |

| Логическое запоминающее устройство | 1976 |

|

SU650103A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

Запись

Свободна

20

Занята или Ожидание

Свободна или .

Занята5, Сохранение состояния

21

Занята .8, Установка ячейки 14 в состояние Ожив. Сравнение числа, хранящегося в ячейке 14,

Запись кода начального или текущего массива и выпача сигнала на управляющий выход ЗО, еспк отсутствует сигнал на входе запрета записи 28 этой ячейки 14, в противном случае - сохранение состояния.

ющем входе 31 этой ячейки 14 . появится сигнал, в противном случае - сохранение состояния.

ке 14 с кодом начального или текущего адреса массива, выдача сигнала на управляюгдий выход ЗО и на выход признака модификашга 25 в слу. чае совпадения, в противном случае .сохранение состояния.

дание, естш на разрешающем входе 31 этой ячейки 14 присутствует сигнал, в противном случав - сохранение состояния. с кодом начального или текущего адреса массива. В случае совпадения - выдача сигналов на управляющий выход ЗО в наг выхоа признака модифшсапии 25 и переход В состоянпе Свободна, в противном случае - сохранение состояния. 15 Формула изобретения Логическое запоминающее устройство по авт. св. № 492934, отличающееся тем, что, с целью повышения надёжности устройства, оно содержит элементы И и элемент И-НЕ, входы которого подключены к шинам чтения, а выход - к одннм из входов элементов И, другие входы элементов И соединены соответственно с одной из управляющих шин и управftл

У I т 1 Ч 1 Г ляющими выходами соответствующих логических запоминающих ячеек блока формирования массивов, а выходы элементов И подключены к соответствующим входам ячеек блока формирования массивов. Источники информации, принятые во внямание при экспертизе: 1.Авторское свидетельство СССР № 432598, М. Кл. G Г1 С 15/00, 1972. 2.Авторское свидетельство СССР Nk 492934, М. Кл. G И С 15/00,. 1974Г (I i vf, Lp

.j:,jfciiJf---jj |-«t-CJg4|

j|..

Авторы

Даты

1978-05-25—Публикация

1974-10-24—Подача