Предлагаемый декадный счетчик может найти применение в вычислительной технике и в устройствах цифровой индикации.

Известные декадные счетчики содержат управляющий триггер, сдвиговый регистр, дешифратор знаков и логические элементы. Применение в указанной схеме однотактного сдвигового регистра с реостатно-емкостными связями затрудняет использование счетчика в широком диапазоне частот. Кроме того, «единица, циркулирующая в сдвиговом регистре в процессе счета, не восстанавливается в случае сбоя, что приводит к нарушению работы схемы.

В предлагаемом декадном счетчике, с целью расширения частотного диапазона и повышения надежности в работе, входные сигналы поступают на счетный вход управляющего триггера, «нулевой выход которого подан на шину сдвига четных ячеек пятикаскадного двухтактного сдвигового регистра, а «единичный выход - на шину сдвига нечетных ячеек непосредственно и к входу установки в «I начальной ячейки регистра - через схему запрета; выходы четных ячеек регистра через, схему «ИЛИ поданы на схему управления, а выходы нечетных ячеек совместно с «единичным и «нулевым выходами управляющего триггера соединены со входами дешифратора знаков. У втоматический запуск сдвигового регистра производится в моменты времени, соответствующие 1, 2, 21-му... импульсу на входе управляющего триггера.

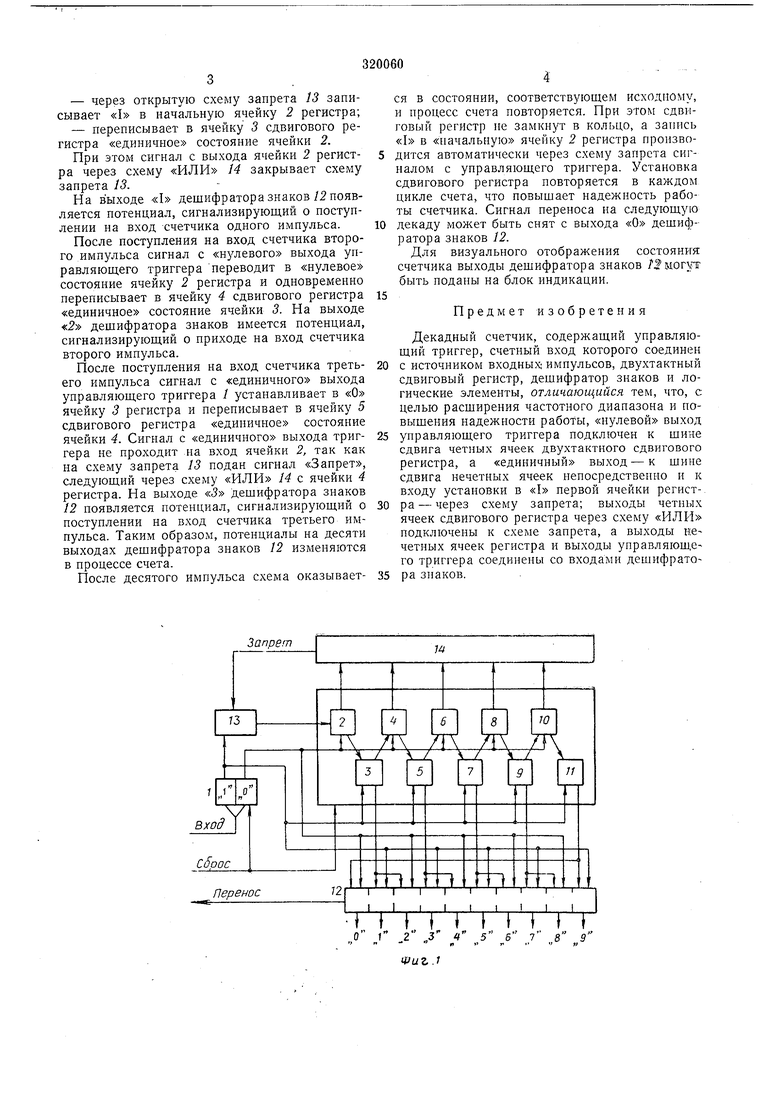

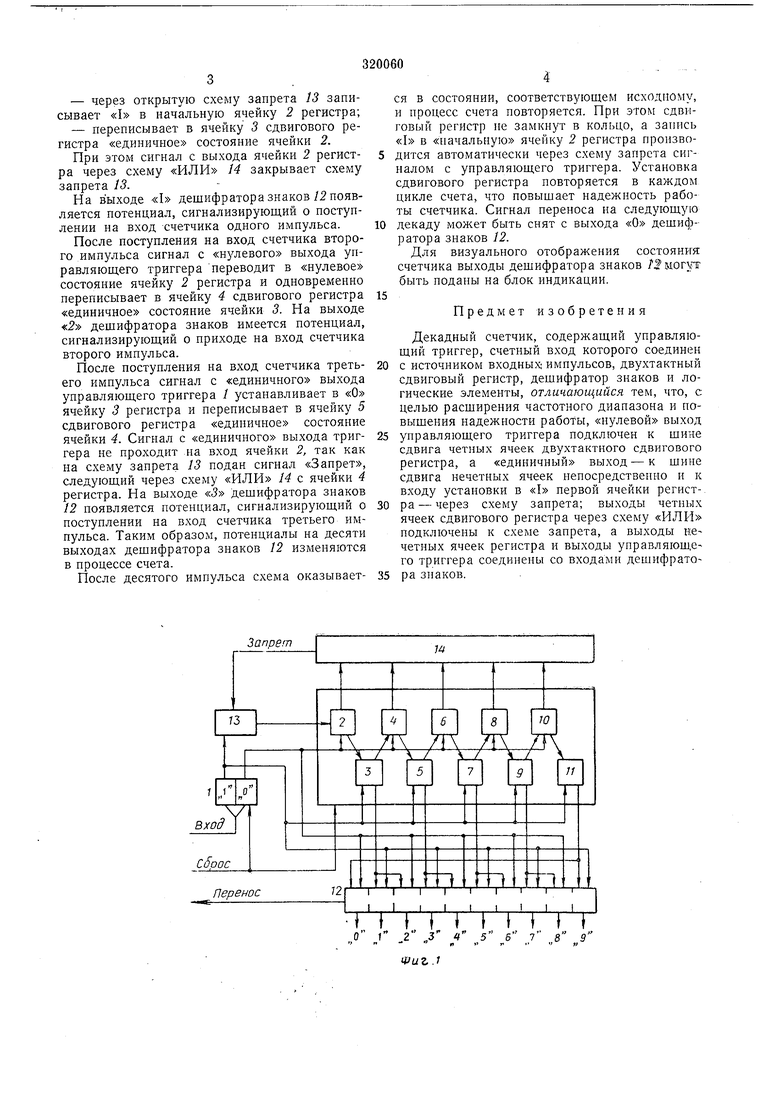

На фиг. 1 представлена блок-схема декадного счетчика; на фиг. 2 - временная диаграмма работы декадного счетчика (а - входные импульсы; б, в - сигналы на «единичном и «нулевом выходах управляющего триггера; г, д, е, ж, 3 - выходные сигналы знаков с нечетных ячеек регистра; и, к, л, м, н, о, п, р, с, т - потенциалы на выходах дешифратора знаков, изменяющиеся в процессе счета).

В исходном состоянии под действием импульса «Сброс управляющий триггер / и

5 ячейки 2-10 сдвигового регистра находятся в «нулевом состоянии, а ячейки // - в «единичном состоянии, что необходимо для сигнализации с помощью дешифратора знаков

12об отсутствии сигналов на входе управляю0 щего триггера (на выходе «О дешифратора

знаков 12 имеется потенциал). Отсутствуют сигналы на входах и выходах схемы запрета

13и схемы «ИЛИ 14.

Первый счетный импульс, поступающий на 5 вход схемы, переключает управляющий триггер / в «единичное состояние. Сигнал с «единичного выхода управляющего триггера производит следующие операции:

-через открытую схему запрета 13 записывает «I в начальную ячейку 2 регистра;

-переписывает в ячейку 3 сдвигового регистра «единичное состояние ячейки 2.

При этом сигнал с выхода ячейки 2 регистра через схему «ИЛИ 14 закрывает схему запрета 13.

На выходе «I дешифратора знаков/2 появляется потенциал, сигнализирующий о поступлении на вход счетчика одного импульса.

После поступления на вход счетчика второго импульса сигнал с «нулевого выхода управляющего триггера переводит в «нулевое состояние ячейку 2 регистра и одновременно переписывает в ячейку 4 сдвигового регистра «единичное состояние ячейки 3. На выходе «2 дещифратора знаков имеется потенциал, сигнализирующий о приходе на вход счетчика второго импульса.

После поступления на вход счетчика третьего импульса сигнал с «единичного выхода управляющего триггера / устанавливает в «О ячейку 3 регистра и переписывает в ячейку 5 сдвигового регистра «единичное состояние ячейки 4. Сигнал с «единичного выхода триггера не проходит на вход ячейки 2, так как на схему запрета 13 подан сигнал «Запрет, следующий через схему «ИЛИ 14 с ячейки 4 регистра. На выходе «5 дещифратора знаков 12 появляется потенциал, сигнализирующий о поступлении на вход счетчика третьего импульса. Таким образом, потенциалы на десяти выходах дещифратора знаков 12 изменяются в процессе счета.

После десятого импульса схема оказывается в состоянии, соответствующем исходному, и процесс счета повторяется. При этом сдвиговый регистр не замкнут в кольцо, а запись «I в «начальную ячейку 2 регистра производится автоматически через схему запрета сигналом с управляющего триггера. Установка сдвигового регистра повторяется в каждом цикле счета, что повыщает надежность работы счетчика. Сигнал переноса на следующую

декаду может быть снят с выхода «О дешифратора знаков 12.

Для визуального отображения состояния счетчика выходы дешифратора знаков /f могугг быть поданы на блок индикации.

Предмет изобретения

Декадный счетчик, содержащий управляющий триггер, счетный вход которого соединен с источником ВХОДНЫХ; импульсов, двухтактный сдвиговый регистр, дешифратор знаков и логические элементы, отличающийся тем, что, с целью расширения частотного диапазона и повышения надежности работы, «нулевой выход управляющего триггера подключен к щине сдвига четных ячеек двухтактного сдвигового регистра, а «единичный выход - к шине сдвига нечетных ячеек непосредственно и к входу установки в «I первой ячейки регист-, ра - через схему запрета; выходы четных ячеек сдвигового регистра через схему «ИЛИ подключены к схеме запрета, а выходы нечетных ячеек регистра и выходы управляюш,его триггера соединены со входами дешифратора знаков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Многофункциональная логическая схема | 1973 |

|

SU490119A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОРОТКИХ ИНТЕРВАЛОВ ВРЕМЕНИ В ЦИФРОВОЙ КОД | 1969 |

|

SU257883A1 |

| Симметричный делитель частоты импульсов | 1982 |

|

SU1089763A2 |

| ДЕСЯТИЧНЫЙ СЧЕТЧИК | 1967 |

|

SU197288A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Коммутатор | 1985 |

|

SU1272494A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО КОМАНД | 1970 |

|

SU268020A1 |

| Частотомер | 1980 |

|

SU894591A1 |

| Оперативное запоминающее устройство с самоконтролем | 1977 |

|

SU708423A1 |

Запрет

T.,m./r.,m,,m

72

Перенос

i I IT t

о 1 2 „J 4 5 в 7 8 9

}пfV г If/

/ 2 5 4 S 6 7 8 9 Ю 11

JLJLJl JLJLJL rLJl Il Jl Jl

г Г

д

е

ж

3

м н о п

р с

Даты

1971-01-01—Публикация