Изобретение может быть использовано в разработка.ч перспективной аппаратуры беспоисковой связи.

Известная схема делителя частоты с дробным переменным коэффициентом деления, содержащего декадные счетчики, матрицы выбора коэффициента, схемы логики переноса схемы фиксации полного заполнения счетчика, схемы памяти, схемы совпадения, формирователь импульса установки в исходное состояние, предназначена для снижения уровня пульсаций опорного колебания, а также для получения более мелкой сетки, чем при использовании делителя с целым переменным коэффициентом. Положительный эффект достигается за счет по возможности равномерно распределенного во времени исключения импульсов в исходной их последовательности. Схема получается исключительно сложной, если число дробных разрядов делителя с переменным коэффициентом деления (ДПКД) больше двух. Поэтому реализация известного ДПКД не представляется целесообразной изза его сложности.

Цель изобретения - повышение точности деления при одновременном упрощении схемы.

ков, вход декады десятых долей соединен с выходом делителя целых коэффициентов, причем управление декадами более низшего дробного знака осуществляется от декад соответствующего высшего порядка с помощью переключаемых схем совпадения и памяти, а декада единиц делителя целых коэффициентов управляется от декады десятых долей также с помощью схемы совпадения и памяти.

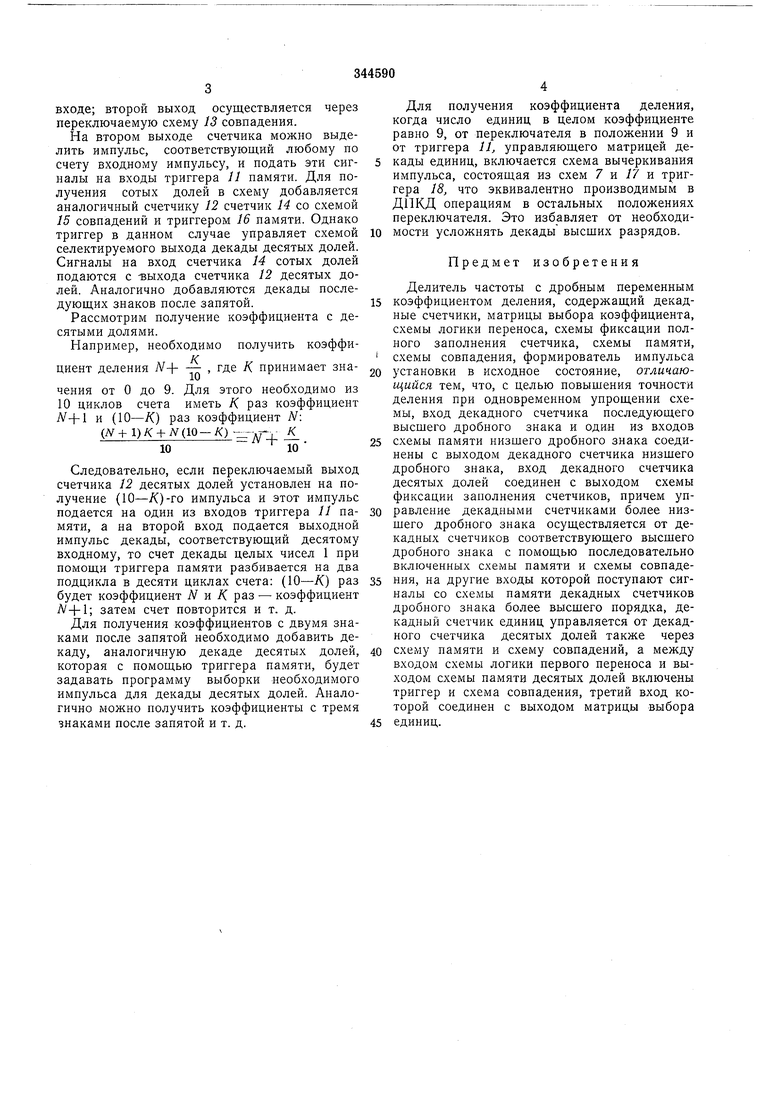

На чертеже представлена схема предлагаемого делителя.

В основной цепи ДПКД содержит делитель, в котором производится набор целых чисел устанавливаемого коэффициента. Он состоит из декадных счетчиков /, 2, 3, матриц 4, 5, 6 выбора коэффициента, схем 7, 8 логики переноса, схемы 9 фиксации полного заполнения счетчика и формирователя 10 импульса

установки в исходное состояние. Схема установки единиц в процессе работы имеет возможность сдвигать коэффициент деления целого ДПКД на единицу по команде с триггера 11 памяти.

Выходные сигналы с выхода делителя целых чисел подаются на вход декадного счетчика 12 десятых долей, который управляет триггером памяти. Счетчик 12 имеет два выхода: на одном из них сигнал появляется

входе; второй выход осуществляется через переключаемую схему 13 совпадения.

На втором выходе счетчика можно выделить импульс, соответствующий любому по счету входному импульсу, и подать эти сигналы на входы триггера 11 памяти. Для получения сотых долей в схему добавляется аналогичный счетчику 12 счетчик 14 со схемой 15 совпадений и триггером 16 памяти. Однако триггер в данном случае управляет схемой селектируемого выхода декады десятых долей. Сигналы на вход счетчика 14 сотых долей подаются с выхода счетчика 12 десятых долей. Аналогично добавляются декады последующих знаков после запятой.

Рассмотрим получение коэффициента с десятыми долями.

Например, необходимо получить коэффи1

циент деления - , где К. принимает значения от О до 9. Для этого необходимо из 10 циклов счета иметь К раз коэффициент Я-f 1 и (10-К.) раз коэффициент N: (N+l)K + N(lQ-К) -z-гд J- А 1010

Следовательно, если переключаемый выход счетчика 12 десятых долей установлен на получение (10-/С)-го импульса и этот импульс подается на один из входов триггера 11 памяти, а на второй вход подается выходной импульс декады, соответствующий десятому входному, то счет декады целых чисел 1 при помощи триггера памяти разбивается на два подцикла в десяти циклах счета: (10-/С) раз будет коэффициент N н К раз - коэффициент Л/+1; затем счет повторится и т. д.

Для получения коэффициентов с двумя знаками после запятой необходимо добавить декаду, аналогичную декаде десятых долей, которая с помощью триггера памяти, будет задавать программу выборки необходимого импульса для декады десятых долей. Аналогично можно получить коэффициенты с тремя знаками после запятой и т. д.

Для получения коэффициента деления, когда число единиц в целом коэффициенте равно 9, от переключателя в положении 9 и от триггера 11, управляющего матрицей декады единиц, включается схема вычеркивания импульса, состоящая из схем 7 и /7 и триггера 18, что эквивалентно производимым в Д11КД операциям в остальных положениях переключателя. Это избавляет от необходимости усложнять декады высших разрядов.

Предмет изобретения

Делитель частоты с дробным переменным

коэффициентом деления, содержащий декадные счетчики, матрицы выбора коэффициента, схемы логики переноса, схемы фиксации полного заполнения счетчика, схемы памяти, схемы совпадения, формирователь импульса

установки в исходное состояние, отличающийся тем, что, с целью повышения точности деления при одновременном упрощении схемы, вход декадного счетчика последующего высшего дробного знака и один из входов

схемы памяти низщего дробного знака соединены с выходом декадного счетчика низшего дробного знака, вход декадного счетчика десятых долей соединен с выходом схемы фиксации заполнения счетчиков, причем управление декадными счетчиками более низшего дробного знака осуществляется от декадных счетчиков соответствующего высшего дробного знака с помощью последовательно включенных схемы памяти и схемы совпадения, на другие входы которой поступают сигналы со схемы памяти декадных счетчиков дробного знака более высшего порядка, декадный счетчик единиц управляется от декадного счетчика десятых долей также через

схему памяти и схему совпадений, а между входом схемы логики первого переноса и выходом схемы памяти десятых долей включены триггер и схема совпадения, третий вход которой соединен с выходом матрицы выбора

единиц.

f

К декаде следующего дробного знака

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов с дробным переменным коэффициентом деления | 1981 |

|

SU951713A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧАСТОТЫ С ДРОБНЫМ КОЭФФИЦИЕНТОМ | 1971 |

|

SU436446A1 |

| Делитель частоты с дробным переменным коэффициентом деления | 1974 |

|

SU506130A1 |

| Делитель частоты с дробным переменным коэффициентом деления | 1976 |

|

SU571914A1 |

| Одноканальное устройство для управления вентильным преобразователем | 1978 |

|

SU714618A1 |

| Делитель частоты с дробным пере-МЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU834931A1 |

| Программируемый делитель частоты | 1975 |

|

SU621099A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Устройство для деления чисел | 1972 |

|

SU448461A1 |

| ДИСКРЕТНЫЙ ФАЗОВРАЩАТЕЛЬ ГЕНЕРАТОРА ИНФРАНИЗКИХ ЧАСТОТ | 1973 |

|

SU369678A1 |

Даты

1972-01-01—Публикация