Изобретение относится к области нередачи данных и иредназначено для использования в системах с перестраиваемой структурой кода в зависимости от условий передачи и при создании универсальных устройств декодирования.

Известно устройство для декодирования корректирующих кодов, содержащее накопители кодовой комбинации и стираний, формирователь такта, схему установления порога декодирования, логические схемы «И, «НЕ, кодопреобразователь, счетчики, регистры сдвига, узлы сравнения и переключения, а также выходной накопитель.

В целях расщирения функциоиальных возможностей в предлагаемое устройство введен узел вычисления порога декодирования, содержащий счетчнк числа несовпадений, тактовый вход которого через схемы «И и «НЕ и схему запрета связан с выходом узла сравнения кодовых комбинаций; триггеры памяти, входы которых в состоянии «О соединены с выходами «И узла иерезаииси, а в состоянии «1 - с формирователем такта установки; дещифратор норога декодирования, входы которого подключены к выходам триггеров памяти, а выходы - ко входам схемы установления норога декодирования; схемы «И, одни входы которых связаны с выходами разрядов счетчика несовпадений.

а другие - с выходом формирователя такта сброса.

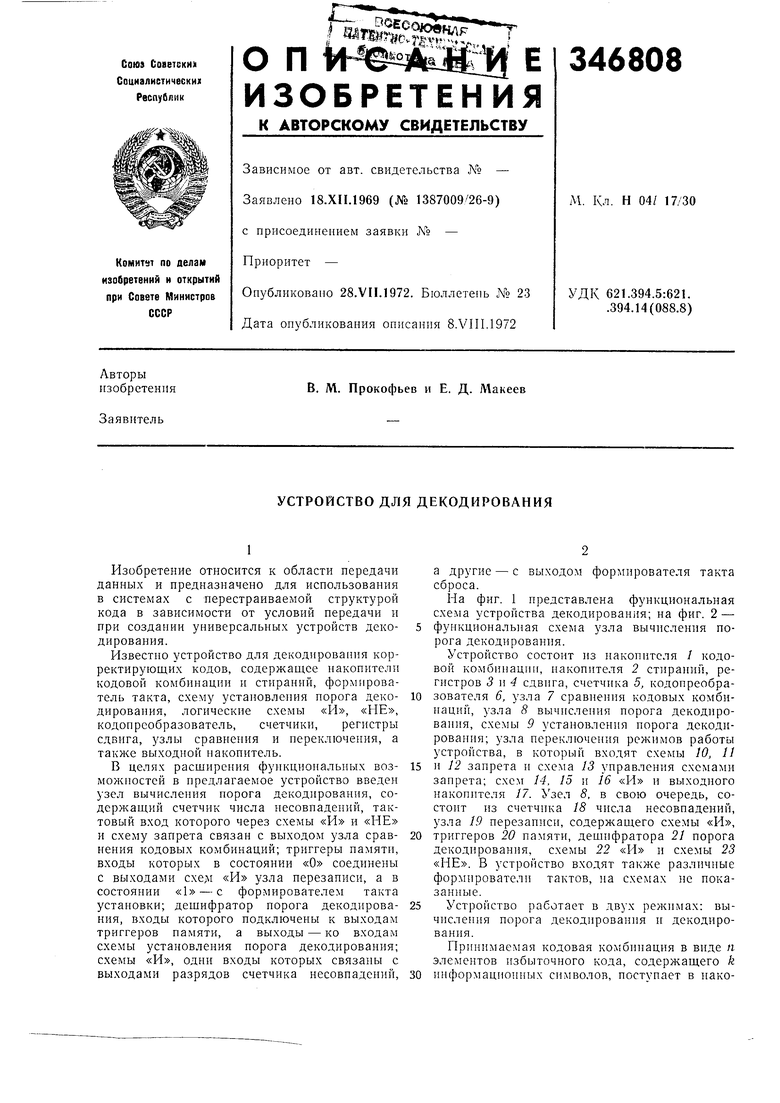

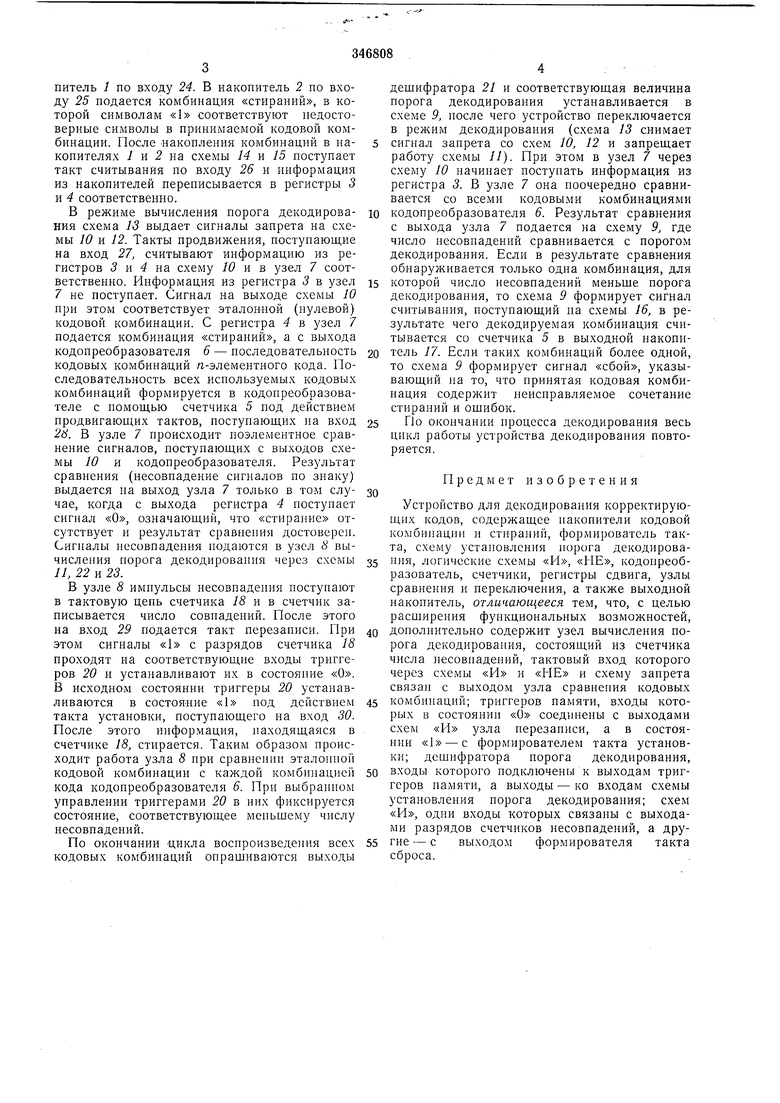

На фиг. 1 нредставлена функциональная схема устройства декодирования; на фиг. 2 - функциональная схема узла вычнслення порога декодирования.

Устройство состонт нз накопителя / кодовой комбинации, накопителя 2 стираний, регистров 3 и 4 сдвига, счетчика 5, кодопреобразователя 6, узла 7 сравиения кодовых комбииаций, узла 8 вычислення норога декодирования, схемы 9 установления норога декодирования; узла переключения режимов работы устройства, в который входят схемы W, 11

н 12 запрета н схема 13 унравления с.хемами запрета; схем 14, 15 и 16 «И и выходного накопителя 17. Узел 8, в свою очередь, состоит из счетчика 18 числа несовпадений, узла 19 перезаписи, содержащего схемы «И,

триггеров 20 памяти, дешифратора 21 порога декодировання, схемы 22 «И и схемы 23 «НЕ. В устройство входят также различные формирователи тактов, на схемах пе показанные.

Устройство работает в двух режимах: вычнсления норога декоднрования и декодирования.

Принимаемая кодовая комбииация в виде п элементов избыточного кода, содержащего k

питель 1 по входу 24. В накопитель 2 по входу 25 подается комбипация «стирапий, в которой символам «1 соответствуют недостоверные символы в принимаемой кодовой комбинации. После Накопления комбинаций в накопителях 7 и 2 на схемы 14 и 15 поступает такт считывания по входу 26 и информация из накопителей переписывается в регистры 3 и 4 соответственно.

В режиме вычисления порога декодирования схема 13 выдает сигналы запрета на схемы 10 и 12. Такты продвижения, поступающие на вход 27, считывают информацию из регистров 3 к 4 на схему 10 и в узел 7 соответственно. Информация из регистра 3 в узел

7не поступает. Сигнал на выходе схемы 10 при этом соответствует эталонной (нулевой) кодовой комбинации. С регистра 4 в узел 7 подается комбинация «стираний, а с выхода кодопреобразователя 6 - последовательность кодовых комбинаций «-элементного кода. Последовательность всех используемых кодовых комбинаций формируется в кодопреобразователе с помощью счетчика 5 под действием продвигающих тактов, поступающих на вход 2. В узле 7 происходит поэлементное сравнение сигналов, поступающих с выходов схемы W и кодопреобразователя. Результат сравнения (несовпадение сигналов по знаку) выдается па выход узла 7 только в том случае, когда с выхода регистра 4 поступает сигнал «О, означающий, что «стирание отсутствует и результат сравнения достоверен. Сигналы несовпадения подаются в узел 8 вычисления порога декодирования через схемы 11,22 и 23.

В узле 8 импульсы несовпадения ностунают в тактовую цепь счетчика /S и в счетчик записывается число совпадений. После этого на вход 29 подается такт перезаписи. При этом сигналы «1 с разрядов счетчика 18 проходят иа соответствующие входы триггеров 20 и устанавливают их в состояние «О.

8исходном состоянии триггеры 20 устанавливаются в состояние «1 под действием такта установки, поступающего на вход 30. После этого информация, находящаяся в счетчике 18, стирается. Таким образом происходит работа узла 8 при сравнении эталонной кодовой комбинации с каждой комбинацией кода кодопреобразователя 6. При выбранном управлении триггерами 20 в них фиксируется состояние, соответствующее меньщему чнслу несовпадений.

По окончании -цикла воснроизвел4е 1ия всех кодовых комбинаций опрашиваются выходы

дешифратора 21 и соответствующая величина порога декодирования устанавливается в схеме 9, после чего устройство переключается в релсим декодирования (схема 13 снимает

сигнал занрета со схем 10, 12 и запрещает работу схемы //). При этом в узел 7 через схему 10 начинает поступать информация из регистра 3. В узле 7 она поочередно сравнивается со всеми кодовыми комбинациями

кодопреобразователя 6. Результат сравнения с выхода узла 7 подается на схему 9, где число несовпадений сравнивается с порогом декодирования. Если в результате сравнения обнаруживается только одна комбинация, для

которой число несовпадений меньще порога декодирования, то схема 9 формирует сигнал считывания, поступающий на схемы 16, в результате чего декодируемая комбинация считывается со счетчика 5 в выходной наконитель П. Если таких комбинаций более одной, то схема 9 формирует сигнал «сбой, указывающий на то, что принятая кодовая комбинация содержит неиснравляемое сочетание стираний и ошибок.

По окончании процесса декодирования весь цикл работы устройства декодирования повторяется.

Предмет изобретения

Устройство для декодирования корректируюпдпх кодов, содержащее накопители кодовой комбинации и стираний, формирователь такта, схему установления порога декодирова ия, логические схемы «И, «ПЕ, кодопреобразователь, счетчики, регистры сдвига, узлы сравнения и переключения, а также выходной накопитель, отличающееся тем, что, с целью расширения функциональных возможностей,

дополнительно содержит узел вычисления порога декодирования, состоящий из счетчика числа несовпадений, тактовый вход которого через схемы «П и «НЕ и схему запрета связан с выходом узла сравнения кодовых

комбинаций; триггеров памяти, входы которых в состоянии «О с выходами схем «И узла перезаписи, а в состоянии «1 - с формирователем такта установки; дешифратора порога декодирования,

входы которого подключены к выходам триггеров памяти, а выходы - ко входам схемы установления порога декодирования; с.кем «П, одни входы которых, связаны с выходами разрядов счетчиков несовпадений, а другие - с выходом формирователя такта сброса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для декодирования | 1974 |

|

SU507952A2 |

| Кодирующее устройство | 1985 |

|

SU1329572A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| Устройство для декодирования линейных кодов | 1985 |

|

SU1304176A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2035124C1 |

| Устройство исправления стираний | 1983 |

|

SU1156260A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

Даты

1972-01-01—Публикация