Изобретение относится к области вычислительной техники.

Известно устройство для преобразования сигнала в двоичный код, содержащее логическое устройство, усилитель напряжения, ячейки памяти.

Цель изобретения - повышение надежности устройства и уменьшение его веса и габаритовЭто достигается тем, что в каждый двоичный разряд добавлен трансфлюксор, обмотка записи которого соединена с логическим блоком « выходом усилителя, а входы усилителя - с обмотками снятия «О и «1 предыдущего разряда, причем обмотка снятия «1 подключена к ячейке памяти.

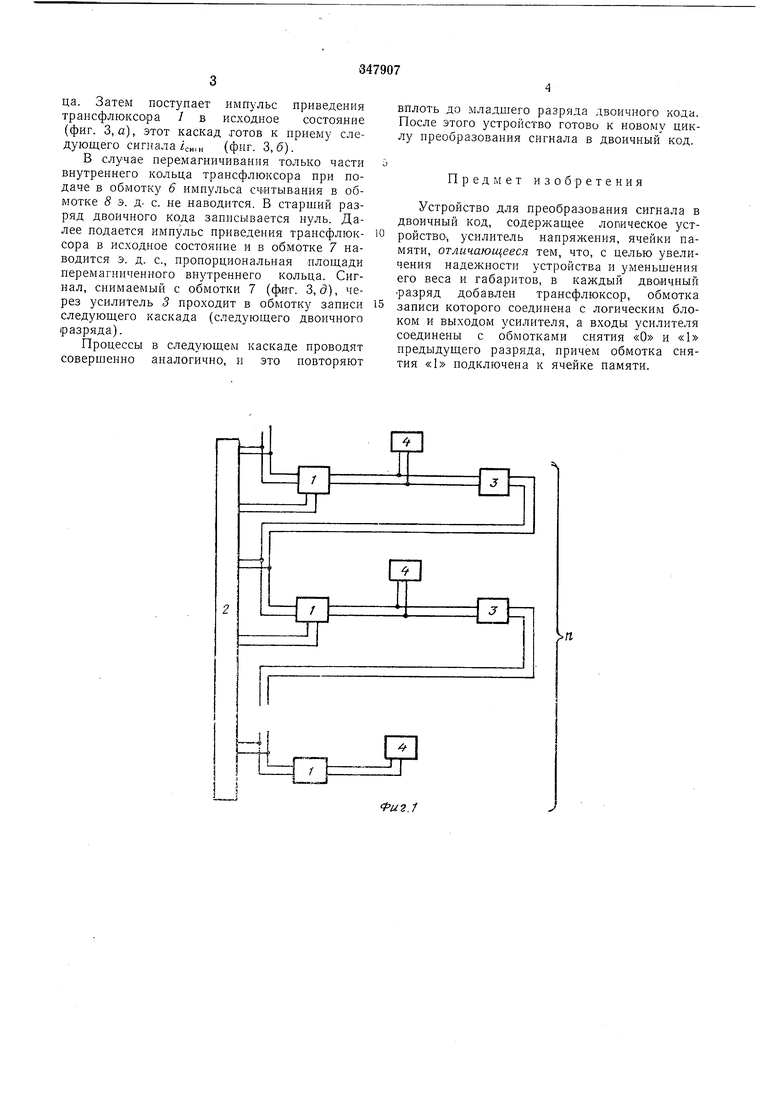

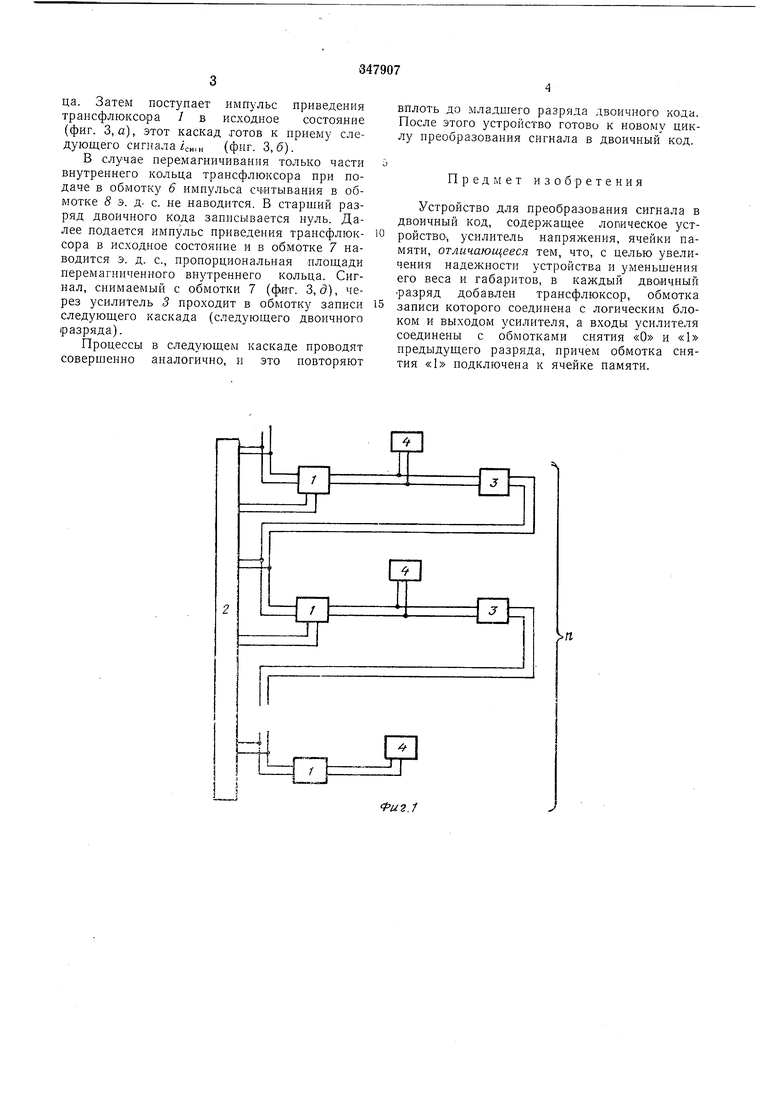

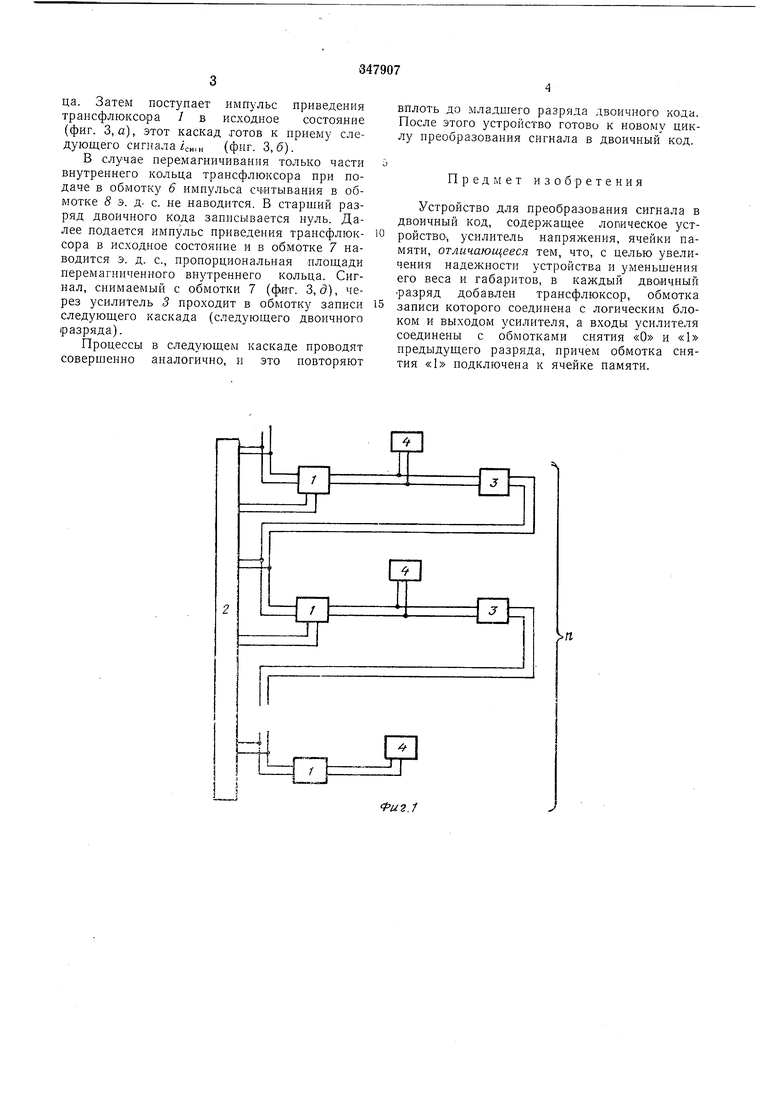

На фиг. 1 изображена блок-схема устройства, на фиг. 2 - принципиальная электрическая схема одного каскада устройства; на фиг. 3 - временные диаграммы подачи импульсов в обмотки трансфлюксора.

Устройство содержит п трансфлюксоров /, логическое устройство 2. усилители 3 напряжения с коэффициентом усиления, равным двум, ячейки 4 памяти (фиг. 1). Каждый трансфлюксор 1 ИМеет о бмотку 5 для при1ведения в исходное состояние и записи сигнала, обмотку 6 считывания, обмотку 7 снятия сигнала «О, обмотку 8 снятия сигнала «1 (фиг. 2).

Перед подачей сигнала icur (фиг. 3, б) в обмотку 5, трансфлюксор переводится в исходное состояние подачей мощного импульса г.чнг (фиг. 3, б) в ту же обмотку, но другой полярности по сравнению с сигналом 1™™При подаче входного сигнала гсигн в первый каскад (старший разряд двоичного кода) в зависимости от ве.тичины входного сигнала происходит перемагничивание части внутреннего кольца или всего внутреннего и части внешнего кольца трансфлюксора, причем максимально возможный входной сигнал не перемагничпвать оба кольца трансфлюксора полностью.

Часть внутреннего кольца или ири большом сигнале все внутреннее и часть внешнего кольца трансфлюксора перемагннчиваются Проиорционально входному сигналу.

При перемагничпвании всего внутреннего и части внешнего кольца трансфлюксора в обмотку 6 считывания поступает р.мпульс считывания г чмт (фиг. 3,8). В обмотке 8 наводится э. д. с., величина которой ироиорциональна илошади пepe aгш чeннoгo внешнего кольца трансфлюксора. Сигнал, снимаемый с обмотки 8 (фиг. 3,г), через усилитель 3 подается в обмотку 5 записи следующего каскада (следующего двоичного разряда). Если имеется сигнал с обмотки 8, то в старший разряд двоичного кода записывается единица. Затем поступает импульс приведения трансфлюксора 1 в исходное состояние (фиг. 3, а), этот каскад готов к приему следующего сигнала/си,н (фиг. 3,6).

В случае иеремагничиваиия только части внутреннего кольца трансфлюксора при подаче в обмотку 6 импульса сч итывания в обмотке 8 в. д. с. не наводится. В старший разряд двоичного кода записывается нуль. Далее подается импульс приведения трансфлюксора в ис.ходное состояние и в обмотке 7 наводится 3. д. с., пропорциональная площади перемагничеиного внутреннего кольца. Сигнал, снимаемый с обмотки 7 (фиг. 3, d), через усилитель 3 проходит в обмотку записи следующего каскада (следующего двоичного разряда).

Процессы в следующем каскаде проводят совершенно аналогично, и это повторяют

вплоть до младшего разряда двоичного кода. После этого устройство готово к ново.му циклу иреобразования сигнала в двоичный код.

Предмет изобретения

Устройство для преобразования сигнала в двоичный код, содержащее лопическое устройство, усилитель иапряжения, ячейки памяти, отличающееся тем, что, с целью увеличения надежности устройства и уменьшения его веса и габаритов, в каждый двоичный разряд добавлен трансфлюксор, обмотка записи которого соединена с логическим блоком и выходом усилителя, а в.чоды усилителя соединены с обмотками снятия «О и «1 предыдущего разряда, причем обмотка снятия «1 подключена к ячейке памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования сигнала в двоичный код | 1976 |

|

SU661772A1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 1970 |

|

SU268494A1 |

| МАГНИТНЫЙ ДЕШИФРАТОР | 1973 |

|

SU374726A1 |

| Устройство дискретной обработки информации | 1980 |

|

SU884140A1 |

| УСТРОЙСТВО для ВЫБОРКИ ИНФОРМАЦИИ в АССОЦИАТИВНОЙ НАМЯТИ | 1968 |

|

SU209538A1 |

| УСТРОЙСТВО для СЕЛЕКТИВНОГО ВЫВОДА ИНФОРМАЦИИ ИЗ ПРОВОЛОЧНЫХ ИСКРОВЫХ КАМЕР | 1967 |

|

SU202581A1 |

| Логическое устройство | 1973 |

|

SU438122A1 |

| РЕВЕРСИВНЫЙ ДВОИЧНЫЙ СЧЕТЧИК | 1972 |

|

SU329676A1 |

| УСТРОЙСТВО для КОДИРОВАНИЯ ЧИСЕЛ в РЕКУРРЕНТНОЛ!КОДЕ | 1972 |

|

SU353346A1 |

| АБОНЕНТСКИЙ КОМПЛЕКТНА ТРАНСФЛЮКСОРАХ ДЛЯ АВТОМАТИЧЕСКИХТЕЛЕФОННЫХ СТАНЦИЙ С ЭЛЕКТРОИНЫГу\УПРАВЛЕНИЕМ | 1970 |

|

SU427486A1 |

t-CJUnj

Даты

1972-01-01—Публикация