Изобретение относится к устройствам автоматики и вычислительной техники и может использоваться для построения аналого-цифровых преобразователей (АЦП) непрерывного действия.

Логическим устройством АЦП непрерывного действия, работающим по методу единичных приращений, является реверсивный счетчик. Это устройство обладает низким быстродействием при уравновешивании больших изменений входного аналогового сигнала, происходящих скачком.

Существует другой метод построения непрерывных АЦП, сходный с методом поразрядного взвещивания и отличающийся от него тем, что уравновешивание начинается с младщего разряда.

Цель изобретения - повышение быстродействия устройства и упрощение схемы при уравновешивании быстрых изменений аналогового сигнала.

Эта цель достигается тем, что в цепь коллектора транзистора прямого кода каждого разряда включены обмотки входная и считывания трансфлюксора прямого кода и обмотка сброса трансфлюксора обратного кода следующего разряда, а в цепь коллектора транзистора обратного кода каждого разряда включены обмотки входная и считывания трансфлюксора обратного кода и обмотка сброса

трансфлюксора прямого кода следующего разряда, выходные обмотки всех трансфлюксоров включены в базовые цепи соответствующих транзисторов.

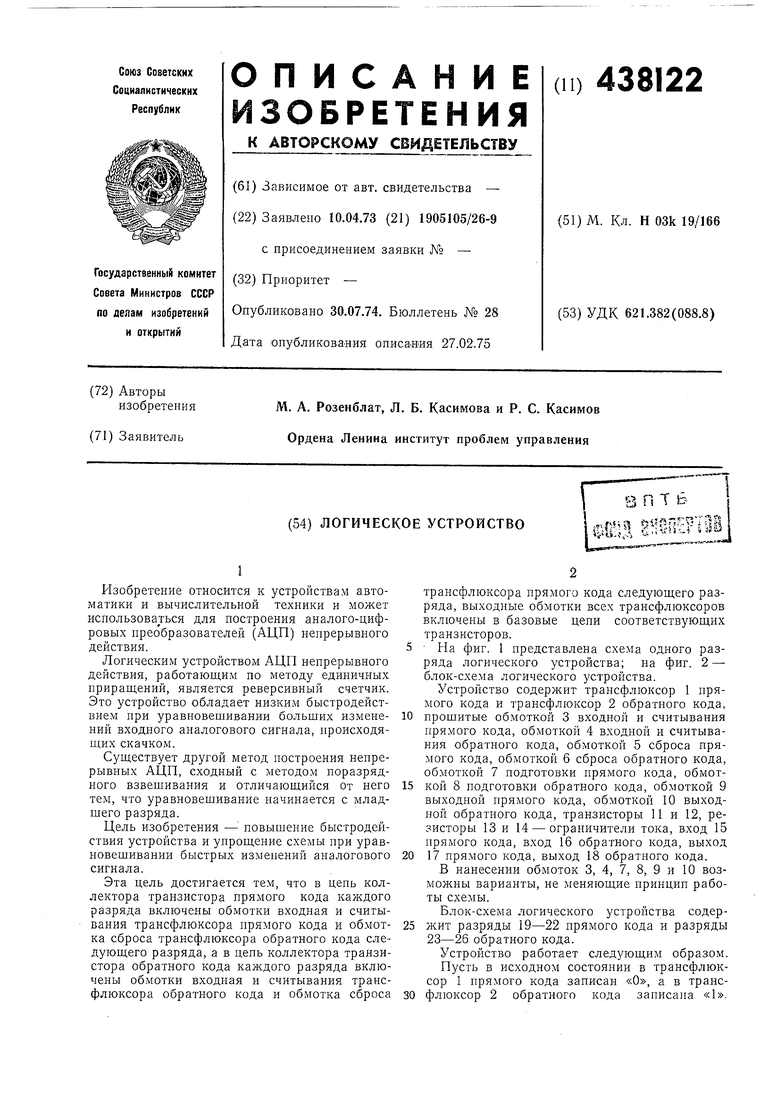

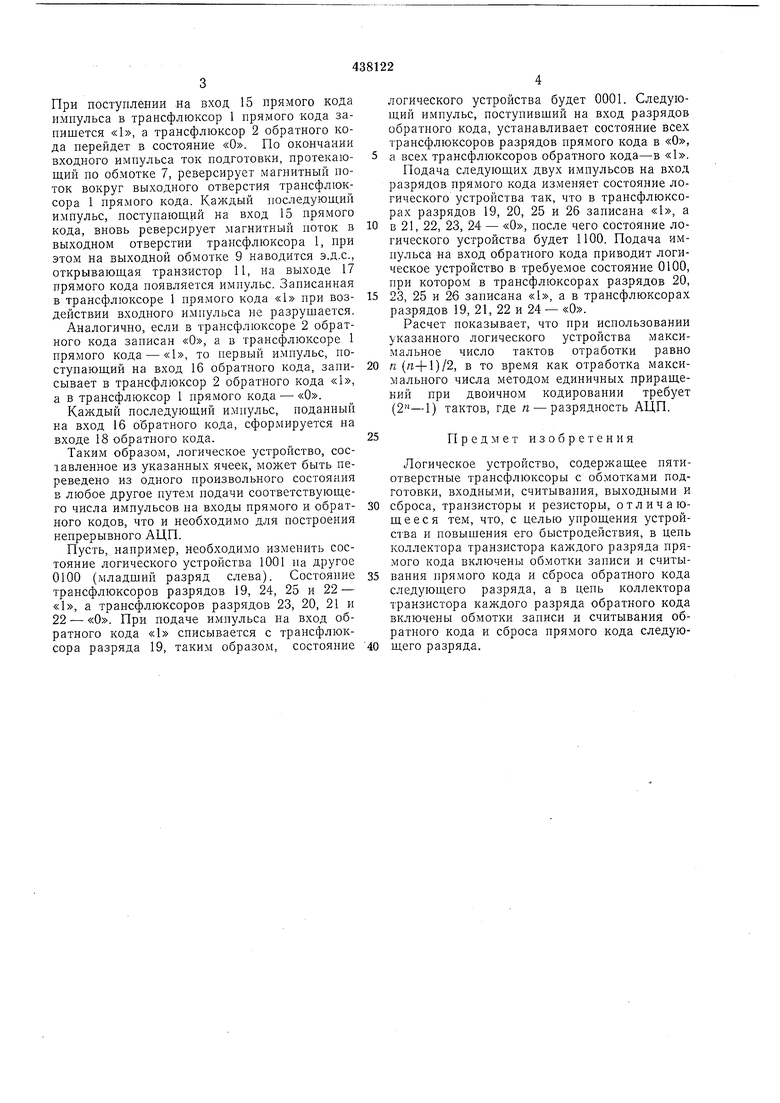

На фиг. 1 представлена схема одного разряда логического устройства; на фиг. 2- блок-схема логического устройства.

Устройство содержит трансфлюксор 1 прямого кода и трансфлюксор 2 обратного кода,

прошитые обмоткой 3 входной и считывания прямого кода, обмоткой 4 входной и считывания обратного кода, обмоткой 5 сброса прямого кода, обмоткой 6 сброса обратного кода, обмоткой 7 подготовки прямого кода, обмоткой 8 подготовки обратного кода, обмоткой 9 выходной прямого кода, обмоткой 10 выходной обратного кода, транзисторы И и 12, резисторы 13 и 14 - ограничители тока, вход 15 прямого кода, вход 16 обратного кода, выход

17 прямого кода, выход 18 обратного кода.

В нанесении обмоток 3, 4, 7, 8, 9 и 10 возможны варианты, не меняющие принцип работы схемы.

Блок-схема логического устройства содержит разряды 19-22 прямого кода и разряды 23-26 обратного кода.

Устройство работает следующим образом. Пусть в исходном состоянии в трансфлюксор 1 прямого кода записан «О, а в трансфлюксор 2 обратного кода записана «1.

При поступлении на вход 15 прямого кода пмпульса в трансфлюксор 1 прямого кода запишется «1, а трансфлюксор 2 обратного кода перейдет в состояние «О. По окончании входного импульса ток подготовки, протекающий по обмотке 7, реверсирует магнитный поток вокруг выходного отверстия трансфлюксора 1 прямого кода. Каждый последующий импульс, поступающий на вход 15 прямого кода, вновь реверсирует магнитный поток в выходном отверстии трансфлюксора 1, нри этом на выходной обмотке 9 наводится э.д.с., открывающая транзистор 11, на выходе 17 прямого кода появляется импульс. Записанная в трансфлюксоре 1 прямого кода «1 при воздействии входного импульса пе разрушается.

Аналогично, если в трансфлюксоре 2 обратного кода записан «О, а в трансфлюксоре 1 прямого кода - «1, то первый импульс, поступающий на вход 16 обратпого кода, записывает в трансфлюксор 2 обратного кода «1, а в трансфлюксор 1 прямого кода - «О.

Каждый последующий импульс, поданный на вход 16 обратного кода, сформируется на входе 18 обратного кода.

Таким образом, логическое устройство, составленное из указанных ячеек, может быть переведено из одного произвольного состояния в любое другое путем подачи соответствующего числа импульсов на входы прямого и обратного кодов, что и необходимо для построения непрерывного АЦП.

Пусть, например, необходимо изменить состояние логического устройства 1001 на другое 0100 (младший разряд слева). Состояние трансфлюксоров разрядов 19, 24, 25 и 22 - «1, а трансфлюксоров разрядов 23, 20, 21 и 22 - «О. При подаче импульса на вход обратного кода «1 списывается с трансфлюксора разряда 19, таким образом, состояние

логического устройства будет 0001. Следующий импульс, поступивший на вход разрядов обратного кода, устанавливает состояние всех трансфлюксоров разрядов прямого кода в «О, а всех трансфлюксоров обратного кода-в «1. Подача следующих двух импульсов на вход разрядов прямого кода изменяет состояние логического устройства так, что в трансфлюксорах разрядов 19, 20, 25 и 26 записана «1, а

в 21, 22, 23, 24 - «О, после чего состояние логического устройства будет 1100. Подача импульса на вход обратного кода приводит логическое устройство в требуемое состояние 0100, при котором в трансфлюксорах разрядов 20,

23, 25 и 26 записана «1, а в трансфлюксорах разрядов 19, 21, 22 и 24 - «О.

Расчет показывает, что при использовании указанного логического устройства максимальное число тактов отработки равно

п (rt+l)/2, в то время как отработка максимального числа методом единичных приращений при двоичном кодировании требует () тактов, где п - разрядность АЦП.

Предмет изобретения

Логическое устройство, содержащее пятиотверстные трансфлюксоры с обмотками подготовки, входными, считывания, выходными и

сброса, транзисторы и резисторы, отличающееся тем, что, с целью упрощения устройства и повышения его быстродействия, в цепь коллектора транзистора каждого разряда прямого кода включены обмотки записи и считывания прямого кода и сброса обратного кода следующего разряда, а в цепь коллектора транзистора каждого разряда обратного кода включены обмотки записи и считывания обратного кода и сброса прямого кода следующего разряда.

17

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕВЕРСИВНЫЙ ДВОИЧНЫЙ СЧЕТЧИК | 1972 |

|

SU329676A1 |

| МАГНИТНО-ТРАНЗИСТОРНЫЙ КЛЮЧВСЕСОЮЗНАЯMuiim-:i.m'iEmБИ5ЛИО7;^НА | 1972 |

|

SU337945A1 |

| ДВОИЧНЫЙ СЧЕТЧИК | 1970 |

|

SU283300A1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 1970 |

|

SU268494A1 |

| ДЕСЯТИЧНЫЙ СЧЕТЧИК В КОДЕ 1 — 1—2—5 | 1972 |

|

SU353355A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1969 |

|

SU253441A1 |

| АНАЛОГОВОЕ УСТРОЙСТВО ДЛЯ ЗАПОМИНАНИЯ ОДНОКРАТНЫХ ПРОЦЕССОВ | 1972 |

|

SU360695A1 |

| Многоканальное устройство для регистрации информации | 1984 |

|

SU1236452A1 |

| Устройство для преобразования сигнала в двоичный код | 1976 |

|

SU661772A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1969 |

|

SU254886A1 |

Авторы

Даты

1974-07-30—Публикация

1973-04-10—Подача