(54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ СИГНАЛА В ДВОИЧНЫЙ КОД

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ СИГНАЛА В ДВОИЧНЫЙ КОД | 1972 |

|

SU347907A1 |

| Устройство дискретной обработки информации | 1980 |

|

SU884140A1 |

| АНАЛОГОВОЕ УСТРОЙСТВО ДЛЯ ЗАПОМИНАНИЯ ОДНОКРАТНЫХ ПРОЦЕССОВ | 1972 |

|

SU360695A1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 1970 |

|

SU268494A1 |

| УСТРОЙСТВО для СЕЛЕКТИВНОГО ВЫВОДА ИНФОРМАЦИИ ИЗ ПРОВОЛОЧНЫХ ИСКРОВЫХ КАМЕР | 1967 |

|

SU202581A1 |

| УСТРОЙСТВО для ВЫБОРКИ ИНФОРМАЦИИ в АССОЦИАТИВНОЙ НАМЯТИ | 1968 |

|

SU209538A1 |

| МАГНИТНЫЙ В1*ЁМЁННОЙ МОДУЛЯТОР - _ :"^"'гкд | 1971 |

|

SU290283A1 |

| Счетчик импульсов | 1983 |

|

SU1112576A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU310308A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТИ | 1972 |

|

SU338900A1 |

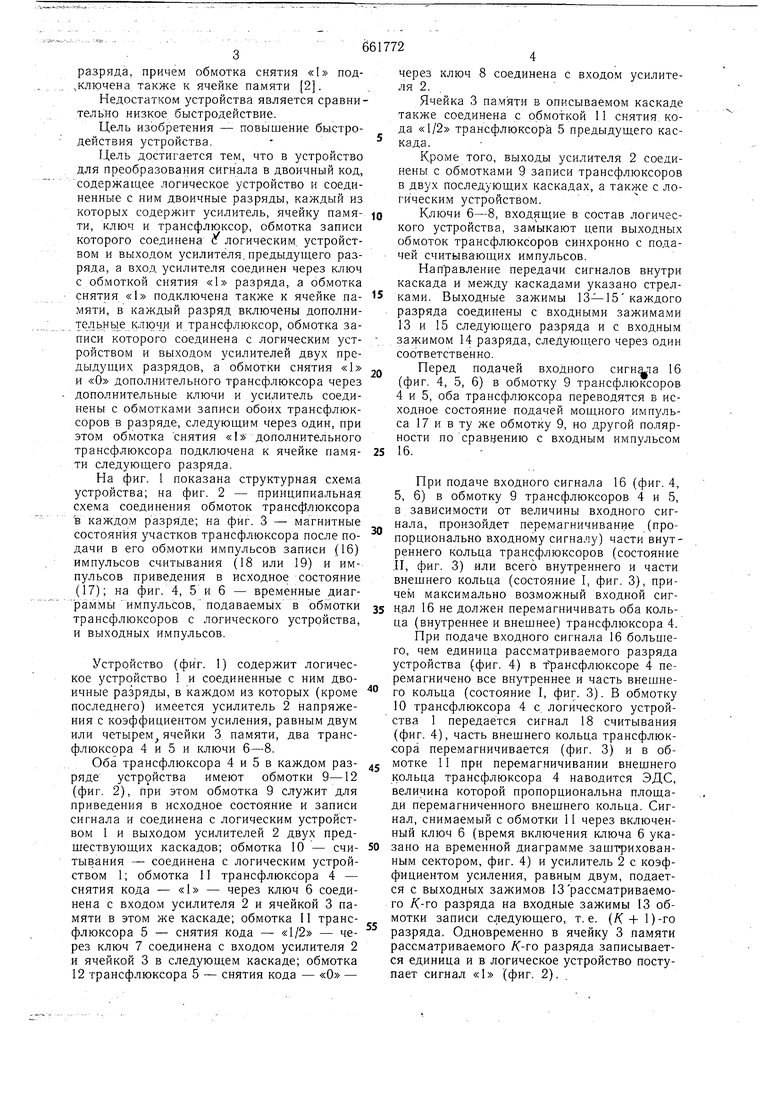

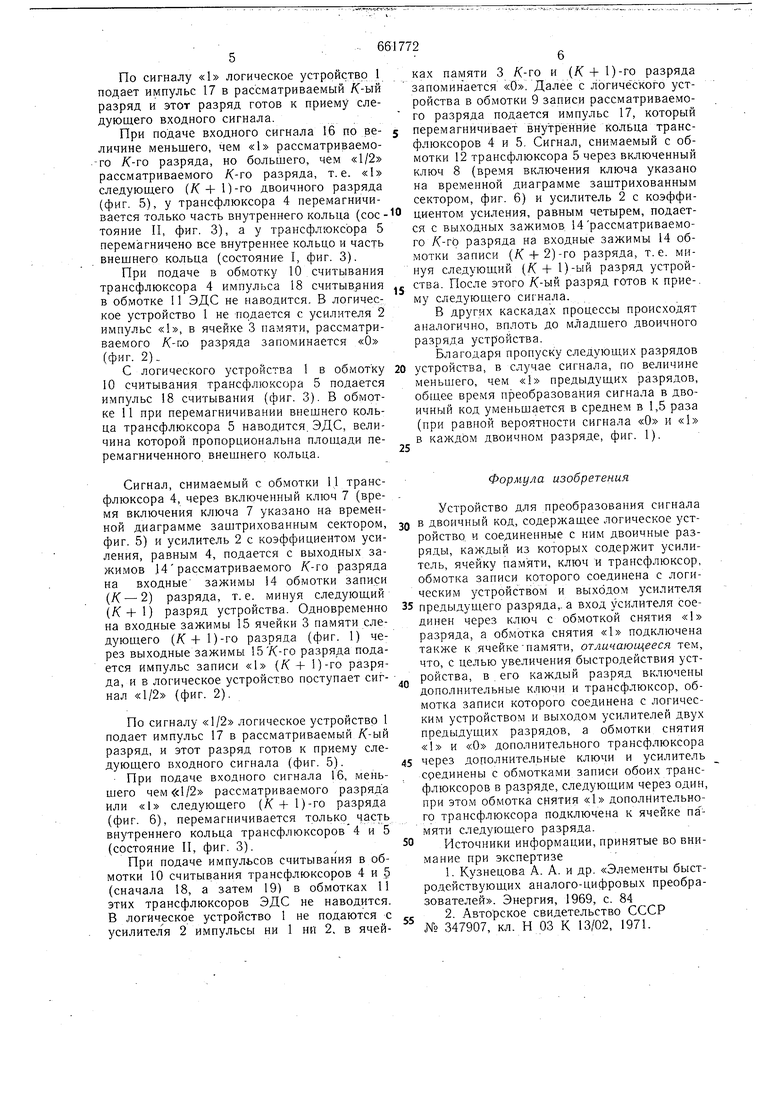

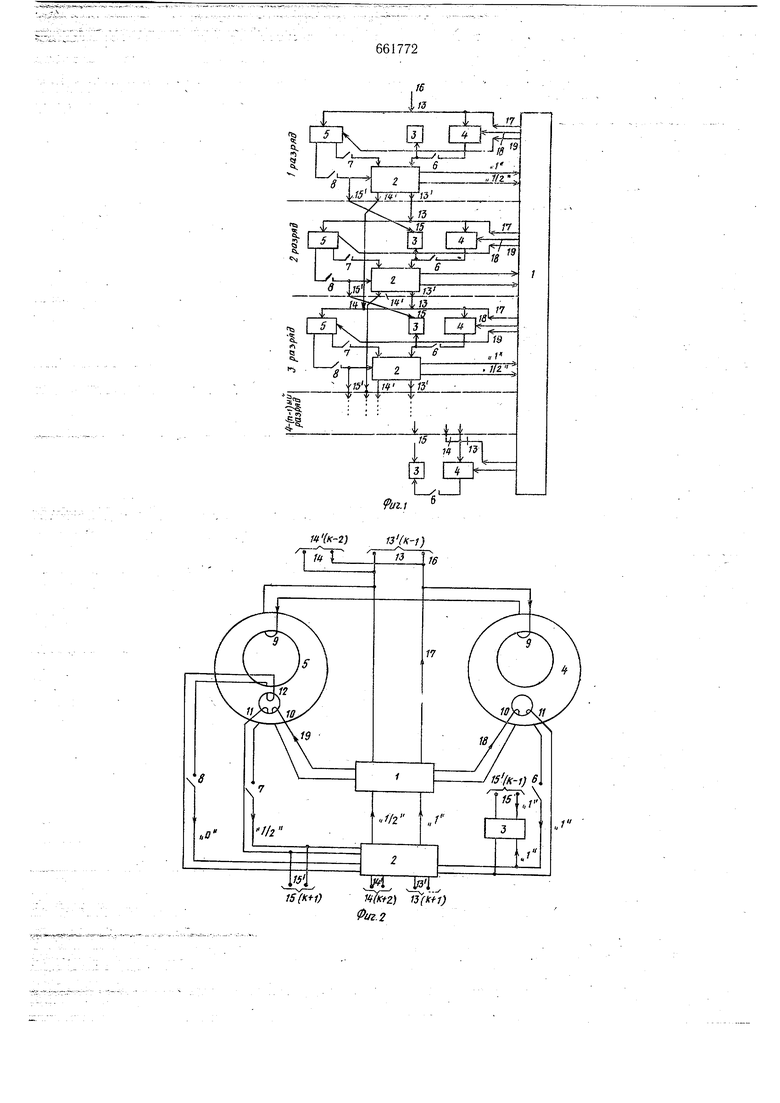

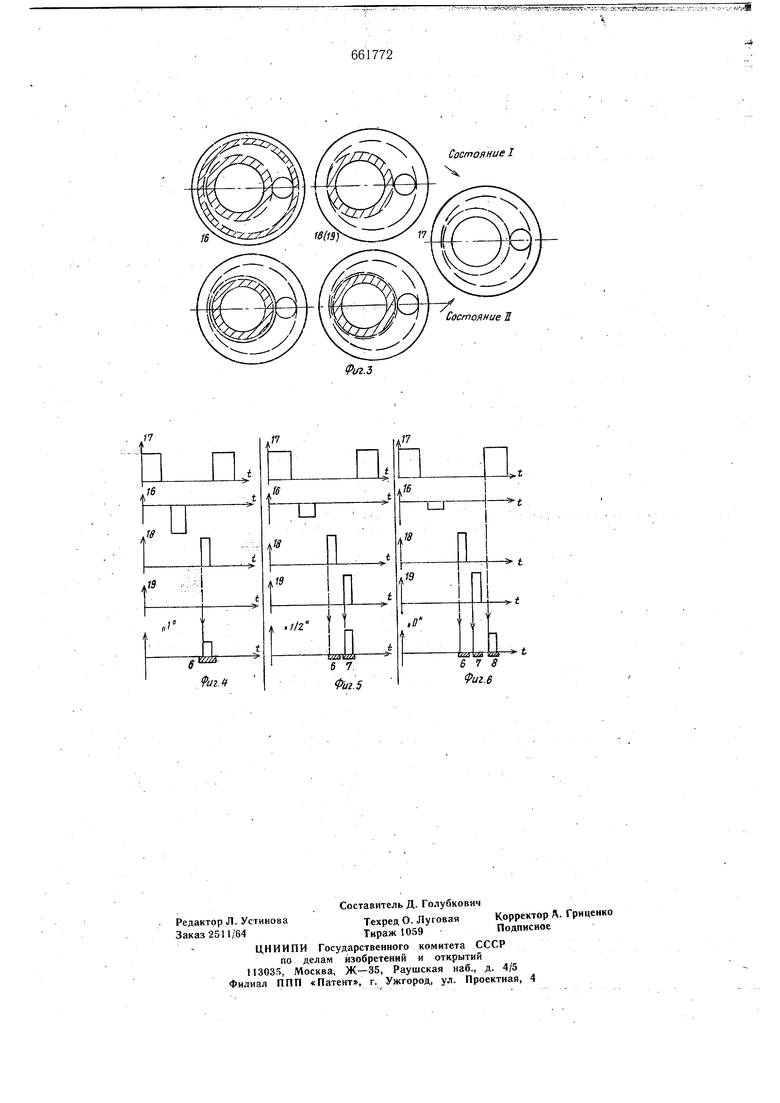

Изобретение относится к устройствам для преобразования электрического сигнала, несущего какую-либо количественную информацию, количественную оценку какой-либо величины в двоичный код, и может быть использовано при разработке элементов и узлов вводных устройств цифровых вычислительных машин, узлов для сопряжения цифровых регуляторов с объектами управления, узлов для сопряже-ния измерительных датчиков с устройствами передачи и хранения информации. Известно устройство для преобразования аналогового электрического сигнала в двоичный код, основанные на методе поразряднога кодирования или на преобразовании напряжения в код через промежуточную величину - время частотосигналрв и . 1, содержащее распределительное устройство, предназначенное для программирования и выполнения временных соотношений в отдельных блоках преобразователя, преобразователь кода в напряжение, состоящий из цифрового регистра на триггерах, ключей, декодирующей сети сопротивлений и источ-. ника эталонного напряжения, компаратор. предназначенный для сравнения двух напряжений: входного сигнала и сигнала с выхода преобразователя кода, и вырабатывающий входной сигнал управления. Недостатком известного устройства является большое количество элементов, что уменьшает надежность и быстродействие работы устройства. Известно устройство для преобразования сигнала в двоичный код, основанное на преобразовании электрического сигнала в магнитопроводах с разветвленной магнитной цепью (трансфлюксорах) в пропорциональное перемагничивание материала магнитопровода с одновременным его разделением на части, соответствующие двоичным разрядамЭто устройство содержит логическое устройство и соединенные с ним двоичные разряды, каждый из которых содержит усилитель, ячейку памяти, ключ и трансфлюксор, обмотка записи которого соединена с логическим устройством и выходом усилителя предыдущего разряда, а вход усилителя соединен через ключ с обмоткой снятия «1 разряда, причем обмотка снятия «1 под.ключена также к ячейке памяти 2. Недостатком устройства является сравнительно низкое быстродействие. Цель изобретения - повышение быстродействия устройства.Цель достигается тем, что в устройство для преобразования сигнала в двоичный код, содержащее логическое устройство и соединенные с ним двоичные разряды, каждый из которых содержит усилитель, ячейку памяти, ключ и трансфлюксор, обмотка записи которого соединена с логическим, устройством и выходом усилителя, предыдущего разряда, а вход усилителя соединен через ключ с обмоткой снятия «1 разряда, а обмотка снятия «1 подключена также к ячейке памяти, в каждый разряд включены дополните л ьньш ключи и трансфлюксор, обмотка записи которого соединена с логическим устройством и выходом усилителей двух предыдущих разрядов, а обмотки снятия «1 и «О дополнительного трансфлюксора через дополнительные ключи и усилитель соединены с обмотками записи обоих трансфлюксоров в разряде, следующим через один, при этом обмотка снятия дополнительного трансфлюксора подключена к ячейке памяти следующего разряда. На фиг. I показана структурная схема устройства; на фиг. 2 - принципиальная схема соединения обмоток трансфлюксора в каждом разряде; на фиг. 3 - магнитные состояния участков трансфлюксора после подачи в его обмотки импульсов записи (16) импульсов считывания (18 или 19) и импульсов приведения в исходное состояние (17); на фиг. 4, 5 и 6 - временные диаграммы импульсов, подаваемых в обмотки трансфлюксоров с логического устройства, и выходных импульсов. Устройство (фиг. 1) содержит логическое устройство 1 и соединенные с ним двоичные разряды, в каждом из которых (кроме последнего) имеется усилитель 2 напряжения с коэффициентом усиления, равным двум или четырем ячейки 3 памяти, два трансфлюксора 4 и 5 и ключи 6-8. Оба трансфлюксора 4 и 5 в каждом разряде устройства имеют обмотки 9-12 (фиг. 2), при этом обмотка 9 служит для приведения в исходное состояние и записи сигнала и соединена с логическим устройством 1 и выходом усилителей 2 двух предшествующих каскадов; обмотка 10 - считывания - соединена с логическим устройством 1; обмотка 11 трансфлюксора 4 - снятия кода - «1 - через ключ 6 соединена с входом усилителя 2 и ячейкой 3 памяти в этом же каскаде; обмотка 11 трансфлюксора 5 - снятия кода - «1/2 - через ключ 7 соединена с входом усилителя 2 и ячейкой 3 в следующем каскаде; обмотка 12 трансфлюксора 5 - снятия кода - «О - через ключ 8 соединена с входом усилителя 2. Ячейка 3 памяти в описываемом каскаде также соединена с обмоткой 11 снятия, кода «1/2 трансфлюксора 5 предыдущего каскада. Кроме того, выходы усилителя 2 соединены с обмотками 9 записи трансфлюксоров в двух последующих каскадах, а также с логическим устройством. Ключи 6-8, входящие в состав логического устройства, замыкают цепи выходных обмоток трансфлюксоров синхронно с подачей считывающих импульсов. Направление передачи сигналов внутри каскада и между каскадами указано стрелками. Выходные зажимы 13 15каждого разряда соединены с входными зажимами 13 и 15 следующего разряда и с входным зажимом 14 разряда, следующего через один соответственно. Церед подачей входного 16 (фиг. 4, 5, 6) в обмотку 9 трансфлюксоров 4 и 5, оба трансфлюксора переводятся в исходное состояние подачей мощного импульса 17 и в ту же обмотку 9, но другой полярности но сравнению с входным импульсом 16. При подаче входного сигнала 16 (фиг. 4, 5, 6) в обмотку 9 трансфлюксоров 4 и 5, в зависимости от величины входного сигнала, произойдет перемагничивание (пропорционально входному сигналу) части внутреннего кольца трансфлюксоров (состояние .II, фиг. 3) или всего внутреннего и части внешнего кольца (состояние I, фиг. 3), причем максимально возможный входной сигнал 16 не должен перемагничивать оба кольца (внутреннее и внешнее) трансфлюксора 4. При подаче входного сигнала 16 большего, чем единица рассматриваемого разряда устройства (фиг. 4) в трансфлюксоре 4 перемагничено все внутреннее и часть внешнего кольца (состояние I, фиг. 3). В обмотку 10 трансфлюксора 4 с логического устройства 1 передается сигнал 18 считывания (фиг. 4), часть внешнего кольца трансфлюксора перемагничивается (фиг. 3) и в обмотке 11 при неремагничивании внешнего кольца трансфлюксора 4 наводится ЭДС, величина которой пропорциональна площади перемагниченного внешнего кольца. Сигнал, снимаемый с обмотки 11 через включенный ключ 6 (время включения ключа 6 указано на временной диаграмме заштрихованным сектором, фиг. 4) и усилитель 2 с коэффициентом усиления, равнь1м двум, подается с выходных зажимов 13рассматриваемого /С-го разряда на входные зажимы 13 обмотки записи следующего, т.е. (К + 1)-го разряда. Одновременно в ячейку 3 памяти рассматриваемого /С-го разряда записывается единица и в логическое устройство поступает сигнал «1 (фиг. 2). По сигналу «1 логическое устройство 1 подает импульс 17 в рассматриваемый /С-ый разряд и этот разряд готов к приему следующего входного сигнала. При подаче входного сигнала 16 по величине меньшего, чем «1 рассматриваемого /С-го разряда, но большего, чем «1/2 рассматриваемого К-го разряда, т.е. «I следующего (/Сч-1)-го двоичного разряда (фиг. 5), у трансфлюксора 4 перемагничивается только часть внутреннего кольца (соетояние II, фиг. 3), а у трансфлюксора 5 перем;агничено все внутреннее кольцо и часть внешнего кольца (состояние I, фиг. 3). При подаче в обмотку 10 считывания трансфлюксора 4 импульса 18 считыв ания в обмотке 11 ЭДС не наводится. В логическое устройство 1 не подается с усилителя 2 импульс «1, в ячейке 3 памяти, рассматриваемого /С-г.о разряда запоминается «О (фиг. 2). С логического устройства 1 в обмотку 10 считывания трансфлюксора 5 подается импульс 18 считывания (фиг. 3). В обмотке 11 при перемагничивании внешнего кольца трансфлюксора 5 наводится. ЭДС, величина которой пропорциональна перемагниченного внешнего кольца. Сигнал, снимаемый с обмотки 1.1 трансфлюксора 4, через включенный ключ 7 (время включения ключа 7 указано на временной диаграмме заштрихованным сектором, фиг. 5) и усилитель 2 с коэффициентом усиления, равным 4, подается с выходных зажимов 14рассматриваемого /С-го разряда на входные зажимы 4 обмотки записи (/(- 2) разряда, т.е. минуя следующий (К + ) разряд устройства. Одновременно на входные зажимы 15 ячейки 3 памяти следующего (К + 1)-го разряда (фиг. 1) через выходные зажимы 15/(-го разряда подается импульс записи «1 (К + 1)-го разряда, и в логическое устройство поступает сигнал «1/2 (фиг. 2). По сигналу «1/2 логическое устройство 1 подает импульс 17 в рассматриваемый /С-ый разряд, и этот разряд готов к приему следующего входного сигнала (фиг. 5). При подаче входного сигнала 16, меньшего чем «1/2 рассматриваемого разряда или «I следующего (/(+1)-го разряда (фиг. 6), перемагничивается только часть внутреннего кольца трансфлюксоров 4 и 5 (состояние II, фиг. 3). При подаче импульсов считывания в обмотки 10 считывания трансфлюксоров 4 и 5 (сначала 18, а затем 19) в обмотках И этих трансфлюксоров ЭДС не наводится. В логическое устройство 1 не подаются с усилителя 2 импульсы ни 1 НИ 2, в ячейках памяти 3 /(-го и (/Сч- 1)-го разряда запоминается «О. Далее с логиче ского устройства в обмотки 9 записи рассматриваемого разряда подается импульс 17, который перемагничивает внутренние кольца трансфлюксоров 4 и 5. Сигнал, снимаемый с обмотки 12 трансфлюксора 5 через включенный ключ 8 {время включения ключа указано на временной диаграмме заштрихованным сектором, фиг. 6) и усилитель 2 с коэффициентом усиления, равным четырем, подается с выходных зажимов 14рассматриваемого /С-гО разряда на входные зажимы 14 обмотки записи (К. + 2)-го разряда, т.е. минуя следующий (К + 1)-ый разряд устройства. После этого К-ът разряд готов к приему следующего сигнала. В других каскадах процессы происходят аналогично, вплоть до младшего двоичного разряда устройства. Благодаря пропуску следующих разрядов устройства, в случае сигнала, по величине меньшего, чем «1 предыдущих разрядов, общее время преобразования сигнала в двоичный код уменьщается в среднем в 1,5 раза (при равной вероятности сигнала «О и «Ь в каждом двоичном разряде, фиг. 1). Формула изобретения Устройство для преобразования сигнала в двоичный код, содержащее логическое устройство и соединенные с ним двоичные разряды, каждый из которых содержит усилитель, ячейку памяти, ключ и трансфлюксор, обмотка записи которого соединена с логическим устройством и выходом усилителя предыдущего разряда,, а вход усилителя соединен через ключ с обмоткой снятия «1 разряда, а обмотка снятия «1 подключена также к .ячейкеПамяти, отличающееся тем, что, с целью увеличения быстродействия устройства, в . его каждый разряд включены дополнительные ключи и трансфлюксор, обмотка записи которого соединена с логическим устройством и выходом усилителей двух предыдущих разрядов, а обмотки снятия «1 и «О дополнительного трансфлюксора через дополнительные ключи и усилитель соединены с обмотками записи обоих трансфлюксоров в разряде, следующим через один, при этом обмотка снятия «1 дополнительного трансфлюксора подключена к ячейке памяти следующего разряда. Источники информации, принятые во внимание при экспертизе 1.Кузнецова А. А. и др. «Элементы быстродействующих аналого-цифровых преобразователей. Энергия, 1969, с. 84 2.Авторское свидетельство СССР № 347907, кл. Н 03 К 13/02, 1971.

ПЧк-2}13(К1)

ТлЕг %г./

ж

W/Ar/2) Is cm-i) Фиг. 2

(Pui.Z

Состояние I

Авторы

Даты

1979-05-05—Публикация

1976-02-02—Подача