Изобретение относится к области автоматики и может быть использовано в система.ч преобразования сигналов, автаподстройки, измерительных комплексах, цифровых автоматических приборах.

Известны мно.гочастотные имлульсные дискриминаторы, содержащие линию задержки, схемы совладения и логическую схему.

Недостатком известных дискриминаторов являются невысокая надежность работы и ллохие динамические свойства.

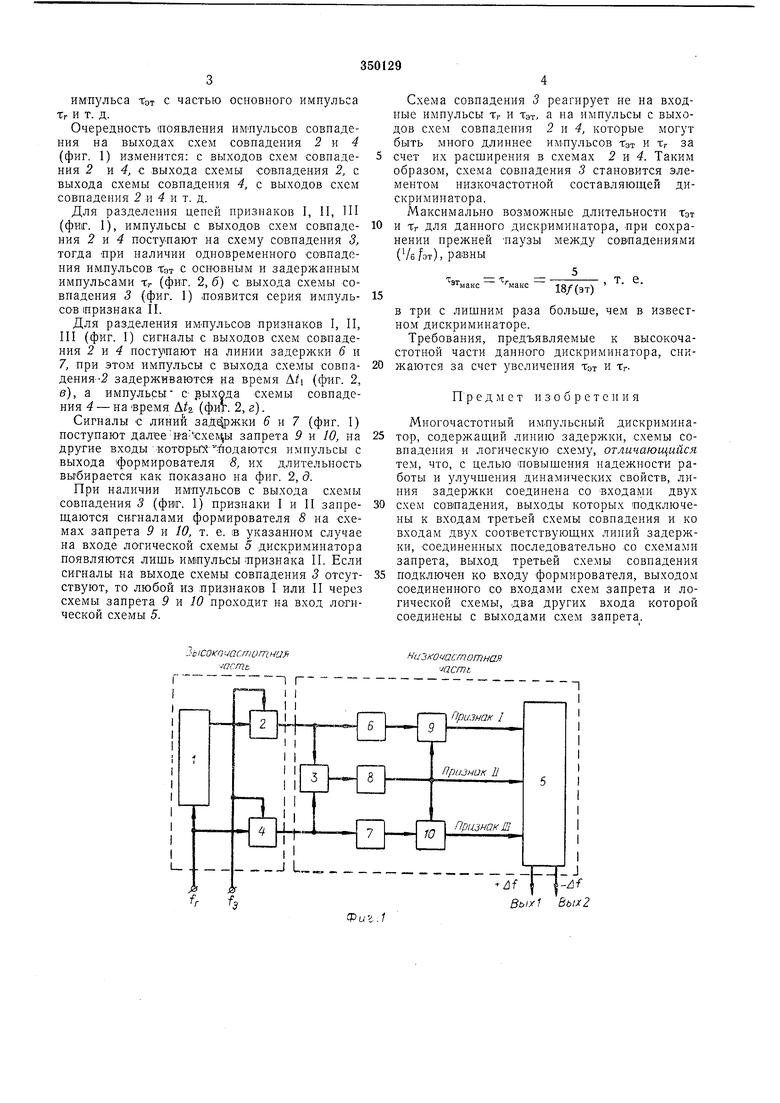

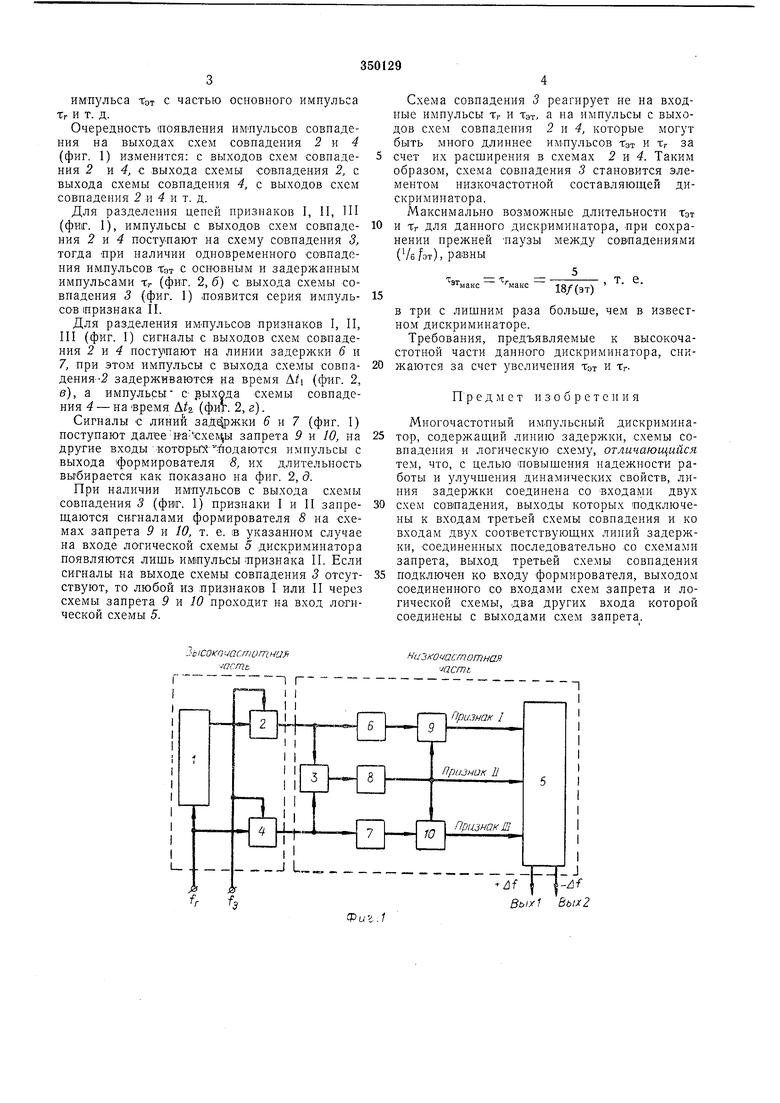

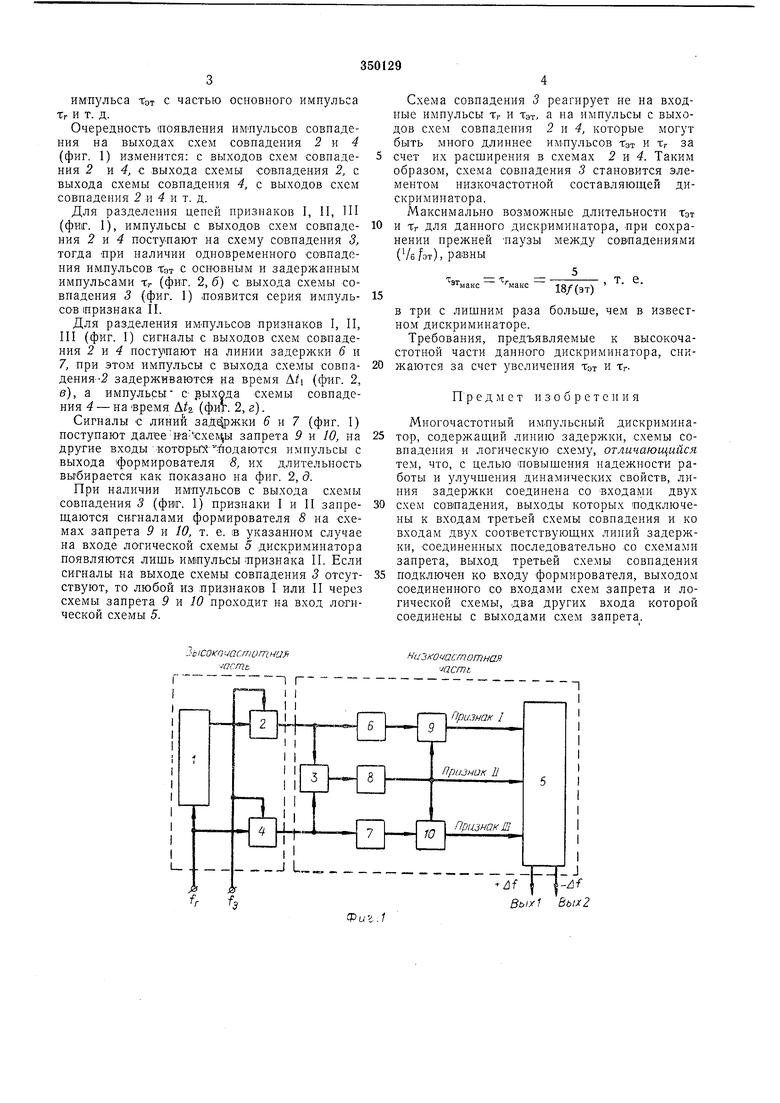

С целью повышения надежности работы и улучшения динамических свойств в предлагаемом устройстве линия задержки соединена со входами двух схем совпадения, выходы которых подключены ко входам третьей схемы совпадения и ко входам двух соответствующих линий задержки, соединенных последовательно со схемами запрета, выход третьей схемы совпадения подключен ко входу формирователя, выходом соединенного со входами схем запрета и логической схемы, два других входа которой соединены с выходами схем залрета.

На фиг. 1 изображена блок-схема предлагаемого дискриминатора; на фиг. 2 - временные диаграммы.

нии задержки 6 и 7, формирователь 8 и схемы запрета 9 и 10.

Импульсная последовательность /г поступает на вход линии задержки / и схему совпадения 4. С выхода линии задержки 1 задержанные на время А/ (фиг. 2, б) имлульсы т,, поступают на схему совпадения 2. На другие входы схем совпадения 2 н 4 подаются импульсы частотой /этПри отклонении от кратности частот fr и /зт в большую сторону (как видно из фиг. 2, б) произойдет последовательное совмещение:

имлульса Тэт с основными и задержанными импульсами Тг;

импульса Тэт с частью основного имлульса Тг;

имлульса Тэт с частью задержанного импульса Тг и т. д.

Таким образом, импульсы совпадения следуют поочередно: с выходов схем сов-падения 2 и 4 (фиг. 1), с выхода схемы совпадения 4, с выхода схемы совпадения 2, с выходов схем совпадения 2 н 4 и т. д.

При отклонении от кратности частот /эт и fr в меньшую сторону лроизойдет последовательное совмещение:

импульса Тэт с частью основного импульса

Тг и т. д.

Очередность (появления импульсов совпадения на выходах схем совпадения 2 и 4 (фиг. 1) изменится: с выходов схем совпадения 2 и 4, -с выхода схемы совладения 2, с выхода схемы совпадения 4, с выходов схем совладения 2 и 4 и т. д.

Для разделения цеией признаков I, II, П1 (фиг. 1), импульсы с выходов схем совпадения поступают на схему совпадения 3, тогда яри наличии одновременного совпадения имлульсов Тэт с основным и задержанным импульсами Тг (фиг. 2, б) с выхода схемы совпадения 3 (фиг. 1) появится серия импульсов признака II.

Для разделения импульсов признаков I, II, III (фиг. 1) сигналы с выходов схем совпадения 2 W 4 поступают на линии задержки 6 и 7, при этом импульсы с выхода схемы совпадения--2 задерживаются на время Д/i (фиг. 2, в), а импульсы- с- выхода схемы совпадения 4 - на время Л/2, (фиг. 2, г).

Сигналы с линий заДфжки б и 7 (фиг. 1) поступают далеен-а-схел ы запрета 9 и W, на другие входы которыхподаются импульсы с выхода формирователя 8, их длительность выбирается как показано на фиг. 2, д.

При наличии импульсов с выхода схемы совпадения 3 (фиг. 1) признаки I и II запрещаются сигналами формирователя 8 на схемах запрета 9 и 10, т. е. в указанном случае на входе логической схемы 5 дискриминатора появляются лишь импульсы признака II. Если сигналы на выходе схемы совпадения 3 отсутствуют, то любой из признаков I или II через схемы запрета 9 тл 10 проходит на вход логической схемы 5.

Jb ICOKO ijocmom n/jfi

-асть I1 ГСхема совпадения 3 реагирует не на входные импульсы Тг и Тэт. а на импульсы с выходов схем совпадения 2 и 4, которые могут быть много длиннее импульсов Тэт и Тг за счет их расширения в схемах 2 и 4. Таким образом, схема совпадения 3 становится элементом низкочастотной составляющей дискриминатора.

Максимально возможные длительности Тат и Тг для данного дискриминатора, при сохранении прежней иаузы между совпадениями (/6/от), равиы

Т. е.

Т

иакс макс

18/(эт)

в три с лишним раза больше, чем в известном дискриминаторе.

Требования, предъявляемые к высокочастотной части данного дискриминатора, снижаются за счет увеличения Тэт и Тг.

Предмет изобретения

Многочастотный импульсный дискриминатор, содержащий линию задержки, схемы совпадения и логическую схему, отличающийся тем, что, с целью повышения надежности работы и улучшения динамических свойств, линия задержки соединена со входами двух схем совпадения, выходы которых подключены к входам третьей схемы совпадения и ко входам двух соответствующих линий задержки, соединенных последовательно со схемами запрета, выход третьей схемы совпадения подключен ко входу формирователя, выходом соединенного со входами схем запрета и логической схемы, два других входа которой соединены с выходами схем запрета.

изко1 ас/потная -lacmt.

-

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1973 |

|

SU379977A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ ИМПУЛЬСОВ РЕВЕРСИВНОГО СЧЕТЧИКА | 1969 |

|

SU236537A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА ЧИСЛА В ПОСЛЕДОВАТЕЛЬНОСТЬИМПУЛЬСОВ | 1970 |

|

SU272669A1 |

| СЕЛЕКТОР ПЕРИОДИЧЕСКОЙ ПОСЛЕДОВАТЕЛЬНОСТИИМПУЛЬСОВ | 1968 |

|

SU209052A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ ИМПУЛЬСОВ | 1971 |

|

SU311396A1 |

| Калибратор частот | 1976 |

|

SU708254A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОРТОГОНАЛЬНОСТИ | 1970 |

|

SU284166A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ПАРАМЕТРОВ | 1972 |

|

SU357850A1 |

| УСТРОЙСТВО ДЛЯ ЛОГИЧЕСКОЙ ОБРАБОТКИ ОТВЕТНЫХ СИГНАЛОВ | 1970 |

|

SU259132A1 |

| Устройство для задержки импульсов | 1979 |

|

SU822331A1 |

fr f,

Вых1 Вык2

Даты

1972-01-01—Публикация