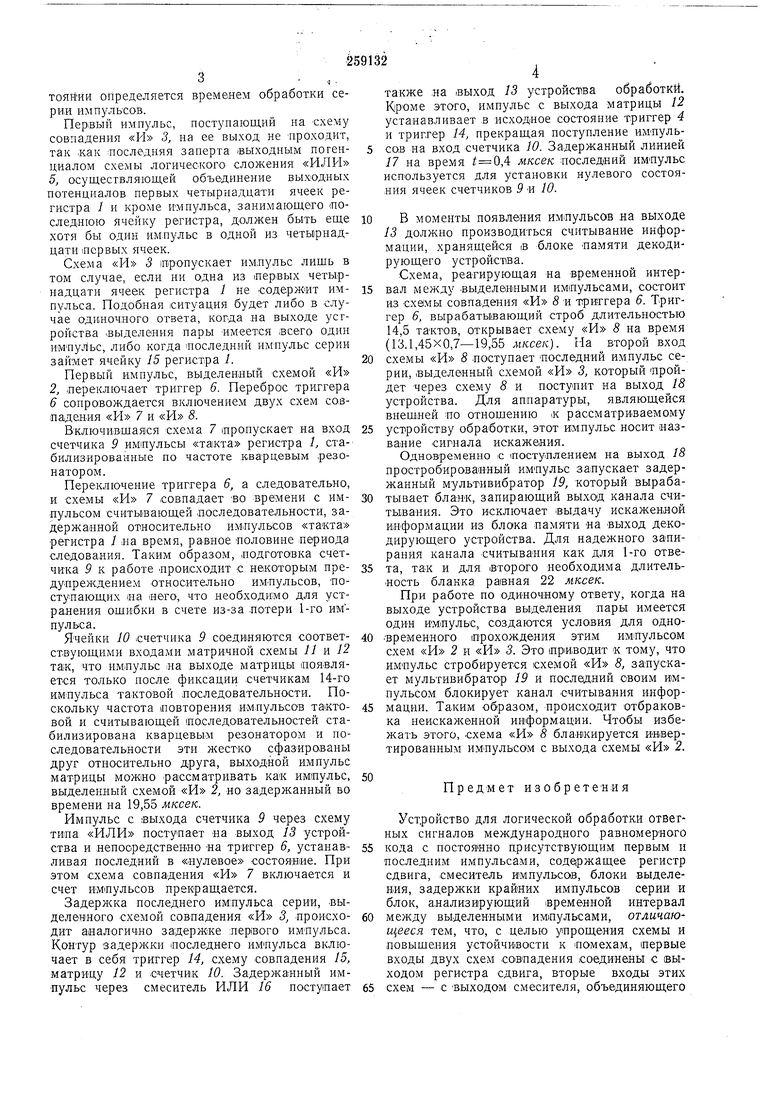

Известны уст:ройства логической обработки ответных сигналов международного равномерного кода с .постоянно присутствующим первым и -последним имл-улисами, содержащее регистр сдвига, смеситель импульсов, блоки выделения, задерЖКи крайних импульсов серии и блока, анализирующий временной интервал между -выделеняыми импульсами. Особенностью описываемого устройства является простота схемы (один «акопитель вместо двух буферных), а также оовыщенная устойчивость к помехам, обеспечиваемая тем. что схема выделения ,не срабатывает от одиночного импульса и высокой разрещающей способностью декодера, обладающего независимостью обработки от базы сигнала. Эти свойства схемы достигаются соответствующим соединением элементов устройства: первые входы двух схем совпадения соединены с выходам регистра сдвига, вторые входы этих схем - с выходом смесителя, объединяющего выходы регистра, и с выходом триггера, яри этом .первый вход третьей схемы совладения соединен с выходам схемы выделения последнего имиульса, а .второй вход - с выходом строба фиксированной схемы ооразования длительности. Работа устройства проходит следующим образом. При определенных условиях «а вход устройства логической обработки иоступает серия импульсов протяженностью 1,45- 40,6 мксек. Количество импульсов серии и ее .протяженность зависят от содержания информации обоих ответов и от их взаимного расположения на оси времени. Задача устройства логической обработки сигналов состоит в подавлении всех внутренних импульсов серии независимо от длины последней и в 1выработке сигнала искажения, указывающего на взаимодейтвие ответных пачек, что Приводит к искажению передаваелюй информации. При этом должен вырабатываться и.мпульс, бланкирующий цепь считывания специнформации как лервого, так и второго ответов. Первый импульс серии с выхода .регистра 1 поступает на -входы схемы совпадения «И 2 и «И 3. Второй вход схемы 2 получает «отпирающий потенииал с выхода триггера 4. С выхода схемы «И 2 первый импульс серии поступает на дифференцирующую цепь и после дифтференцирования своим задним фронтом переключает триггер 4 во второе устойчивое состояние, которому соответствует выключенное состояние схемы «И 2. Длительность пребывания схемы «И 2 в выключенном соетоянии определяется временем обработки серии импульсов.

Первый импульс, поступающий на схему совпадения «И 3, на ее выход не проходит, так .как ;последняя заперта 1выходным по генциалом схемы логического сложения «ИЛИ 5, осуществляющей объединение выходных потенциалов первых четырнадцати ячеек регистра 1 и кроме импульса, занимающего (последнюю ячейку регистра, должен быть еще хотя бы один импульс в одной из четырнадцати лервых ячеек.

Схема «PI 3 лропускает имлульс лишь в том случае, если ни одна из inepiBbix четырнадцати ячеек регистра / не содержит импульса. Подобная ситуация будет либо в случае одиночного ответа, когда ,на выходе устройства .выделения пары «меется (Всего один импуЛьс, либо когда последний импульс серии займет ячейку 15 регистра I.

Первый импульс, выделенный схемой «И 2, .переключает триггер 6. Переброс триггера 6 сонровождается включением двух схем совпадения «И 7 и «И 8.

Включившаяся схема 7 пропускает на вход счетчика 9 им1пульсы «такта регистра 1, стабилизированные по частоте кварцевым резонатором.

Переключение триггера 6, а следовательно, и схемы «И 7 совпадает БО времени с импульсом считывающей .последовательности, задержанной относительно им:пульсов «такта регистра 1 иа время, равное половине периода следова.ния. Таким образом, подготовка счетчика 9 к работе происходит с некоторым предупреждением относительно импульсов, поступающих иа него, что необходимо для устранения ошибки в счете из-за .потери 1-го импульса.

Ячейки 10 счетчика 9 соединяются соответствующими входами матричной схемы И и 12 так, что импульс ла выходе матрицы появляется только после фиксации счетчикам 14-го импульса тактовой последовательности. Поскольку частота повторения импульсов тактовой и считывающей последовательностей стабилизирована кварцевым резонатором и последовательности эти жестко сфазяроваиы друг относительно друга, выходной импульс матрицы можно рассматривать как имоульс, выделенный схемой «И 2, но задержанный во времени на 19,55 мксек.

Имиульс с выхода счетчика 9 через схему типа «ИЛИ поступает на выход 13 устройства и .непооредствеБно на триггер 6, устанавливая последний в «нулевое состояние. При этом схема совпа.дения «И 7 включается и счет импульсов прекращается.

Задержка последнего импульса серии, .выделенного схемой совпадения «И 3, происходит аналогично задержке nepiBoro импульса. Контур задержки 1последнего имлульса включает в себя триггер 14, схему совпадения 15, матрицу 12 и .счетчик 10. Задержанный импульс через смеситель ИЛИ 16 поступает

также на выход 13 устройства обработки. Кроме этого, импульс с выхода матрицы 12 устанавливает в исходное состояние триггер 4 и триггер 14, прекращая поступление имлульCQB на вход счетчика 10. Задержанный линией 17 на время ,4 мксек последний импульс используется для установки нулевого состоя.ния ячеек счетчиков 9 « W.

В моменты появления импульсов на выходе 13 должно производиться считывание информании, хранящейся в блоке памяти декодирующего устройства.

Схема, реагирующая на временной интервал между выделенными импульсами, состоит из схемы совпадения «И 8 н триггера 6. Триггер 6, вырабатывающий строб длительностью 14,5 тактов, открывает схему «И 8 на время (13.1,45x0,7-19,55 мксек). На второй вход схемы «И 8 поступает последний импульс серии, выделенный схемой «И 3, который пройдет через схему 8 и поступит на выход 18 устройства. Для аппаратуры, являющейся внешней по отношению к рассматриваемому устройству обработки, этот импульс носит название сигнала искажения.

Одновременно ic поступлением на выход 18 простробированный импульс за:пускает задержанный мультивибратор 19, который вырабатывает бланк, запирающий выход канала считывания. Это исключает выдачу искаженной информации из блока памяти на выход декодирующего устройства. Для надежного запирания канала считывания как для 1-го ответа, так и для второго необходима длительность бланка равная 22 мксек.

При работе по одиночному ответу, когда на выходе устройства выделения пары имеется один Импульс, создаются условия для одно.временного прохождения этим импульсом схем «И 2 и «И 3. Это приводит к тому, что импульс стробируется схемой «И 8, запускает мультивибратор 19 и последний своим импульсом блокирует канал считывания информации. Таким образом, происходит отбраковка неискаженной информации. Чтобы избежать этого, схема «И 8 бла.нкируется инвертированным импульсом с выхода схемы «И 2.

Предмет изобретения

Устройство для логической обработки ответных сигналов международного равномерного кода с постоянно присутствующим первым и последним импульса.ми, соде|ржащее регистр сдвига, смеситель импульсов, блоки выделения, задержки крайних импульсов серии и блок, а.нализи1рующий временной интервал между вы.деленными импульсами, отличающееся тем, что, с целью упрощения схемы и повышения устойчивости к помехам, первые входы двух схем совпадения соединены с выходом регистра сдвига, вторые входы этих схем - с выходом смесителя, объединяющего 5 выходы регистра, и с выходом триггера; при ITOM первый вход третьей схемы совпадения юединен с выходом схемы выделения послед2591326 него импульса, а второй вход - с выходом схемы образования строба фиксирован-ной длительности.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВАЯ СЕЙСМОРАЗВЕДОЧНАЯ СТАНЦИЯ | 1973 |

|

SU396648A1 |

| Устройство для ввода информации | 1980 |

|

SU951282A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство управления режимом работы синхрогенератора | 1985 |

|

SU1322504A1 |

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1524082A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1987 |

|

SU1437870A2 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ РАЗНОСТИ ДВУХ ЧИСЕЛ | 1966 |

|

SU179990A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ | 2011 |

|

RU2474043C1 |

| Устройство для сопряжения источников информации с вычислительной машиной | 1984 |

|

SU1179358A1 |

| УСТРОЙСТВО для СБОРА И ПЕРЕДАЧИ ИНФОРМАЦИИ | 1971 |

|

SU294163A1 |

Даты

1970-01-01—Публикация