Изобретение относится к вычислительной технике.

Устройство может быть использовано для предварительного умножения частотно-импульсных сигналов на коэффициент, больший единицы, с целью увеличения статической и динамической точности лоследующих частотомеров, а также в качестве масштабного блока в частотно-импульсных арифметических устройствах.

Известны умножители частотно-импульсных сигналов, содержащие делитель частоты и реверсивный счетчик, соединенный через преобразователь «код-напряжение с управляемым генератором частоты.

Цель изобретения - повышение динамической точности. Достигается она тем, что предлагаемый умножитель частотно-импульсных сигналов содержит блок временной раздвижки ИмпульсоВ, блок задержки входных импульсов, блок выделения разности периодов, коммутирующий триггер и схемы совпадения, причем выход делителя частоты соединен со входаМИ блока задержки и одним входом коммутирующего триггера, второй вход которого подключен к выходу блока задержки. Выход блока временной раздвижки импульсов соединен со входом блока задержки и одним входом блока выделеиия разности периодов, другой вход которого соединен с выходом

делителя частоты. Выходы блока выделения разности периодов соединены с первыми входами двух схем совпадения, вторые входы которых подключены к выходу управляемого генератора частоты, а выходы схем совпадения подключены ко входам реверсивного счетчика. Выход управляемого генератора частоты соединен также с одним входом третьей схемы совпадения, другой вход которой подключен к выходу коммутирующего триггера, а выход - ко входу делителя частоты.

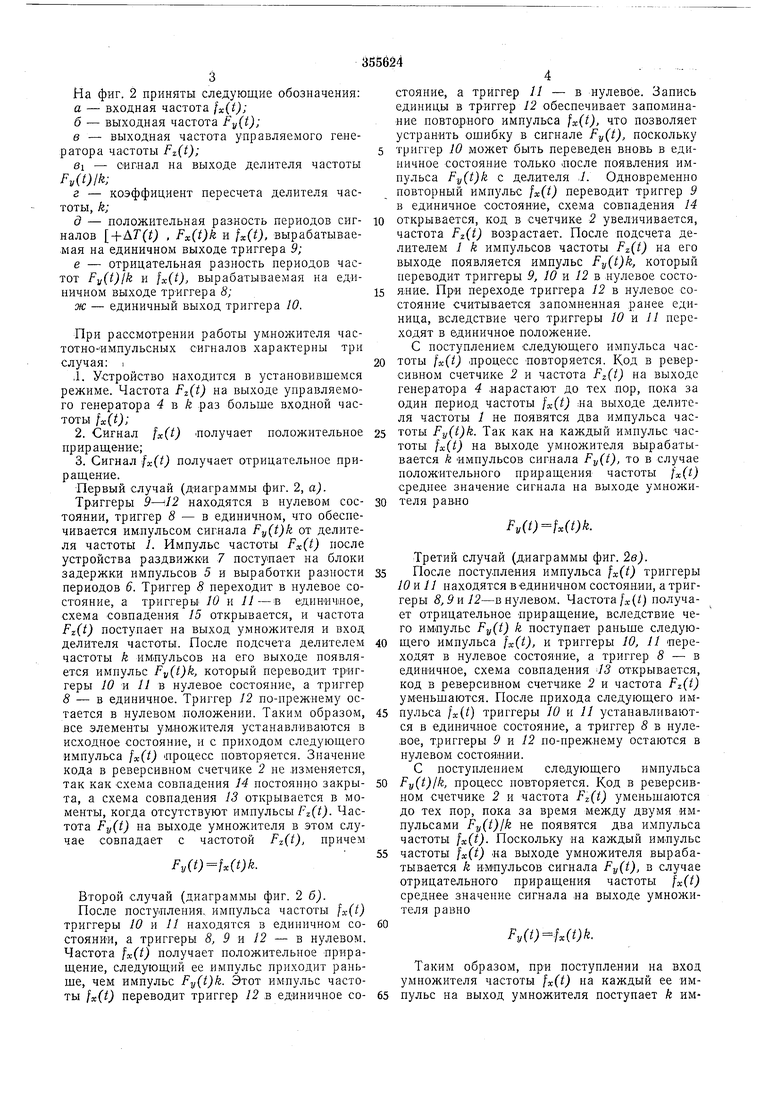

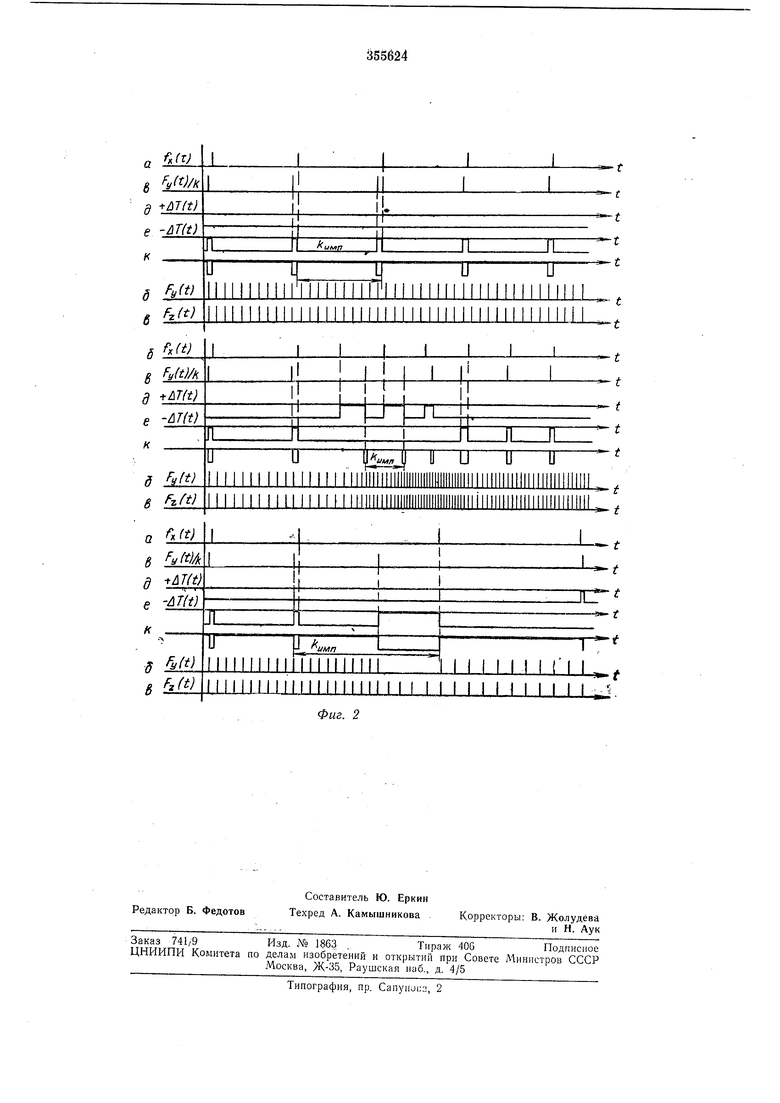

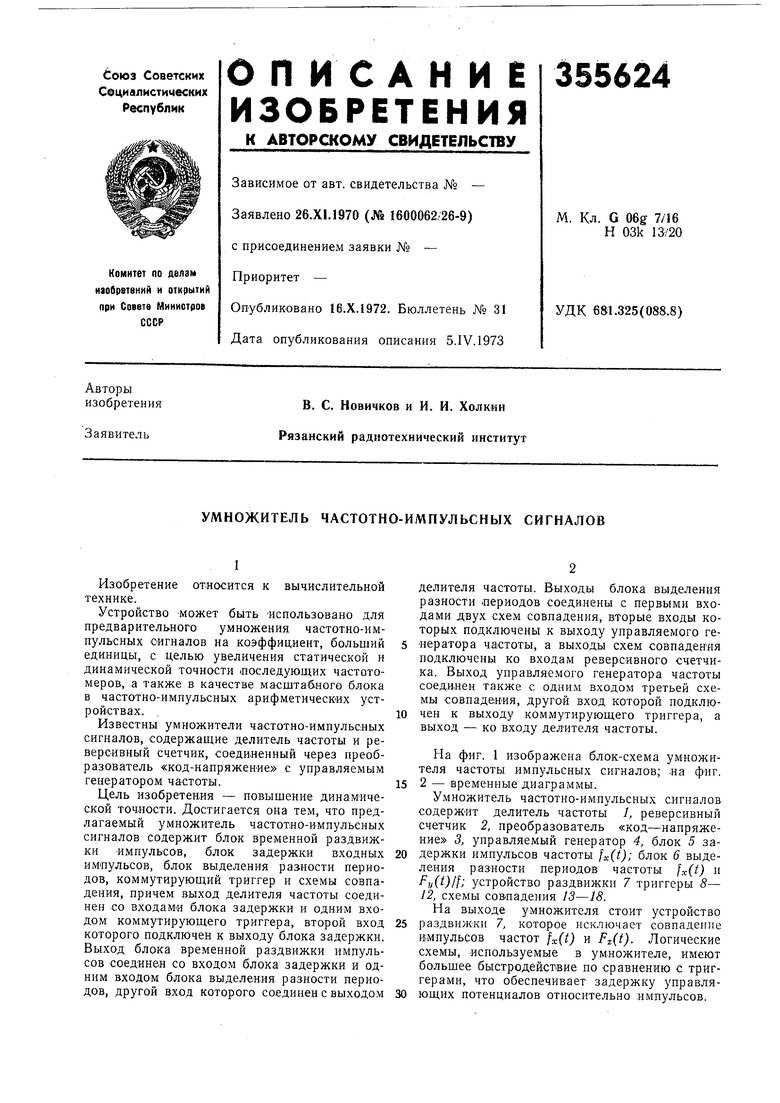

На фиг. 1 изображена блок-схема умножителя частоты импульсных сигналов; .на фиг.

2 - временные диаграммы.

Умножитель частотно-импульсных сигналов содержит делитель частоты /, реверсивный счетчик 2, преобразователь «код-напряжение 3, управляемый генератор 4, блок 5 задержки импульсов частоты y.(t), блок 6 выделения разности периодов частоты lx(t} и Py(t)ll; устройство раздвижки 7 триггеры 8- 12, схемы совладения 13-18. На выходе умножителя стоит устройство

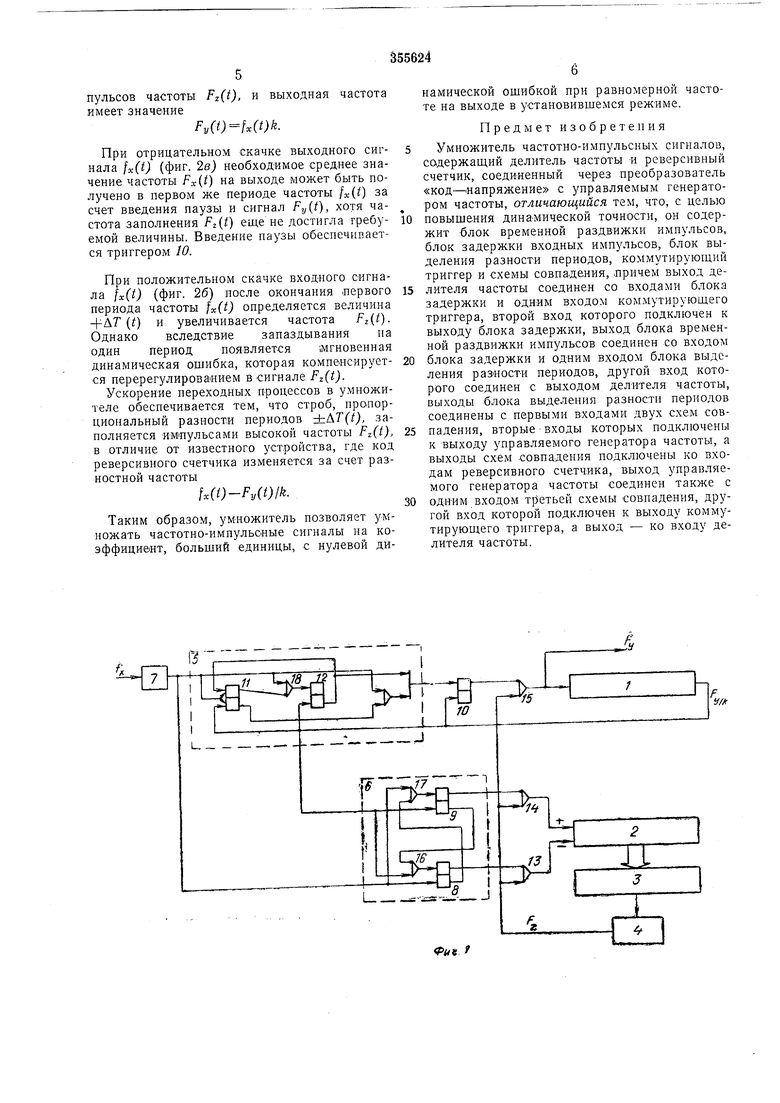

раздвижки 7, которое исключает совпадение импульсов частот fx(t) и Fi(t). Логические схемы, используемые в умножителе, имеют большее быстродействие по сравнению с триггерами, что обеспечивает задержку управляНа фиг. 2 приняты следующие обозначения:

а - входная частота fx(t)j

б - выходная частота Py(t);

в - выходная частота управляемого генератора частоты Pz(t);

в, - сигнал на выходе делителя частоты Fy(t)lk;

г - коэффициент пересчета делителя частоты, k;

д - положительная разность периодов сигналов +AT(t) , Fx(t)k и lx(t), вырабатываемая на единичном выходе триггера 9;

е - отрицательная разиость периодов частот Fy(t)/k и fx(0 вырабатываемая на единичном выходе триггера 8;

ж - единичный выход триггера W.

При рассмотрении работы умножителя частотно-импульсных сигналов характерны три случая:

.1. Устройство находится в установившемся режиме. Частота Fz(t) на выходе управляемого генератора 4 в /г .раз больше входной частоты fx(t);

2.Сигнал fx(0 Получает положительное приращение;

3.Сигнал fx(f) получает отрицателыгое приращение.

Первый случай (диаграммы фиг. 2, а).

Тр,иггеры находятся в нулевом состоянии, триггер 8 - в единичном, что обеспечивается имлульсом сигнала Fy(t)k от делителя частоты /. Импульс частоты Fy:(i) после устройства раздвижки 7 поступает на блоки задержки импульсов 5 и выработки разности периодов 6. Триггер 8 переходит в пулевое состояние, а триггеры 10 и 11-в единичное, схема совпадения 15 открывается, и частота Fz(t) поступает на выход умножителя и вход делителя частоты. После подсчета делителем частоты k импульсов на его выходе появляется импульс F-u(t)k, который переводит триггеры 10 и 11 в нулевое состояние, а триггер 8 - в единичное. Триггер 12 по-прежнему остается в нулевом положении. Таким образом, все элементы умаожителя устанавливаются в исходное состояние, и с приходом следующего импульса fx(t) Процесс повторяется. Значение кода в реверсивном счетчике 2 не изменяется, так как схема совпадения 14 постоянно закрыта, а схема совпадения 13 открывается в моменты, когда отсутствуют импульсы Fz(t). Частота Fy(t) на выходе умножителя в этом случае совпадает с частотой Fz(t), причем

Fy(t)fx(t)k.

Второй случай (диаграммы фиг. 2 б).

После поступления, импульса частоты fx(t) триггеры W и 1} находятся в единичном состоянии, а триггеры 8, 9 и 12 - в нулевом. Частота fx(t) получает положительное приращение, следующий ее импульс приходит раньше, чем импульс Fy(t)k. Этот импульс частоты fx(t) переводит триггер 12 в единичное состояние, а триггер 11 - в нулевое. Запись единицы в триггер 12 обеспечивает запоминание повторного импульса fx(t), что позволяет устранить ошибку в сигнале Fy(t), поскольку

триггер 10 может быть переведен вновь в единичное состояние только после появления импульса Fy(t)k с делителя l. Одновременно повторный импульс fx(t) переводит триггер 9 в единичное состояние, схема совпадения 14

открывается, код в счетчике 2 увеличивается, частота Fz(t) возрастает. После подсчета делителем / k импульсов частоты Fz(t) на его выходе появляется импульс Fy(t)k, который переводит триггеры 9, 10 и 12 ъ нулевое состояние. При переходе триггера 12 в нулевое состояние считывается запомненная ранее единица, вследствие чего триггеры 10 v. 11 переходят в единичное положение. С поступлением следующего импульса частоты lx(t) процесс повторяется. Код в реверсивном счетчике 2 и частота Fz(t) на выходе генератора 4 .нарастают до тех пор, пока за один период частоты lx(t) на выходе делителя частоты 1 не появятся два импульса частоты Fy(t)k. Так как на каждый импульс частоты lx(t) на выходе умножителя вырабатывается k импульсов сигнала Fy(t), то в случае положительного приращения частоты ix(i) среднее значение сигнала на выходе умножителя равно

Py{t)l.(t)k.

Третий случай (диаграммы фиг. 2s).

После поступления импульса lx(t) триггеры 10 к 11 находятся в единичном состоянии, а триггеры 8,9 и 12-в нулевом. Частота/ж(0 получает отрицательное приращение, вследствие чего импульс Fy(t) k поступает раньше следующего импульса lx(t), и триггеры 10, 11 переходят в нулевое состояние, а триггер 8 - в единичное, схема совпадения 75 открывается, код в реверсивном счетчике 2 и частота Fz(t) уменьшаются. После прихода следующего импульса fx(t) триггеры 10 и // устанавливаются в единичное состояние, а триггер 8 в нулевое, триггеры 9 к 12 по-прежнему остаются в нулевом состоянии. С постуилением следующего импульса

Fy(t)/k, процесс повторяется. Код в реверсивном счетчике 2 и частота Fz(t) уменьшаются до тех пор, пока за время между двумя импульсами Fy(t)/k не появятся два импульса частоты fx(0- Поскольку на каждый импульс

частоты fx(t) «а выходе умножителя вырабатывается k импульсов сигнала Fy(t), в случае отрицательного приращения частоты fx(t) среднее значение сигнала на выходе умножителя равно

Fy(i)4(t)k. пульсов частоты Fz(t), и выходная частота имеет значение PyW-MOk. При отрицательном скачке выходного сигнала fx(t) (фиг. 2в) необходимое среднее значение частоты Fx(t) на выходе может быть получено в первом же периоде частоты fx(t) за счет введения паузы и сигнал Fy(t), хотя частота заполнения Fz(t) еще не достигла гребуемой величины. Введение паузы обеспечивается триггером 10. При положительном скачке входного сигнала fx(t) (фиг. 26) после окончания первого периода частоты fx(t) определяется величина (t) и увеличивается частота F(t). Однако вследствие запаздывания на один период появляется мгновенная динамическая ошибка, которая компенсируется перерегулированием в сигнале/- z(ОУскорение переходных процессов в умножителе обеспечивается тем, что строб,пропорциональный разности периодов (t), заполняется импульсами высокой частоты Fz(t), в отличие от известного устройства, где код реверсивного счетчика изменяется за счет разностной частоты f(t)-Fy(t)/k. Таким образом, умножитель позволяет умпожать частотно-импульсные сигналы на коэффициент, больший единицы, с нулевой динамической ошибкой при равномерной частоте на выходе в установившемся режиме. Предмет изобретения Умножитель частотно-импульсных сигналов, содержащий делитель частоты и реверсивный счетчик, соединенный через преобразователь «код-напряжение с управляемым генератором частоты, отличающийся тем, что, с целью повышения динамической точности, он содержит блок временной раздвижки импульсов, блок задержки входных импульсов, выделения разности периодов, коммутирующий триггер и схемы совпадения, причем выход делителя частоты соединен со входами блока задержки и одним входом коммутирующего триггера, второй вход которого подключен к выходу блока задержки, выход блока временной раздвижки импульсов соединен со входом блока задержки и одним входом блока выделения разности периодов, другой вход которого соединен с выходом делителя частоты, выходы блока выделения разности периодов соединены с первыми входами двух схем совпадения, вторыевходы которых подключены к выходу управляемого генератора частоты, а выходы схем совпадения подключены ко входам реверсивного счетчика, выход управляемого генератора частоты соединен также с одним входом третьей схемы совпадения, другой вход которой подключен к выходу коммутирующего триггера, а выход - ко выходу делителя частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1973 |

|

SU450186A2 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СИГНАЛОВ | 1971 |

|

SU420082A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД | 1972 |

|

SU426318A1 |

| Преобразователь частоты в код | 1971 |

|

SU443482A1 |

| САМОНАСТРАИВАЮЩИЙСЯ ПРЕОБРАЗОВАТЕЛЬ ЗНАКОПЕРЕМЕННЫХ ЧАСТОТНО-ИМПУЛЬСНЫХ СИГНАЛОВВ КОД | 1968 |

|

SU210488A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ ВЫЧИТАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU284442A1 |

| ВСЕСОЮЗНАЯ | 1973 |

|

SU386403A1 |

| Умножитель частотно-импульсных сигналов | 1971 |

|

SU475620A1 |

| ЧАСТОТНО-ИМПУЛЬСНАЯ СЛЕДЯЩАЯ СИСТЕМА | 1973 |

|

SU372543A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД С НЕПРЕРЫВНЫМОТСЧЕТОМ | 1971 |

|

SU310383A1 |

f(i)

FyM/k д e ()

д ML

fzft)

Ш

yf)

--ч-г-МП

JC 5 ML В ML

Фиг. 2

JL

П П

и U

шг III IIIIII1И I I I I I I I I и I I I I I 1

Даты

1972-01-01—Публикация