1

Изобретение относится к области вычислительной техники и может быть использовано ДЛЯ иредварительного умножения часто ноимиульсных сигналов на коэффициент, больший единицы, с целью увеличения статической и динамической точности последующих частотомеров, а также в качестве масштабного блока в частотно-импульсных устройствах.

Известно устройство для умножения частоты следования импульсов, содержаш,ее устройство раздвижки, блок задержки имн льсов, коммутирующий триггер, делитель часчоты, блок выделения разности периодов двух частот, реверсивный счетчик частоты и импульсно-потенциальные схемы совпадения.

Недостатком известного устройства является значительное количество оборудования.

С целью упрощения схемы предлагаемы; умножитель содержит инвертор, интегратс;р и два ключа, первые входы которых подкл;очс иы к выходу блок. вычитания периодов, вторые входы иодктючены соответственно .; выходам интегратора и инвертора, а выхо;1ы - ко входу интегратора, выход которого соединен со входом управляемого гсперато1)а частоты н входом инвертора.

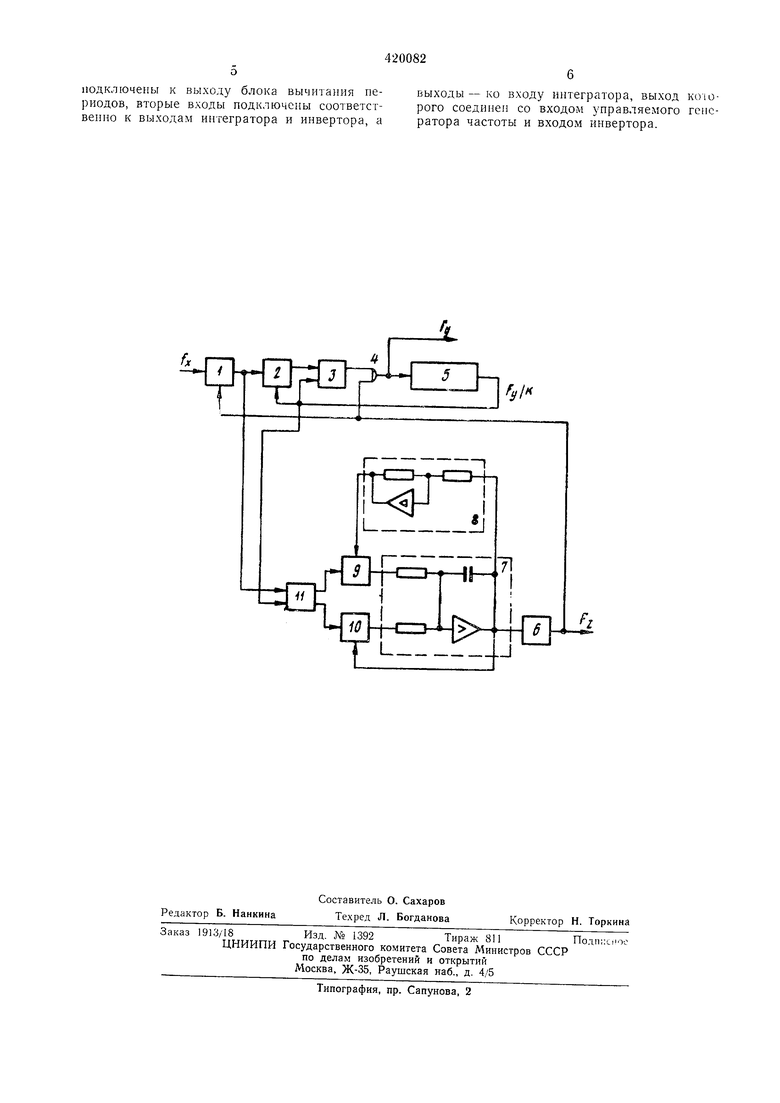

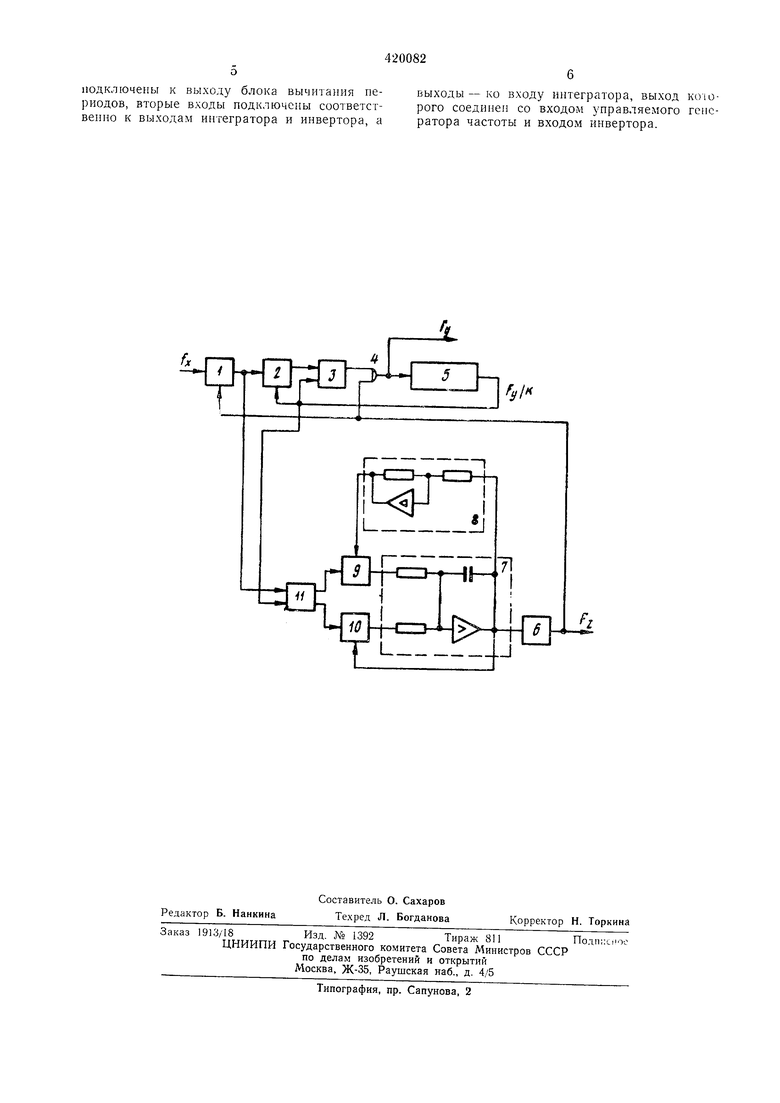

На чертеясе изображена схема H|ien;iaraeмого умножителя частоты сигналов.

множитель частоты состоит из блока раздвижки 1, блока 2 задержки имнульсов, коммутирующего триггера 3, схемы «PI 4, делителя частоты 5, управляемого генератора частоты 6, интегратора 7, инвертора 8, ключей 9 и 10 и блока 11 вычитания периодов двух частот.

БЛОК раздвил ки 1, подключенный ко входу умножителя, исключает совпадение импульсов частот fx и .F,.

YcTpoiiCiBo работает следующим образом.

ЕСЛИ оно находится в установившемся режиме, то частота F, сигнала на выходе управляемого генератора частоты 6 в /г раз больше частоты входного сигнала /л-Код блока 2 задержки импульсов равен нулю, на выходе блока вычитания 11 периодов имеется сигнал , а коммутируюи1ий триггер 3 находится в нулевом состоянии, что обеспечивается импульсом сигнала F,i/k (Fy - частота выходного сигнала) от делителя частоты 5. Импульс частоты входного сигнала /.V иосле блока раздвижки 1 поступает на блоки 2 задержки импульсов и вычитания периодов 11. Сигпал с вы.хода блока 11 закрывает КЛЮЧ 10, код блока 2 приобретает зиачение, равное единице, а коммутируюиии триггер 3 переходит в единичное состояние. Схема «И 4 открывается, и сигиа, с частотой F, иостунасг на выход умножите,тя и вход делителя частоты 5. После иодсчета /с им иульсов пелитслем частоты иа его выходе

появляется импульс F,, который переводит триггер 3 в пулевое состояние, списывает едпиицу кеда в блоке 2 задержки импульсов и вырабатывает па выходе блока 11 вычитаиия периодов двух частот сигнал -Д7 Таким образом, все Элементы умножителя устанавливаются в исходное состояние, к с приходом следующего импульса / процесс повторяется. Значение упраплпю1цего напряжения па выходе интегратора 7 практически не изменяется, так как ключ 9 закрыт, а ключ 10 открывается на весьма короткое время, не превышающее периода частоты F-. Частота F,j на выходе умножителя в этом случае совпадает с частотой F,, причем

Fy kl,.

Если сигнал частоты 1х получает положительное приран1,ение, то после поступления импульса частоты /. триггер 3 находится в единичном состоянии, код блока 2 задержки импульсов равен единице, а сигналы с выходов блока II вычитания периодов закрывают ключи 9 и 10. Частота Дг- получает положительпое приращеиие и следующий ее импульс приходит раиьше, чем импульс F,jlk. Этот импульс частоты /X вырабатываег на выходе блока 11 вычитапия периодов сигнал +Д7 и увеличивает код блока 2 задержки импульсов па едииину. Запись единицы в блок 2 обесиечивает запомипапие повторного импульса 1х, что позволяет устрапить ошибку в сигнале F,j, поскольку триггер 3 может быть переведен вновь в единичное состояние только после появления импульса Fylk с делителя 5. Одновременно сигнал с выхода блока вычитаиия 11 открывает ключ 9, и положительиое напряжение с выхода инвертора 8 увеличивает отрицательпое управляюнхее папряжепие на выходе интегратора 7, а частота F возрастает. После подсчета /г импульсов частоты /г делителем 5 па его выходе появляется импульс F,,lk, который прекращает выработку сигпала +Д на выходе блока вычитапия И, переводит триггер 3 в нулевое состояние и списывает одну единицу с кода блока 2 задержки импульсов. При списывании запомиеппой рапее едипицы кода блока 2 на его выходе появляется импульс, который переводит коммутирующий триггер 3 в единичн(;е состояние.

С поступлепием следующего имиульса частоты fx процесс повторяется. Отрицательное управляющее иапряжение на выходе иитегратора 7 и частота .F, па выходе генератора 6 будут возрастать до тех пор, пока за один период частоты /л- па выходе делителя частоты 5 пе появятся два импульса частоты Fylk. Так как иа каждый импульс частоты /. иа выходе умпожигелл вырабатывается /г импульсов си1нала Fy, то в случае положительного приращения частоты f;v средиее значение сигнала на выходе умножителя будет равно: Fy --klx.

Если сигнал частоты f получает отрицательпое приращение, то после поступления

импульса Ix. сигнал с выходов блока вычитания 11 закрывает ключи 9 и 10, код в блоке 2 имеет значение, равное единице, а триггер 3 находится в едииичном состоянии. Частота /лполучает отрицательпое приращепие, вследствие чего импульс Fyjk поступает раньще следующего импульса f:v, и код в блоке 2 обнуляется, триггер 3 переходит в нулевое состояние, а иа выходе блока вычитания 11 вырабатывается сигнал -ДГ. Ключ 10 открывается, и иа его вход и вход нитегратора 7 постунает отрицательное напряжение с выхода интегратора 7. Отрицательное напряжение на выходе интегратора 7 у.меньшается, и частота F иа

выходе генератора 6 также уменьшается. После прихода следующего импульса /.х- сигнал на выходе блока вычитаиия 11 обнуляется, в блок 2 занисывается единица, и триггер 3 иереходит в единичное состояние.

С поступлепием следующего импульса Fylk процесс повторяется. Напряжение на выходе интегратора 7 и частота Р будут уменьшаться до тех пор, нока за время между двумя импульсами Fylk ие появятся два импульса частоты 1х. Поскольку на аждый импульс частоты ix па выходе умножителя вырабатывается k импульсов сигиала Fy, то в случае отрицательного приращения частоты /д- среднее значение сигнала на выходе умножителя

равно:

Fy klx.

Таким образом, при поступлении па вход умножителя частоты /ж, на каждый ее импульс на выход умножителя поступает k импульсов частоты fz, и выходная частота имеет значение:

Fy .

Таким образом, умножитель позволяет умпожать частотно-импульсные сигналы на коэффициент, больший единицы, с нулевой динамической обшивкой при равпомериой частоте па выходе в установившемся режиме. Время установления в устройстве может составлять несколько периодов входной частоты.

Предмет изобретепия

Умиожитель частоты сигналов, содержащий делитель частоты, выход которого соединен

со входом блока задержки импульсов, с одним входом коммутирующего триггера, второй вход которого соединен с выходом блока задержки импульсов, и с одним входом блока вычитапия периодов, второй вход которого

соединен с выходом блока раздвижки и со вторым входом блока задержки импульсов, а первый и второй входы блока раздвижки подключены соответственно ко входу устройства и выходу управляемого генератора частоты,

который через схему «И, второй вход которой соединен с выходом коммутирующего триггера, подключен ко входу делителя частоты, отличающийся тем, что, с це.лью упрощения схемы, он содержит инвертор, иитегратор и два ключа, первые входы которых

подключены к выходу блока вычитания периодов, вторые входы подключены соответственно к выходам интегратора и инвертора, а

выходы - ко входу интегратора, выход коюрого соединен со входом управляемого генератора частоты и входом инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| УМНОЖИТЕЛЬ ЧАСТОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 1972 |

|

SU355624A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU528695A1 |

| Умножитель частоты следования импульсов | 1973 |

|

SU450186A2 |

| Умножитель частотно-импульсных сигналов | 1971 |

|

SU475620A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2062549C1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В КОД | 1972 |

|

SU426318A1 |

| Т в. в. Смеляков | 1973 |

|

SU375774A1 |

| Датчик углового положения,скорости и ускорения вращения вала | 1983 |

|

SU1101740A1 |

| Умножитель частоты | 1982 |

|

SU1083330A1 |

| Устройство для регулирования расхода | 1984 |

|

SU1171759A1 |

1Л - -СГЗ- -

71

HiII

Даты

1974-03-15—Публикация

1971-11-11—Подача