1

Изобретение относится к автоматике и вычислительной -технике.

Известен .умножитель частотно - импульсных сигналов, .содержащий управляемый генератор частоты, подключенный к блоку перераспределения, -блок выделения разности периодов двух частот, выходы которого через схемы совпадения, связанные с выходом управляемого генератора частоты, подсоединены к реверсивному счетчику, а выходы этого счетчика через преобразователь код-напряжение - к входу управляемого генератора частоты, коммутирующий триггер, связанный через схему совпадения, подключенную к управляемому генератору частоты, с делителем частоты.

Предложенное устройство отличается тем, что в него введены .доп:олнительные коммутирующий триггер, делитель частоты и логич еские схемы. Т1ри этом вьгход умножителя через схему сборки соединен с входами основного И дополнитеЛ:ьного делителей частоты, выходы которых через схему сборки подключены к одному из -еходов блока выделения разности периодов двух чагтот. Второй в-ход этого блока соединен свыходом устройства перераспределения, с единичным установоч ным «ходом основного чкоммуТирующего триггера и с импул-ксньш входом схемы совпадения, потенциальный -вход которой подключен к единичному выходу основного коммутирующего триггера, а выход - к единичному установочному входу дополнительного коммутирующего триггера. Нулевой установочный вход последнего соединен с выходом дополнительного делителя частоты, а единичный выход - с потенциальным входом схемы совпадения, импульсный вход которой через инвертор подключен к выходу управляемого

генератора частоты, а ее выход - к входу дополнительного делителя частоты.

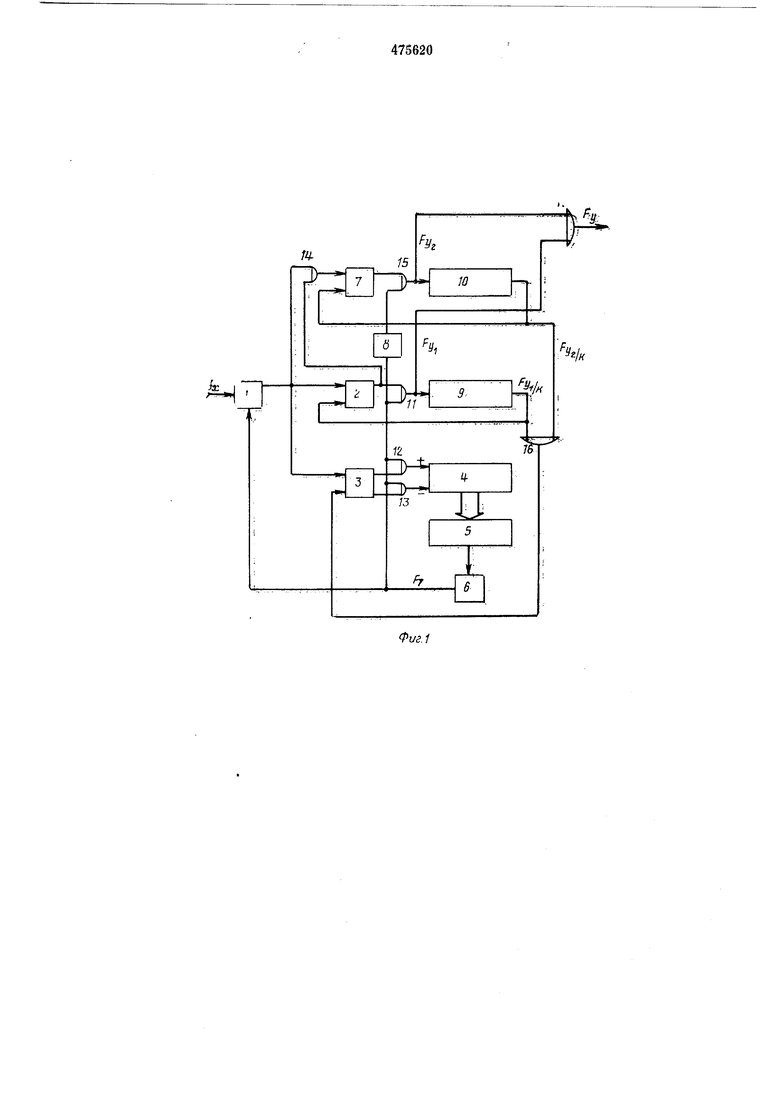

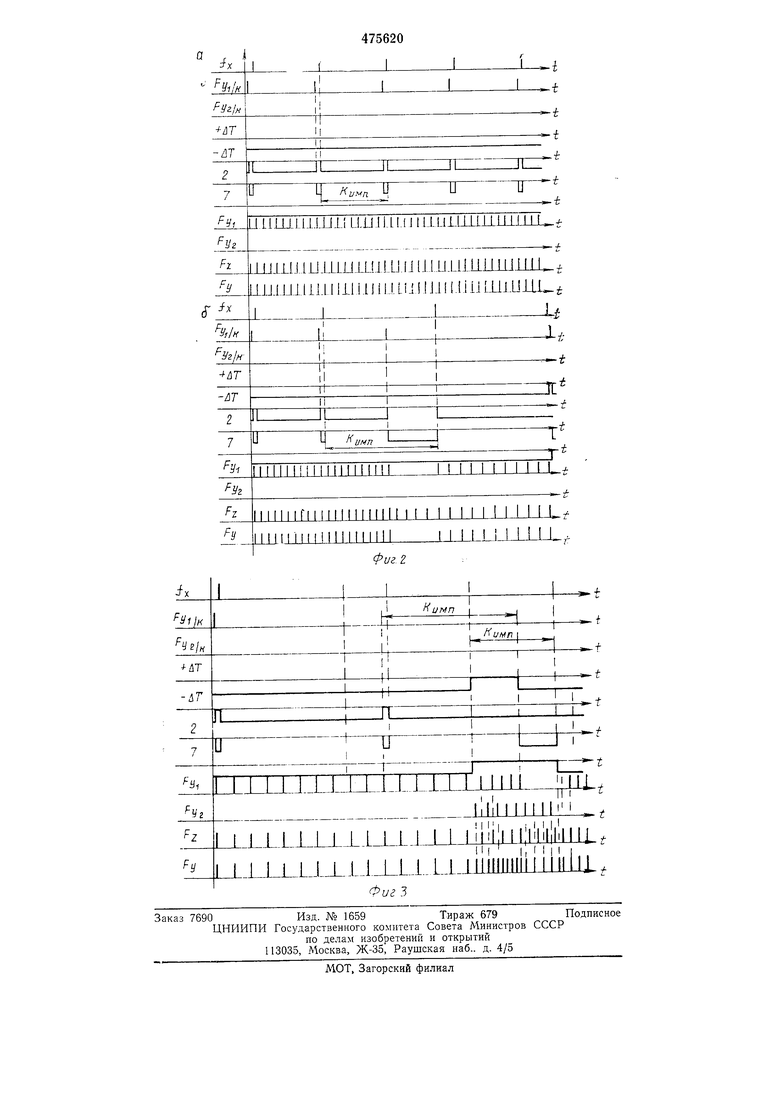

На фиг. 1 изображена схема умножителя частотно-импульсных сигналов. На фиг. 2, а, б и 3 представлены :нременные диаграммы,

поясняющие работу умножителя.

Умножитель частотно- импульсных сигналов состоит из блока 1 первраспредйления, коммутирующего триггера 2, бл:ока 3, лыделения разности периодов :дву-х частот, .pfesepcHBного счетчика 4, ттреобраЕВтов-ателя 5, код-напряжение, управл яемото тенератора .6 частоты, дополнителькаго коммутирующего триггера 7, инвертора , делителя 9 частоты, дополнительного делителя 10 частоты, импульсно-потенциальных схем совпадения 11, 15 и сборки 16 и 17.

На фиг. 2 и 3 приняты следующие .обозначения:f X - входная частота;

f ,, - выходная частота основного канала

умножения;

Fj,,, - выходная частота дополнительного канала умножения; F, - выходная частота управляемого

генератора 6 частоты; /,,, - выходная частота умножителя; Fy //( - сигнал на выходе делителя 9 частоты;ГУ //( - сигнал на выходе дополнительного

делителя 10 частоты; / - коэффициент пересчета основного и

дополнительного делителей частоты; + А7- положительная разность периодов сигналов Fу /к или Fy //с и f , вырабатываемая на положительном выходе блока 3 выделения разности периодов двух частот;

-Л/- отрицательная разность периодов частот F /к или F,. /к и /д. , вырабатываемая на отрицательном выходе блока 3 выделения разности периодов двух частот.

При рассмотрении работы умножителя частотно-импульсных сигналов характерны три случая;

устройство находится в установившемся режиме, при этo частота F, на выходе управляемого генератора б частоты в к раз больше входной частоты f j- ;

сигнал /.V получает отрицательное приращение;

сигнал /д. получает положительное приращение.

Рассмотрим первый случай (диаграммы фиг. 2, а).

В исходном состоянии триггеры 2 и 7 находятся в нулевом состоянии. Схема 13 совпадения открыта нулевым потенциалом, поступающим с отрицательного выхода блока 3 выделения разности периодов двух частот. Это обеспечивается импульсами сигналов Fy IK и Fy /к от делителей 9 и 10 частоты

соответственно. Импульс частоты f. после блока 1 перераспределения поступает на блок 3 выделения разности периодов двух частот, па вход схемы 14 совпадения и единичный установочный вход триггера 2. Блок 3 закрывает схему 13 совпадения, коммутирующий триггер 2 переходит в единичное состояние, схема 11 совпадения открывается и частота F, с выхода управляемого генератора 6 частоты поступает на выход умножителя и на вход делителя 9 частоты. После подсчета к импульсов делителем 9 частоты на его выходе появляется импульс F, /к, который переводит коммутирующий триггер 2 в нулевое состояние, а на отрицательном выходе блока 3-разрещающий потенциал, открывающий схему 13 совпадения.

Триггер 7 по-прежнему остается в нулевом положении. Таким образов, все элементы умножителя устанавливаются в исходное состояние и с приходом следующего импульса /д. процесс повторяется. Значение кода в реверсивном счетчике 4 не изменяется, так как схема 12 совпадения постоянно закрыта, а схема 13 совпадения открывается в моменты, когда отсутствуют импульсы Р . Частота Fy на выходе умножителя в этом случае совпадает с частотой Fy и с частотой F.,. ,

причем Fy - к f j ,

Рассмотрим второй случай (диаграммы фиг. 2,6).

После поступления импульса fj. триггер 2 находится в единичном состоянии, триггер 7-в нулевом, а схемы 12 и 13 закрыты отрицательными потенциалами, которые подаются с выходов блока 3. Частота /д. получает отрицательное приращение, вследствие чего импульс F. /к поступает раньше следующего импульса /д. и триггер 2 переводится в нулевое состояние, а на отрицательном выходе блока 3 появляется потенциал, открывающий схему 13. Частота .F- поступает на вычитающий вход реверсивного счетчика 4, и его код и частота F уменьшаются. После прихода следующего импульса f., триггер 2 устанавливается в единичное состояние, а схема 13 закрывается. Триггер 7 при этом по-прежнему остается в нулевом

состоянии.

С подачей следующего импульса Fy /к

процесс повторяется. Код в реверсивном счетчике 4 и частота F, уменьшаются до тех

пор, пока на время между двумя импульсами Fy /к не появятся два импульса частоты / . Поскольку на каждый импульс частоты на выходе умножителя вырабатывается к импульсов сигнала Fy , то и в случае отрицательного нриращения частоты /j. среднее значение сигнала на выходе умножителя равно

.

45

Рассмотрим третий случай (диаграммы фиг. 3).

После поступления импульса частоты f. триггер 2 находится в единичном состоянии, триггер-7 в нулевом, а схемы 12 и 13 закрыты. Частота f получает положительное приращение, и следующий ее импульс приходит раньше, чем импульс F /к. Этот импульс через схему 14 попадает на единичный установочный вход дополнительного коммутирующего триггера 7, так как триггер 2 находится в единичном состоянии и схема 14 открыта. Триггер 7 переходит в единичное состояние, схема 15 открывается, и на вход дополнительного делителя 10 частоты, имеющего коэффициент пересчета, равный к, поступает частота F . Одновременно импульсы частоты Fy , сдвинутые на полпериода во

времени относительно F за счет инвертирования их инвертором 8 суммируются на схеме 17 сборки с импульсами частоты Fy ,

поступающими с делителя 9 частоты, и подаются на выход умножителя. Таким образом, нри положительном изменении входной частоты /г работают одновременно оба делителя частоты. В то же время блоком 3 вырабатывается положительная разность +АГ периодов частот f,. и /,,, IK. Схема 12 открыта и происходит увеличение кода реверсивного счетчика 4 и частоты F- . После подсчета к импульсов делителем 9 частоты на его выходе появляется импульс Fy /к, который

переводит триггер 2 в нулевое состояние и закрывает схему 12. До прихода следующего импульса частоты f работает дополнительный делитель 10 частоты. Если импульс частоты /д. появится раньше импульса F /к,

то блок 3 открывает схему 12, и происходит дальнейшее увеличение кода реверсивного счетчика 4 и частоты F, . При этом коммутирующий триггер 2 переводится в единичное состояние и импульсы частоты F, поступают на вход делителя 9 частоты и происходит суммирование на схеме 17 сборки частот Р., и F.. . После подсчета делитеy у.

лем 10 частоты к импульсов появляется импульс сигнала .F /к, который переводит

триггер 7 в нулевое состояние и обеспечивает закрывание схемы 12.

Код реверсивного счетчика 4 и частота f, на выходе генератора 6 возрастают до тех пор, пока за один период частоты /д. на выходе делителя 9 частоты и дополнительного делителя частоты не появятся импульсы частоты Ру /к и частоты .Fy, /к соответственно.

Так как на каждый импульс частоты f на выходе умножителя вырабатывается к импульсов сигнала .Fy , то и в случае положительного приращения частоты f,. среднее значение сигнала на выходе умножителя равно

Ру Ф.

Р Р у у.

Таким образом, при поступлении на вход умножителя частоты / на каждый ее импульс на выход умножителя поступает /с импульсов частоты F и выходная частота имеет значение

Fy Kfx.

При отрицательном скачке выходного сигнала f (фиг. 2, б) необходимое среднее значение частоты Fy на выходе может быть получено в первом же периоде частоты f за счет введения паузы в сигнал F у , хотя

частота заполнения F еще не достигла требуемой величины. Введение паузы обеспечивается триггеро г 2.

При положительном скачке входного сигнала /д. (фиг. 3) после окончания первого периода частоты f,. определяется величина + АТ и происходит увеличение частоты /В предложенном устройстве перерегулирования в сигнале F, и рассогласования периодов частот f . и F /к и F,. /к не наб 32

людается. Это достигается обеспечением поочередной работы основного и дополнительного делителей частоты, сигналы с которых сзммируются на выходе умножителя. Поэтому длительность переходного процесса и предлагаемом устройстве при положительном приращении входного сигнала f. имеет практически то же значение, что и при отрицательном приращении входного сигнала.

Таким образом, предложенный умнож)тель частотно-импульсных сигналов позволяет в несколько раз уменьшить время переходных процессов в схеме при положительном изменении входного сигнала по сравнению с известным умножителем.

Предмет изобретения

Умножитель частотно-импульсных сигналов, содержащий управляемый генератор частоты, подключенный к блоку перераспределения, блок выделения разности периодов двух частот, выходы которого через схемы совпадения, связанные с выходом управлясмого генератора частоты, подключены к реверсивному счетчику, выходы которого чере:; преобразователь код-напряжен 1е подключо ны к входу управляемого генератора частоты, ком.мутирующий триггер, связанный чере:

схему совпадения, подключенную к управляемому генератору частоты, с делителем частоты, отличающийся тем, что, с целью по вышения быстродействия, оно содержит дя полнительные коммутирующий триггер, до

литель частоты и логические схе.мы, причел входы основного и дополнительного делите лей частоты подключены через первую схем сборки к выходной шине устройства, а выхо ды подключены к первым входам соответст

венно основного и допрлнительного коммут , рующих триггеров и через вторую схему к первому входу блока выделения разности периодов двух частот, к второму входу которого подключен блок перераспределения.

связанный с вторым входом основного коммутирующего триггера и через схему совпадения, подключенную к выходу основного коммутирующего триггера, с первым входом дополнительного ком1мути|рующего триггера, выход которого через схему -совпадения, подключен ную через инвертор к управляемому генератору частоты, связан с входом дополнительного делителя частоты.

Ji

%

%

15

| название | год | авторы | номер документа |

|---|---|---|---|

| УМНОЖИТЕЛЬ ЧАСТОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 1972 |

|

SU355624A1 |

| Умножитель частоты следования импульсов | 1973 |

|

SU450186A2 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СИГНАЛОВ | 1971 |

|

SU420082A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU966848A1 |

| Устройство для регулирования расхода | 1984 |

|

SU1171759A1 |

| Умножитель частоты | 1980 |

|

SU936372A1 |

| Контурная система программного управления | 1991 |

|

SU1800446A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU999135A2 |

| Устройство для программного управления скоростью подачи | 1982 |

|

SU1067473A1 |

| Датчик углового положения,скорости и ускорения вращения вала | 1983 |

|

SU1101740A1 |

Авторы

Даты

1975-06-30—Публикация

1971-11-18—Подача