Изобретение отлосится к области радяотелемеприи.

Известно устройство для обработки ииформации многоканальной системы, содержащее блок кодирования адреса и синхронизато1р, один выход iKJOTopoTo подсоединен ко входу блока кодирования времени и в каждом канале к первым входам блоков кодирования информации с устранением избыточ-ности, ко вторым входам которых подключены источники информации, а выходы каждого из п разрядов блока кодирования информации с устранением ее избыточности подключены ко входам п ячеек памяти.

Для увеличения объема передаваемой информации в каждом каиале выходы ячеек памяти через схему «ИЛИ подключены параллельно к первому входу схемы «И и к первому входу схемы «НЕТ, ко второму входу которой и ко второму входу схемы «И подключен второй выход синхронизатора, а выход схемы «И через соответствующие отводы линии задержки подсоединен к первому входу каждой из п дополнительных схем «И, ко вторым входам которых подсоединены выходы соответствующих ячеек памяти. Выходы дополнительных схем «И каждого канала подключены ко входу дополнительной схемы «ИЛИ, соответствующему данному каналу, причем между первым входом дополнительной схемы

«ИЛИ, и ВЫХОДО.М схем «И в каждом канале включен бло;к кодирования адреса, а выход блока кодирования времени подключен ко второму входу дополнительной схемы

«ИЛИ, выход которой является выходом устройства.

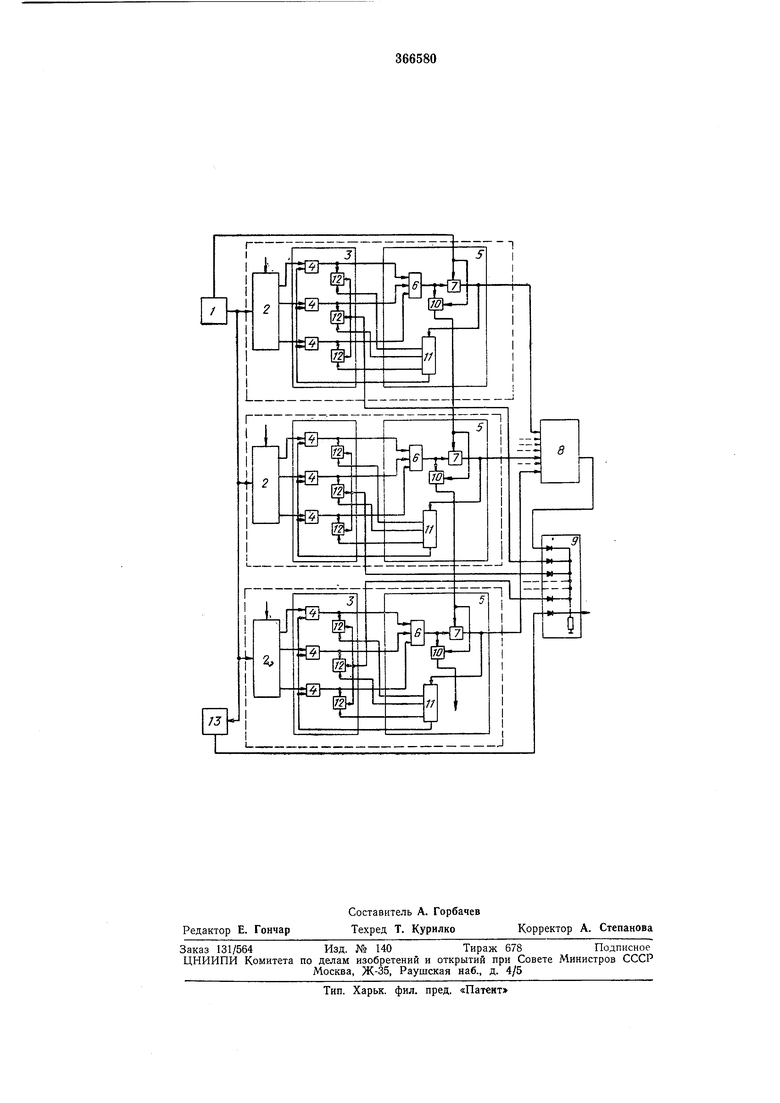

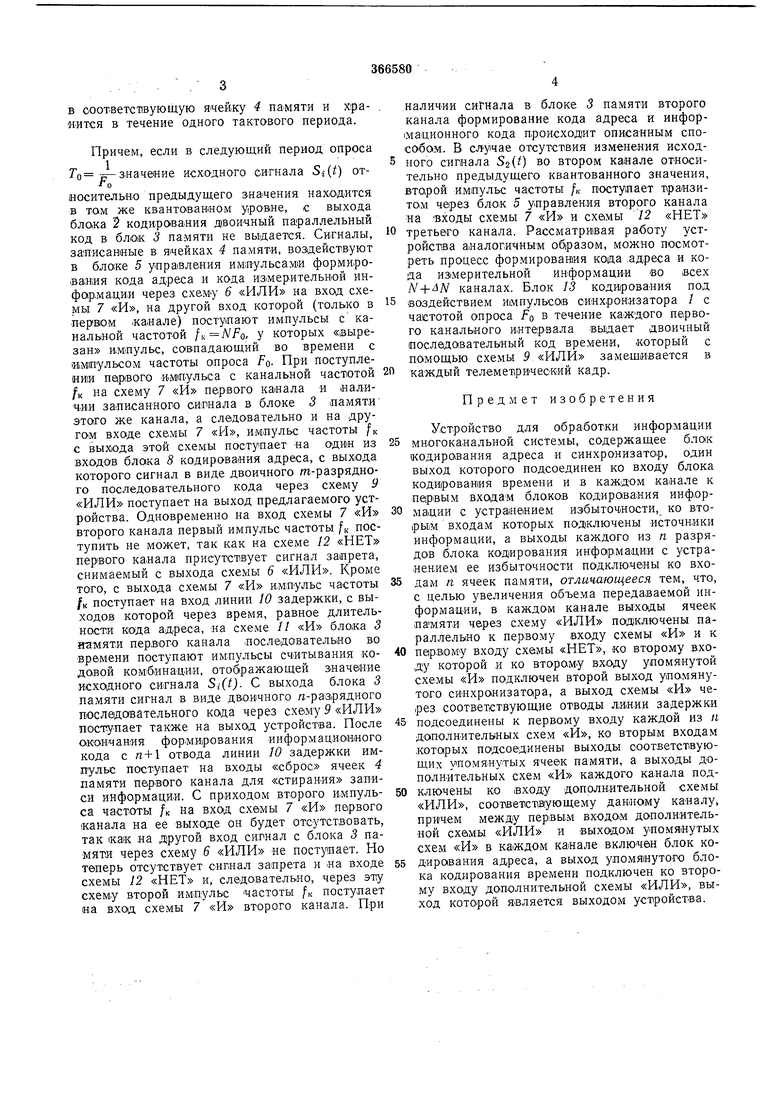

На чертеже приведена блок-схема предлагаемого устройства.

Устройство состоит из син.хронизатора 1,

блоков 2 кодирования измерительной информации с устранением избыточности ее, Л+.V блоков 3 памяти, п ячеек 4 памяти в каждом блоке; блоков 5 управления имтльсам.и формирования кода адреса и кода измерительной информации; схемы 6 схемы 7 блока 8 кодирования адреса; выходной схемы 9 линии 10 задержки; п схем // «И в каждом блоке 3 памяти; схемы 12 блока 13 кодироваяия времени.

Сигналы синхронизатора / с частотой опроса FQ управляют работой блоков 2 кодирования измерительной информации. В блоках 2 кодирования всех N+dN каналов одновременно в течение первого канального интервала происходит преобразование млновенного значения исходного сигнала 5,-(г ) в двоичный л-разрядный параллельный код. Каждый

разряд кода записывается в блоке 3 памяти

в соответспвующую ячейку 4 памяти и храН-ится в течение одного тактового периода.

Причем, если в следующий период опроса Го р-з-начение исходного сигнала (i} от-fo

носительно предыдущего аначения находится в том же квантованном yipOBHe, с выхода блока 2 кодирования д воичный параллельный код в блок 3 памяти не выдается. Сигналы, записанные в ячейках 4 памяти, воздействуют в бло;ке 5 управления импульсами формирования кода адреса и кода измерительной инфар.ма,ци.и через схему 6 «ИЛИ на вход схемы 7 «И, на другой вход которой (только в первом |Ка.нале) поступают импульсы с канальной частотой , у которых «вырезан и.М1пульс, совпадающий во времени с имиульсом частоты олроса FQ. При поступлении neipBoro имтульса с канальной частотой /к на схему 7 «И первого каяала и «аличди записанного сигнала в блоке 3 памяти этого же канала, а следовательно и на другом входе схемы 7 «И, импульс частоты /к с выхода этой схемы поступает «а одни из входов блока 8 кодирования адреса, с выхода которого сигнал в виде двоичного т-разрядного последовательного кода через схему 9 «ИЛИ поступает на выход предлагаемого устройства. Одновременно на вход схемы 7 «И второго канала первый импульс частоты /к поступить не может, так как на схеме 12 «НЕТ первого канала присутствует сигнал запрета, снимаемый с выхода схемы 6 «ИЛИ. Кроме того, с выхода схемы 7 «И нмпульс частоты /к поступает на вход линии W задержки, с выходов которой через время, равное длительности кода адреса, иа схеме И «И блока 3 н-амят.и первого канала последовательно во времени поступают импульсы считывания кодовой комбинации, отображающей значе1Ние исходного сигнала Si(t). С выхода блока 3 памяти сигнал в виде двоичного /г-разрядного последавательного кода через схему 9 «ИЛИ поступает также на выход устройства. После окончания формирования информационного кода с п+1 отвода линии 10 задержки импулыс поступает на входы «сброс ячеек 4 памяти пе,рвого канала для «стирания записи информации. С приходом второго импульса частоты /к на вход схемы 7 «И neipBoro канала на ее выходе он будет отсутствовать, так «ак на другой вход сигнал с блока 3 памяти через схему 6 «ИЛИ не поступает. Но теперь отсутствует сигнал запрета и «а входе схемы 12 «НЕТ и, следовательно, через эту схему второй импульс частоты /к поступает на вход схемы 7 «И второго канала. При

.наличии сигнала в блоке 3 памяти второго канала формирование кода адреса и информационного кода происходит описанным спосо бом. В случае отсутствия изменения исходного сигнала ) во втором канале относительно предыдущего квантованного значения, второй импульс частоты /к поступает транзитом через бло,к 5 управления второго канала на ВХОДЫ схемы 7 «И и схемы 72 «ПЕТ

0 третьего канала. Рассматривая работу устройства аналогичным образом, можно посмотреть процесс формирования кода .адреса и кода измерительной информации во всех каналах. Блок 13 коди(рования под

5 воздействием импульсов синхронизатора / с частотой опроса FO в течение каждого первого канального интервала выдает двоичный последовательный код времени, который с помощью схемы 9, «ИЛИ замещивается в каждый телеметрический кадр.

Предмет изобретения

Устройство для обработки информации

5 многоканальной системы, содержащее блок кодирования адреса и синхронизатор, один выход которого подсоединен ко входу блока кодирования времени и в каждом канале к первым входам блоков кодирования информации с устранением избыточности, ко вторым входам которых подключены источники информации, а выходы каждого из я разрядов блока кодирования информации с устранением ее избыточности подключены ко входам я ячеек памяти, отличающееся тем, что, с целью увеличения объема передаваемой информации, в каждом канале выходы ячеек памяти через схему «ИЛИ подключены параллельно к первому входу схемы «И и к

40 парному входу схемы «НЕТ, ко второму входу которой и ко второму вХОду упомянутой схемы «И подключен второй выход упомянутого синхронизатора, а выход схемы «И через соответствующие отводы линии задержки

45 подсоединены к первому входу каждой из я дополнительных схем «И, ко вторым входам которых подсоединены выходы соответствующих упомянутых ячеек памяти, а выходы дополнительных схем «И каждого канала подключены ко (ВХОДУ дополнительной схемы «ИЛИ, соотеетствующему данному каналу, причем между пер;вьш входом дополнительной схемы «ИЛИ и выходом упомянутых схем «И Б каждом канале включен блок ко5 диравания адреса, а выход упомянутого блока кодирования времени подключен ко второму входу дополнительной схемы «ИЛИ, выход которой является выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи телеметрической информации | 1983 |

|

SU1145357A1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1980 |

|

SU949838A1 |

| Многоканальная телеизмерительная система | 1986 |

|

SU1310870A1 |

| Устройство для передачи телеметрической информации | 1977 |

|

SU646366A1 |

| Устройство для передачи измерительной информации | 1982 |

|

SU1062753A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Преобразователь сигналов с адаптивной дельта-модуляцией со слоговым компандированием в сигналы с нелинейной импульсно-кодовой модуляцией | 1990 |

|

SU1762411A1 |

| Устройство для передачи телеметрической информации | 1978 |

|

SU734787A1 |

| Устройство для передачи телеметрической информации | 1974 |

|

SU458851A1 |

Авторы

Даты

1973-01-01—Публикация