(54) ДЕМОДУЛЯТОР СИГНАЛОВ С ФАЗОРАЗНОСТНОЙ

МОДУЛЯЦИЕЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОМОДЕМ | 2010 |

|

RU2460215C1 |

| Устройство для детектирования многочастотных сигналов с двукратной относительной фазовой манипуляцией | 1980 |

|

SU921115A2 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ПАССИВНЫХ ПОМЕХ | 1982 |

|

SU1090136A1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1978 |

|

SU790361A1 |

| Усреднитель-анализатор спектра Фурье | 1980 |

|

SU955086A1 |

| Адаптивный групповой приемник многочастотного кода с импульсно-кодовой модуляцией | 1989 |

|

SU1635273A1 |

| Цифровой генератор гармонических функций | 1981 |

|

SU1001069A1 |

| Многоканальный демодулятор дискретных сигналов | 1986 |

|

SU1327317A1 |

| УСТРОЙСТВО УСКОРЕННОЙ СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2446560C1 |

| ЦИФРОВОЙ МОДЕМ | 2001 |

|

RU2218666C2 |

1

Изобретение относится к технике связи и может быть использовано в системах передачи дискретной информации для приема многоканальных взаимно ортогональных сигналов с фазоразностной модуляцией при наличии сдвигов частоты сигналов в канале связи.

Известен демодулятор сигналов с фазоразностной модуляцией, содержащий последовательно соединенные аналого-цифровой преобразователь, первый перемножитель, первый сумматор, первый блок памяти, блок вычисления разности фаз и блок декодирования, последовательно соединенные блок синхронизации и формирователь управляющих импульсов, вь1ходы которого подключены к управляющим входам первого блока памяти, первого сумматора, первого перемножителя и аналого-цифрового преобразователя, информационный вход и второй выход которого соединены соответственно со входом блока синхронизации и первым входом второго перемножителя, выход которого подключен ко второму входу первого перемножителя, а также второй блок памяти и анализатор смещения частоты 1.

Однако помехоустойчивость такого демодулятора невысока.

Цель изобретения - повыщение помехоустойчивости.

Поставленная цель достигается тем, что в демодулятор сигналов с фазоразностной модуляцией, содержащий последовательно соединенные аналого-цифровой преобразователь, первый перемножитель, первый сумматор, первый блок памяти, блок вычисления разности фаз и блок декодирования,

10 последовательно соединенные блок синхронизации и формирователь управляющих импульсов, выходы которого подключены к управляющим входам первого блока памяти, первого сумматора, первого переМножите15 ля и аналого-цифрового преобразователя, информационный вход и второй выход которого соединены соответственно со входом блока синхронизации и первым входом второго перемножителя, выход которого подключен ко второму входу первого перемножителя, а также второй блок памяти и анализатор смещения частоты, введены коммутатор, второй, третий и четвертый сумматоры, счетчик, третий, четвертый и пятый блоки памяти и преобразователь кода, выход которого подключен ко входу второго блока памяти, выход которого соединен с третьим .входом первого перемножителя, причем второй выход блока вычисления разности фаз и выход блока декодирования соединены со входами анализатора смещения частоты, выходы которого подключены к первым входам третьего блока памяти и второго сумматора, выход которого соединен со вторым входом третьего блока памяти, выход которого подключен ко второму входу второго сумматора и к одному из входов третьего сумматора, выход которого соединен со входом четвертого блока памяти, выходы которого подключены к другим входам третьего сумматора и ко входам коммутатора, выходы которого соединены со входами пятого блока памяти, выходы которого подключены ко входам преобразователя кода и четвертого сумматора, выходы которого соединены с соответствующими входами коммутатора, при этом дополнительные выходы формирователя управляющих импульсов соединены с управляющими входами преобразователя кода, третьего, четвертого и. пятого блоков памяти, коммутатора и счетчика, выход которого подключен к соответствующему входу четвертого сумматора, а соответствующий выход преобразователя кода соединен со вторым входом второго перемножителя, преобразователь кода содержит блок кодирования и последовательно соединенные двухразрядный сумматор и многоразрядный переключатель, соответствующие входы которого соединены со входом и выходом блока кодирования, причем первый вход двухразрядного сумматора и вход блока кодирования являются входами преобразователя кода, управляющим входом и выходом которого являются соответственно второй вход двухразрядного сумматора и выход многоразрядного переключателя.

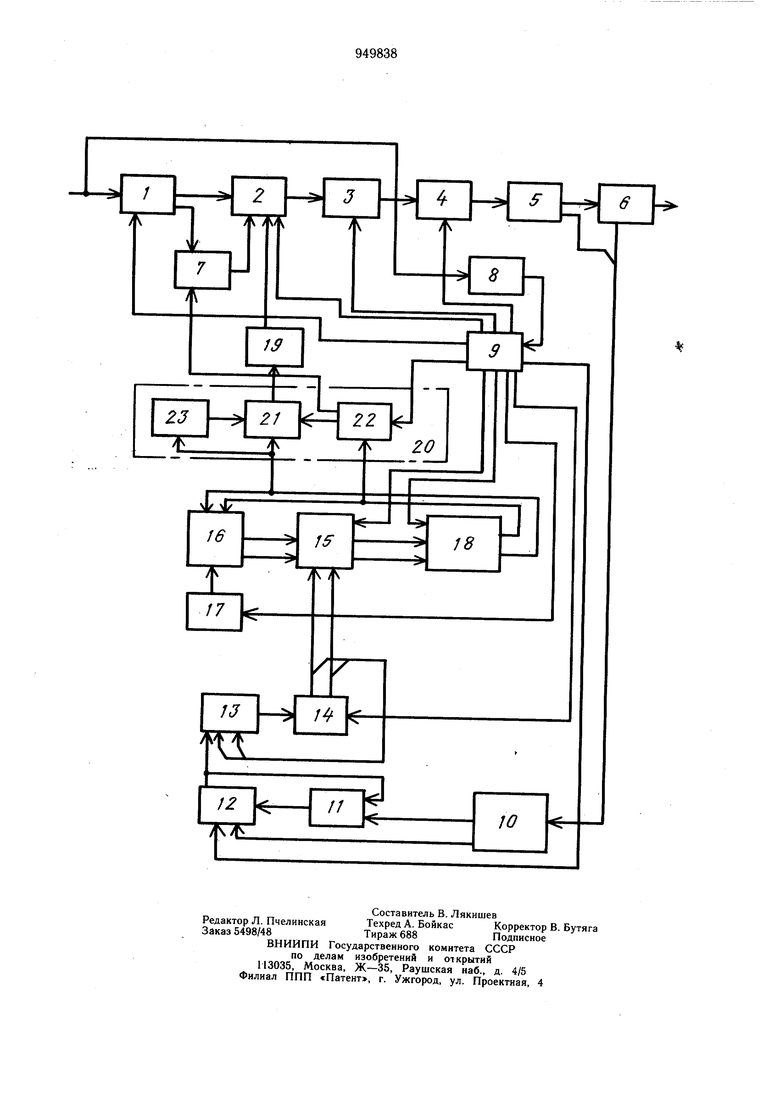

На чертеже приведена структурная электрическая схема предлагаемого демодулятора. .

Демодулятор сигналов с фазоразностной модуляцией содержит аналого-цифровой преобразователь (АЦП) 1, первый перемножитель 2, первый сумматор 3, первый блок 4 памяти, блок 5 вычисления разности фаз, блок 6 декодирования, второй перемножитель 7, блок 8 синхронизации, формирователь 9 управляющих импульсов, анализатор 10 смещения частоты, второй сумматор 11, тре1ий блок 12 памяти, третий сумматор 13, четвертый блок 14 памяти, коммутатор 15, четвертый сумматор 16, счетчик 17, пя,тый блок 18 памяти, второй блок 19 памяти и преобразователь 20 кода, состоящий из многоразрядного переключателя 21, двухразрядного сумматора 22 и блока 23 кодирования.

Демодулятор работает следующим обрааом.

Для разделения -канальных сигналов вычисляется корреляция на интервале ортогональности Т принимаемого группового сигнала S(t) с опорными колебаниями приемника.

Алгоритмы вычисления корреляции: Хк / S(t)sin о/к t dt; УК ;f /S(t) cos UK tdt. чения л к и УК являются npoef

Значения

проекциями канальных сигналов, причем Х, - проекция в синфазном подканале, а У - проекция в квадратурном подканале к-го канала демодулятора.

В предлагаемом устройстве перемножение группового сигнала S(t) на синусные и косинусные составляющие опорных частот

осуществляется в первом 2 и втором 7 перемножителях, причем для этого берутся отсчеты группового сигнала и отсчеты значений опорных колебаний. Перемножение производится последовательно во времени, причем каждый отсчет сигнала умножается на отсчеты синусных и косинусных составляющих всех опорных частот.

Взятие отсчетов группового сигнала и преобразование значений отсчетов в многоразрядные двоичные числа (двоичные коды

5 отсчетов сигнала) осуществляется в аналого-цифровом преобразователе 1, на вход которого поступает многочастотный сигнал. Частоту взятия отсчетов (частоту дискретизации) целесообразно выбрать такой, чтобы на интервале ортогональности Т ук ладывалось 2 (где п - целое число) отсчетов. При этом интервал между отсчетами At Т/2 . Поскольку интервал между частотами канальных сигналов F , то частота дискретизации

- 9 Р

5ТдИСКр.

Это соотнощение может быть и другим, но коэффициент пропорциональности между дискр. и F. по крайней мере, должен быть кратным четырем. Для конкретности считают, что на интервале ортогональности укладывается 64 отсчета, т. е.

fflHcitp. 64-F или Т 64 At .

Для нахождения проекций канальных сигналов в соответствии с алгоритмом рабоJ ты корреляторов отсчеты группового сигнала умножаются на значения опорных колебаний каналов и результат умножения суммируется /накапливается/ в течение интервала ортогональности Т в первом сумматоре 3. Результаты накопления представляют собой проекции сигнала в синфазных и квадратурных подканалах всех каналов и записываются в первый блок 4 памяти. Абсолютные значения (отсчеты) синусных и косинусных составляющих опорных частот формируются на выходе второго блока 19 памяти, в котором записаны значения синуса. Для формирования отсчетов опорных колебаний на вход второго блока 19 памяти необходимо подавать двоичные числа (коды), указывающие адреса ячеек второго блока памяти, в которых записаны сОответст вующие значения синусов. Эти числа - коды адреса второго блока 19 памяти. Формирование кодов адресов второго блок 19 памяти производится в три этапа. Сначала формируются двоичные числа, синусы и косинусы которых соответствуют отсчетам значений опорных колебаний, синфазных и квадратурных канальных сигналов, т. е. аргументы или коды аргументов, так как функции этих аргументов (синусы или косинусы) соответствуют значениям опорных колебаний. Затем коды, аргумента перекодируются в преобразователе 20 кода в коды адресов ячеек второго блока 19 памяти. Для формирования кода аргумента сначала формируется аргумент, соответствуюпдий гармоникам частоты F, затем к этим значениям аргумента прибавляются некоторые начальные значения, такие, чтобы аргумент первой гармоники частоты F соответствовал значениям аргумента опорного колебания первого канала с учетом смещения частоты этого канального сигнала в тракте связи.

Целесообразность перекодирования кодов аргумента в адреса ячеек второго блока 19 памяти связаны с тем, что любые значения аргумента можно привести к значениям в пределах первого квадранта (от О до ). Кроме того, преобразователь кода аргумента формирует код, соответствующий организации второго блока памяти.

Начальные значения аргумента определяются во втором сумматоре 11, в третьем блоке 12 памяти, третьем сумматоре 13 и четвертом блоке 14 памяти.

Передача начальных значений аргумента из четвертого блока 14 памяти в пятый блок 18 памяти осуществляется через коммутатор 15 по командам из формирователя 9 управляющих импульсов. С помощью счетчика 17, четвертого сумматора 16, коммутатора 15 и пятого блока 18 памяти формируется код аргумента.

Из пятого блока 18 памяти код аргумента передается в преобразователь 20 кода, из которого выдаются коды адресов ячеек второго блока 19 памяти и отдельно знаки синусов.

Рассмотрим формирование кода аргумента.

На вход счетчика от формирователя 9 управляющих импульсов поступают импульсы с частотой взятия отсчетов (частотой дискретизации). Состояние этого счетчика показывает номер отсчета т, который в данный момент обрабатывается. Произведение m Д t представляет собой дискретное время демодулятора. Аргумент первой гармоники в долях периода равен

F At m JD iДля выбранного конкретного значения

-X 64 этот аргумент равен

At

-6

ш-2 Аргументы следующих (более высоких) к-ых гармоник частоты формируются путем 5 накопления значений номеров отсчетов в четвертом сумматоре 16 и пятом блоке 18 памяти. При этом формируются значения аргументов к-ых гармоник, равных

к-гп --4. Коды аргументов опорных колебаний канальных сигналов формируются путем сложения аргументов гармоник с начальным значением аргумента.

Код расстройки формируется в виде относительных двоичных чисел. Обозначим

, числа, соответствующие кодам относительной расстройки, через 8расстр - Тогда слагаемое аргумента, обусловленное расстройкой частоты, равно

Д f m Д t SpaccT -f. Значения относительной расстройки 6расст).

0 формируются во. втором сумматоре 11 и третьем блоке 12 памяти.

Анализатор 10 смещения частоты определяет разность между смещением частоты в канале связи и величиной Д1, на которую

5 смещены частоты опорных колебаний.

Указанная разность выдается анализатором 10 смещения- частоты в виде двоичных чисел. Коды приращений расстройки из анализатора 10 смещения частоты поступают на входы второго су.мматора II и

0 третьего блока 12 памяти. Накопление приращений расстройки происходит за счет того, что выход третьего блока 12 памяти соединен со вторым входом второго сумматора 11. На каждом щаге подстройки частоты анализатор 10 смещения частоты вырабатывает код приращения расстройки и производится фиксация нового значения расстройки в виде относительной величины , равной сумме старого значения расстройки и найденной в анализаторе 10 смед щения частоты величины приращения расстройки. При этом могут учитываться как незначительные величины отклонения частоты, так и большие отклонения, равные, например, интервалу между частотами канальных сигналов. Возможность отработки точных значений смещения частоты, а не величин пропорциональных расстройке, позволяет повысить скорость подстройки частоты.

В процессе подстройки в третьем блоке 12

Q памяти формируются числа 5, соответствующие сумме относительной расстройки частоты 6расстр.- и начального значения аргумента, численно равного Kj , где К| - номер гармоники F - частоты первого канального сигнала f( () или & 6о +

5 +брасст/х де (5о к, - 1.

Значения величин расстройки накапливаются в третьем сумматоре 13 и четвертом блоке 14 памяти. Наопление производится по командам из формирователя 9 управляющих импульсов, которые поступают на управляющий вход четвертого блока 14 памяти.

Таким образом, коды аргументов опорных колебаний, каналбных сигналов для каждого отсчета группового сигнала формируются следующим образом.

Сначала в третьем сумматоре 13 и четвертом блоке 14 памяти к ранее накопленному значению (т-1)6 прибавляется величина S (по команде на управляющий вход четвертого блока 14 памяти) и формируется величина тб.

Затем код величины тб через коммутатор 15 передается в пятый блок 18 памяти. Одновременно в счетчик 17 прибавляется один импульс и этот счетчик из состояния m-1 переходит в состояние т. Затем код, находящийся в счетчике 17 (величина гп), прибавляется через четвертый сумматор 16 к величине, находящейся в пятом блоке 18 памяти. При этом в пятом блоке 18 памяти оказывается величина m-f mS . Эта величина соответствует коду аргумента первого канала. Действительно, код аргумента первой гармоники в долях периода равен гп--, начальное значение кода аргумента равно 6-m4.

Выше указывалось, что - 2 Код аргумента опорного колебания первого канала равен (m-f т6) х2. Умножение на величину 2 (или сдвиг величины ш-+-т6 на п разрядов) осуществляется соответствующей коммутацией при соединении пятого блока 18 памяти с преобразователем 20 кода. По величине т + тб в преобразователе 20 кода формируется код адреса второго блока 19 памяти и знак синуса. После этого происходит перемножение отсчета группового сигнала на отсчеты опорных колебаний.

Для формирования кода аргумента второго канала в пятом блоке 18 памяти снова добавляется величина m из счетчика 17. В пятом блоке 18 памяти оказывается величина 2т + т&, которая соответствует коду аргумента второго канала демодулятора. Этот процесс продолжается до конца обработки всех каналов демодулятора, после чего цикл повторяется с новым значением номе;ра отсчета.

Рассмотрим теперь работу преобразователя 20 кода.

Прежде всего отметим, что целые части кода (значащие цифры слева от запятой), поступающего на его вход могут не учитываться и отбрасываются. Старщие два разряда справа от запятой указывают номер квадранта, причем, старщий из них указывает знак синуса. Покажем, что младщий разряд из двух старщих разрядов указывает на необходимость перекодирования кода аргумента в дополнительный код. Для этого

рассмотрим четыре варианта сочетания цифр первых двух разрядов кода аргумента.

sin21i(+cA) sin(| -f25i;o(-) sin( - 2Xct) sin2(l-4ct)

Величина (1-4oC) представляет собой значение 4 в дополнительном коде. Поэтому для получения кода адреса ячеек второго блока памяти необходимо младшие разряды (начиная с третьего после запятой) аргумента перевести в дополнительный код. Знак синуса положителен.

sin(0,5 + A) 2Х -з1п2лы Код адреса ячеек второго блока памяти равен коду аргумента. Знак синуса отрицателен.

sin2ru(-i- +ot) (- -2 гл)1 -sin2A(l-4с().

Для получения кода адреса необходимо аргумент перевести в дополнительный код. Знак синуса отрицателен.

В преобразователе 20 кода перевод в дополнительный код осуществляется блоком 23 кодирования. Преобразование в дополнительный код может выполняться либо сумматором, либо другими логическими схемами. К оммутация аргумента в дополнительный код или прямо на вход второго блока 19 памяти синусов осуществляется многоразрядными переключателем 21.

В соответствии с алгоритмами работы демодулятора при обработке синфазного подканала отсчеты группового сигнала следует умножать на синусы аргументов, а при обработке квадратурных подканалов - на косинусы аргументов. Второй блок 19 памяти выдает значение косинуса аргумента, если при формировании адреса ячеек второго блока 19 памяти ко второму справа от запятой разряду кода аргумента прибавить единицу.

Добавление единицы осуществляется в двухразрядном сумматоре 22. На второй вход этого сумматора из формирователя 9 управляющих импульсов выдается код 0,00 для синфазного подканала и 0,01 - для квадратурного.

В предлагаемом демодуляторе непосредственно измеряется смещение частоты, что позволяет производить подстройку частоты не путем регулирования частоты по кольцу обратной связи, а точной установкой измеренной величины расстройки. Это позволяет уменьшить время вхождения в синхронизм по несущим частотам и улучшить отслеживание быстрых изменений смеш.ения частоты, обусловленных, например, эффектом Допплера. Формула изобретения . Демодулятор сигналов с фазоразностной модуляцией, содержащий последовательно соединенные аналого-цифровой преобразователь, первый перемножитель, первый сумматор, первый блок памяти, блок вычисления разности фаз и блок декодирования, последовательно соединенные блок синхронизации и формирователь управляющих импульсов, выходы которого подключены к управляющим входам первого блока памяти, первого сумматора, первого перемножителя и аналого-цифрового преобразователя, информационный вход и второй выход которого соединен соответственно со входом блока синхронизации и первым входом второго перемножителя, выход которого подключен ко второму входу первого перемножителя, а также второй блок памяти и анализатор смещения частоты, отличающийся тем, что, с целью повыщения помехоустойчивости, в него введены коммутатор, второй, третий и четвертый сумматоры, счетчик, третий, четвертый и пятый блоки памяти и преобразователь кода, выход которого подключен ко входу второго блока памяти, выход которого соединен с третьим входом первого перемножителя, причем второй выход блока вычисления разности фаз и выход блока декодирования соединены со входами анализатора смещения частоты, выходы которого подключены к первым входам третьего блока памяти и второго сумматора, выход которого соединен со вторым входом третьего блока памяти, выход которого подключен ко второму входу второго сумматора и, одному из входов третьего сумматора, выход которого соединен со входом четвертого блока памяти, выходы которого подключены к другим входам третьего сумматора и входам коммутатора, выходы которого соединены со входами пятого блока памяти, выходы которого подключены к входам преобразователя кода и четвертого сумматора, выходы которого соединены с соответствующими входами коммутатора, при этом дополнительные выходы формирователя управляющих импульсов соединены с управляющими входами преобразователя кода, третьего, четвертого и пятого блоков памяти, коммутатора и счетчика, выход которого подключен к соответствующему входу четвертого сумматора, а соответствующий выход преобразователя кода соединен со вторым входом второго перемножителя. 2. Демодулятор по п. 1, отличающийся тем, что преобразователь кода содержит блок кодирования и последовательно соединенные двухразрядный сумматор и многоразрядный переключатель, соответствующие входы которого соединены со входом и выходом блока кодирования, причем первый вход двухразрядного сумматора и вход блока кодирования являются входами преобразователя кода, управляющим входом и выходом которого являются соответственно второй вход двухразрядного сумматора и выход многоразрядного переключателя. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 540404, кл. Н 04 L 27/22, Н 04 J 11/00, 1974 (прототип).

Авторы

Даты

1982-08-07—Публикация

1980-04-30—Подача