1

Изобретение относится к аналоговой н аналого-цифровой вычислительной технике, aiBTOматике и телеметрии.

Известны переключатели аналоговых сигналав, содержащие ключевые и вправляющие МОП-тра«зи1Сторы и схему управления.

Однако в таких переключателях на вход управляющего МОП-транзистора необходимо подавать относительно больщой уровень напряжения (а шлитуда управляющего напряжения зависит от величины порогового напряжения и положительного ИСточни1ка питания), который не согласуется с ур01в;ня:МИ напряжений биполярных ДТЛ и ТТЛ, поскольку последние выполняются в основном на основе биполярных транзисторов п-р-п типа проводимости и имеют выходные уровни напряжений положительной лолярности.

Цель изобретения-согласование схемы управления ключевым МОП-транзистором с логическими биполярными диодно-транзисторньши (ДТЛ) или Т1ранзисторн-о-транзисторньшн (ТТЛ) схемами и повыщение стабильности работы переключателя при технологическом разбросе порогового напряжения.

Для этого в схему упра-вления вводят инвертор, вход которого подсоединен к средней точке двух последовательно-соединенных МОП-резисторов, включенных между отрицательныМ полюсом источника по1стоянного напряжения и управляющим входом. Выход инвертора подсоединяют к затвору управляющего МОП-транзистора, исток которого подключен к управляющему входу переключателя. Кроме того, в схему управления вводят дополнительный МОП-транзистор, подключенный параллельно выходу инвертора, затвор которого подсоединен к отрицательному полюсу источника постоянного напряжения.

В результате этого, напряжение на затворе управляющего МОП-транзистора повыщается с приходом управляющего положительного напряжения и понижается при отсутствии его. При этоМ напрялсение пропорционально увеличивается или уменьщается с увеличением или уменьшением порогового напряжения.

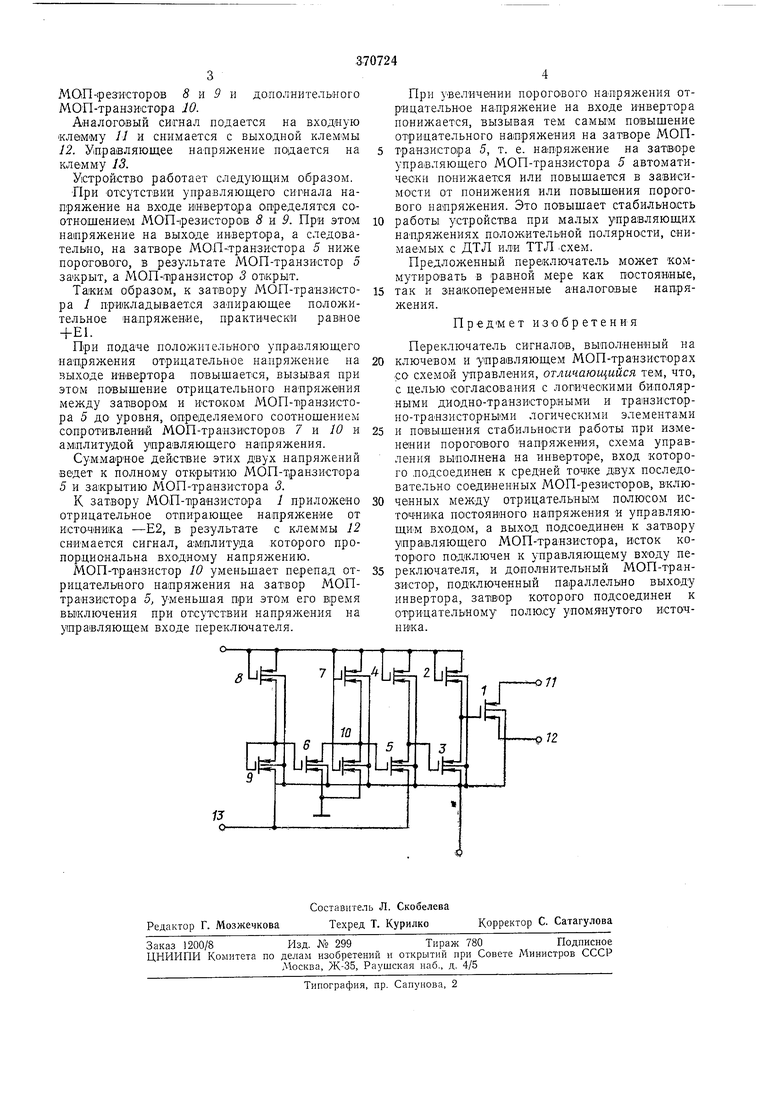

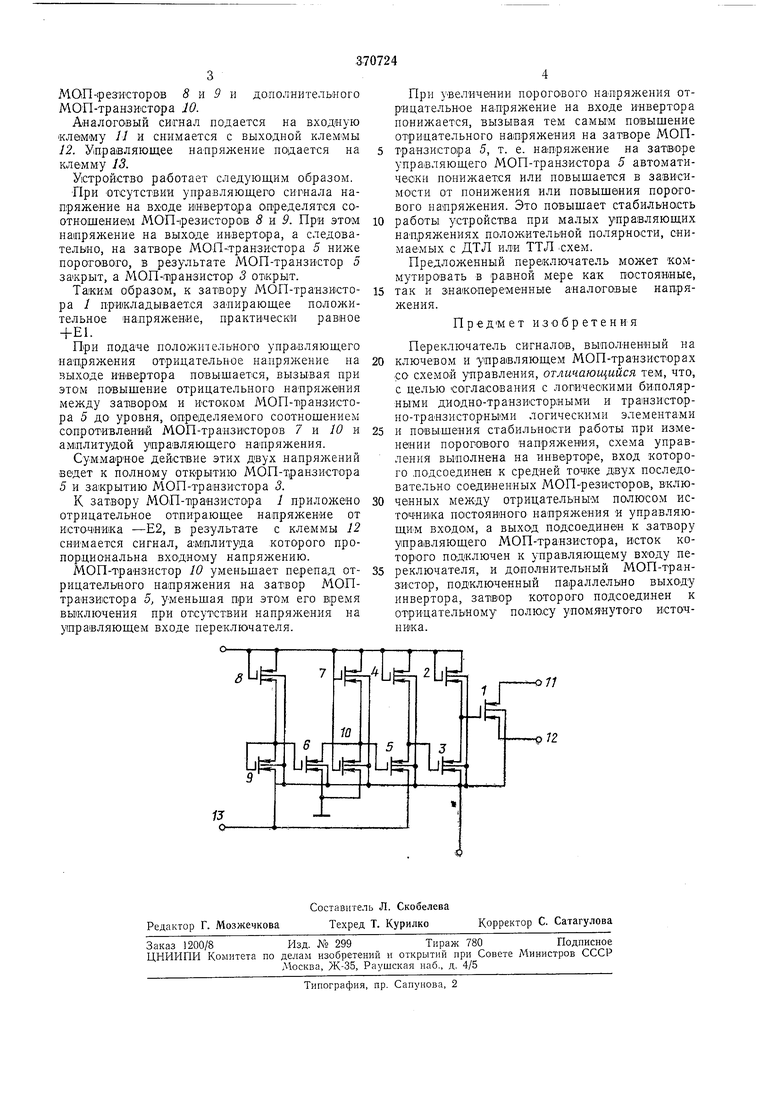

На чертеже представлен предлагаемый переключатель.

Он содержит ключевой МОП-транзистор /, затвор которого через МОП-транзистор 2 соединен с положительным полюсом источника постоя-нного напряжения +Е1.

Затвор транзистора 3 подключен к средней

точке последовательно-соединенных нагрузочного МОП-транзистора 4 и управляющего МОП-транзистора 5, цепь управления которых состоит из ин1вертора, содержащего МОПтранзисторы 6 и 7, вход которых подключен

к средней точке последовательно соединенных

МОПнрезИсторов S и 5 и дополнительного МОП-транзистора 10.

Аналоговый сигнал подается на входную «лемму 11 и снимается с выходной клеммы 12. Управляющее напряжение подается на клемму 13.

Устройство работает следующим образом.

При Отсутствии управляющего сигнала напряжение на входе инвертора определятся соотношением МОП-резисторов 5 и Р. При этом напряжение на выходе инвертора, а следовательно, на затворе МОП-транзистора 5 ниже поротавого, в результате МОП-транзистор 5 закрыт, а МОП-1Т1ранзистор 3 открыт.

Таким образом, к затвору МОП-транзистора / прикладывается забирающее положительное налряжение, практически равное +Е1.

При подаче положительного управляющего напряжения отридательное напряжение на выходе инвертора повышается, вызывая при этом повышение отрицательного напряжения между затвором и истоком МОП-транзистора 5 до уровня, определяемого соотношением сопроти-влений МОП-транзисторов 7 и /( и ам1плитудой управляющего напряжения.

Суммарное действие этих двух напряжений ведет к полному открытию МОП-транзистора 5 и закрытию МОП-транзистора 3.

К затвору МОП-траизистора 1 приложено отрицательное отпирающее напряжение от источника -Е2, в результате с клеммы 12 снимается сигнал, амплитуда которого пропорциональна входному напряжению.

МОП-транзистор 10 уменьшает перепад отрицателБното напряжения на затвор М.ОПтранзистора 5, уменьшая при этом его время выключения при отсутствии напряжения на управляющем входе переключателя.

При увеличении порогового напряжения отрицательное налряжение на входе инвертора понижается, вызывая тем самым повышение отрицательного напряжения на затворе МОПтранзистора 5, т. е. напряжение на затворе управляющего МОП-транзистора 5 автоматически понижается или повышается в зависимости от понижения или повышения порогового напряжения. Это повышает стабильность

работы устройства при малых упра)вляюших напряжениях положительной полярности, снимаемых с ДТЛ или ТТЛ схем.

Предложенный пере ключатель может коммутировать в равной мере как постоянные,

так и знакопеременные аналоговые напряжения.

Предмет изобретения

Переключатель сигналов, выполненный на

ключевом и управляющем МОП-транзисторах со схемой управления, отличающийся тем, что, с целью согласования с логическими биполярными диодно-транзисториыми и транзисторно-транзисторными логическими элементами

и повышения стабильности работы при изменении порогового напряжения, схема управления выполнена на инверторе, вход которого подсоединен к средней точке двух последовательно соединенных МОП-резисторов, включенных между отрицательным полюсом источника постоянного напряжения и управляющим входом, а выход подсоединен к затвору управляющего МОП-транзистора, исток которого подключен к управляющему входу переключателя, и дополнительный МОП-транзистор, подключенный параллельно выходу инвертора, затвор которого подсоединен к отрицательному полюсу упомянутого источника.

| название | год | авторы | номер документа |

|---|---|---|---|

| Переключатель | 1974 |

|

SU540377A1 |

| Моп-ттл транслятор | 1979 |

|

SU836797A1 |

| ПЕРЕКЛЮЧАТЕЛЬ АНАЛОГОВЫХ СИГНАЛОВI псссоюгнАяir:u:i;TriD-Ta:;i--ij{/i?i: L...^i!lr^:l:5'^I^'^^ i | 1971 |

|

SU304694A1 |

| Многоразрядный управляемый магазин сопротивлений | 1982 |

|

SU1173542A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU858110A1 |

| СОГЛАСУЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU327610A1 |

| Формирователь импульсов на моп-транзисторах | 1978 |

|

SU790335A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕКЛЮЧЕНИЯ ЗНАКОПЕРЕМЕННЫХ АНАЛОГОВЫХ СИГНАЛОВ | 1973 |

|

SU385287A1 |

| Устройство сопряжения биполярных и МДП логических устройств | 1974 |

|

SU591091A1 |

| Многоканальный коммутатор аналоговых сигналов | 1982 |

|

SU1034183A1 |

Даты

1973-01-01—Публикация