(54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРС СТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1974 |

|

SU510752A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU890440A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU875465A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU729642A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1108508A1 |

| Ячейка аналоговой памяти | 1977 |

|

SU733031A1 |

| Аналого-цифровой интегратор | 1977 |

|

SU732905A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1140178A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU868840A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU991514A1 |

1

Изобретение относится к области запоминающих устройств и может быть использовано, например в измерительной текнике и устройствах автоматики.

Известно аналоговое запоминающее устройство, в котором ключи и усилители выполнены на МОП-транзисторах Щ .

Однако сложность схемного выполнения устройства ограничивает его область применения.

Наиболее близким по технической сущности к предлагаемому является аналого-вое запоминающее устройство, содержащее элемент сравнения, один из входов которого соединен с входной шиной устройства, ключевой элемент, управляющий вход которого соединен с шиной управления, а его вход соединен с выходом элемента сравнения, повторитель напряжения, ко входу которого подключен накопительный элемент, например конценсатор, другая обкладка которого соединена с шиной нулевого потенциала 23.

Однако данное устройство не позволяет запоминать минимальные значения аналогового сигнала. Кроме того, оно схемотехнически сложно.

Цель изобретения - расширение области применения устройства за счет увеличения динамического диапазона входного сигнала и .его упрощение.

Поставленная цель достигается тем, что в аналоговом запоминающем устрой10стве, содержащем накопительный элемент, например конденсатор, одна обкладка которого соединена с шиной нулевого потенциала, элемент сравнения, один из входовкоторого подключен ко входу устройства,

IS ключ, выполненный на первом МОП-транзисторе, исток которого соединен с выходом элемента сравнения, повторитель напряжения, выполненный на втором МОПтранзисторе, затвор которого соединен

20 с другой обкладкой .конденсатора и первым выходом переключателя, пассивный элемент, шину управления, соединенную с затвором первого МОП-транзистора, и

3eS

шины питания, исток второго МОП-транэисгора подключен к выходу устройства, к другому входу элемента сравнении и через пассивный элемент к первой шине питания, подложка первого МОП-транзистора подсоединена ко входу переключателя, второй выход которого соединен с выходом элемента сравнения, сток второго -МОП-транзистора подключен ко второй шине питания.

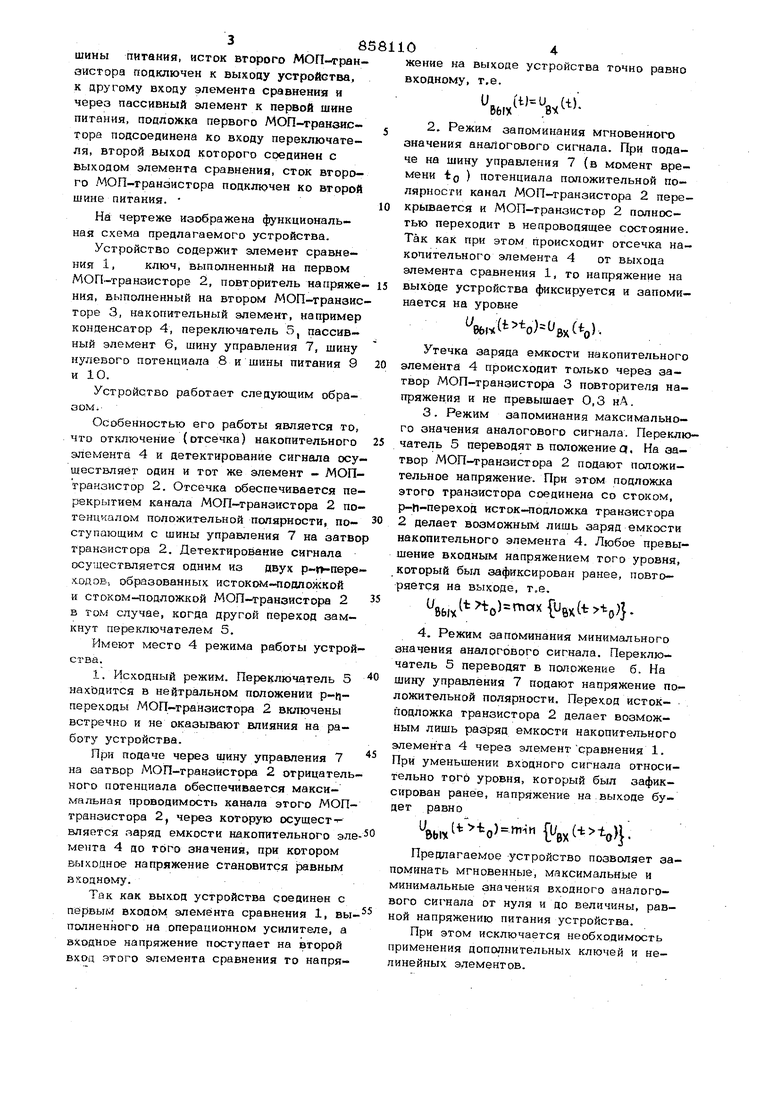

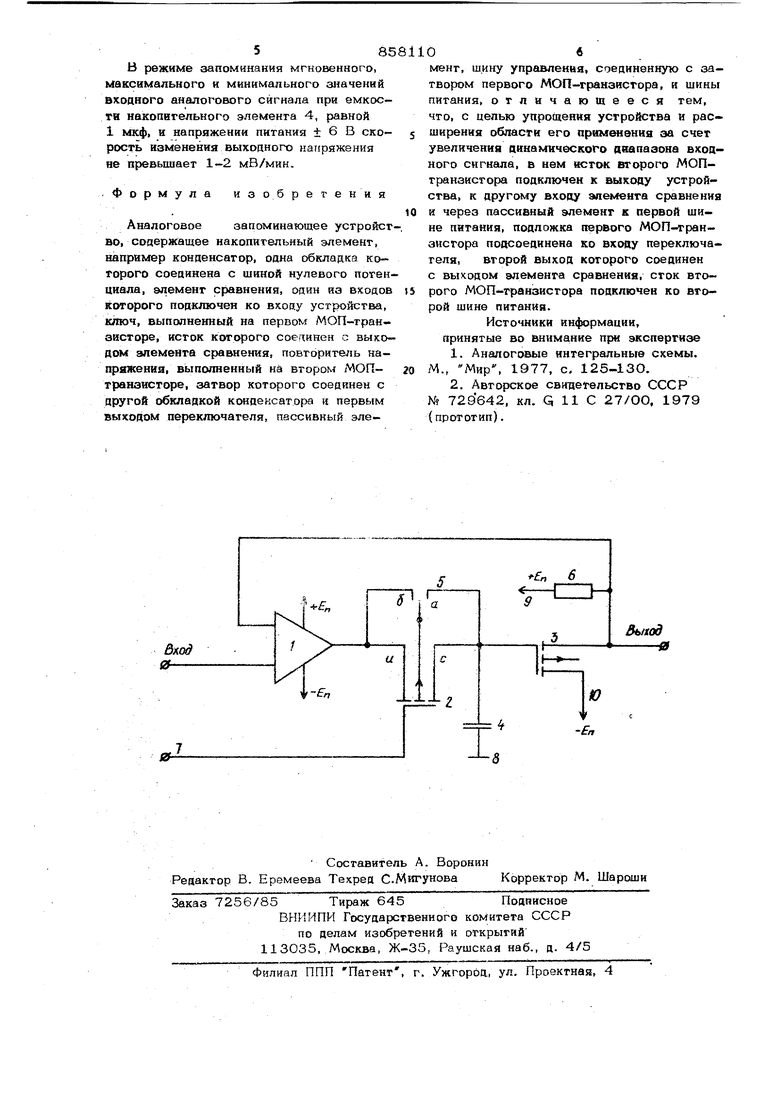

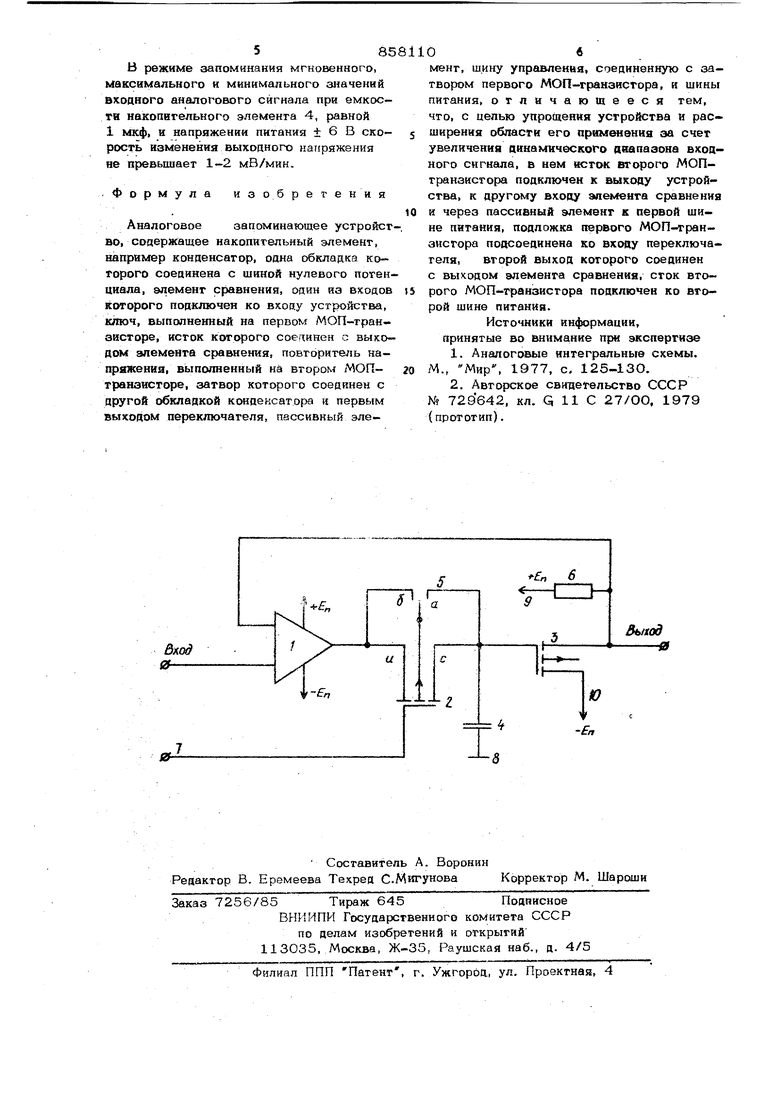

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит элемент сравнения 1, ключ, выполненный на первом МОП-транзисторе 2, повторитель напряжения, выполненный на втором МОП-транзисторе 3, накопительный элемент, например конденсатор 4, переключатель 5, пассивный элемент 6, шину управления 7, шину нулевого потенциала 8 и шины питания 9 и Ю.

Устройство работает следующим образом.

Особенностью его работы является то, что отключение (отсечка) накопительного элемента 4 и детектирование сигнала осуществляет один и тот же элемент - МОПтранзистор 2. Отсечка обеспечивается перекрытием канала МОП-транзистора 2 потенциалом положительной полярности, по- ступающим с шины управления 7 на затво транвистора 2. Детектирование сигнала осуществляется одним из двух р-г -переХОДОВ-, образованных истоком-подложкой н стоком-подложкой МОП-транзистора 2 в том случае, когда другой переход замкнут переключателем 5.

Имеют место 4 режима работы устройства.

При подаче через ыхину управления 7 на затвор МОП-транзистора 2 отрицательного потенциала обеспечивается максимальная проводимость канала этого МОПтранзистора 2, через которую осуществляется заряд емкости накопительного эле мента 4 до того значения, при котором выходное напряжение Становится равным входному.

Так как выход устройства соединен с первый входом элемента сравнения 1, выполненного на операционном усилителе, а входное напряжение поступает на второй вход этого элемента сравнения то напря04

жение на выходе устройства точно равно входному, т.е.

B6,x -V 2. Режим запоминания мгновенного значения аналогового сигнала. При подаче на шину управления 7 (в момент времени tg ) потенциала положительной полярносги канал МОП-транзистора 2 перекрьшается и МОП-транзистор 2 полностью переходит в непроводящее состояние. Так как при этом происходиг отсечка накопительного элемента 4 от выхода элемента сравнения 1, то напряжение на выходе устройства фиксируется и запоминается на уровне

iV,(,Og(i).

Утечка заряда емкости накопительного элемента 4 происходит только через затвор МОП-транзистора 3 повторителя напряжения и не превышает 0,3 нА.

)«{% 0 }

ftbix - o)- .

Предлагаемое устройство позволяет запоминать мгновенные, максимальные и минимальные значения входного аналогового сигнала от нуля и до величины, равной напряжению питания устройства.

При этом исключается необходимость применения дополнительных ключей и нелинейных элементов. 585 В режиме запоминания мгновенного, максимального и минимального значений вкодного аналогового сигнала при емкости накопигельного элеменга 4, равной 1 мкф, и напряжении питания ± 6 В ско- рость изменения выходного напряжения не превышает 1-2 мВ/мин. Формула изобретения Аналоговое зааоминающее устройсг во, содержащее накопительный элемент, например конденсатор, одна обкладка которого соединена с шиной нулевого потен циала, элемент сравнения, один из вкодов которого подключен ко входу устройства, ключ, выполненный на первом МОП-транзисторе, исток которого соегщнен с выходом элемента сравнения, повторитель напряжения, выполненный на втором МОПтранзисторе, затвор которого соединен с другой обкладкой конденсатора и первым выходом переключателя, пассивный эле0«мент, шину управления, соединенную с затвором первого МОП-транзистора, и шины питания, отличающееся тем, что, с целью упрощения устройства и расширения области его применения за счет увеличения пннамкческого аоапазона входного сигнЕша, в нем исток второго МОПтранзистора подключен к выкоду устройства, к другому входу элемента сравнения к через пассивный элемент к первой шине питания, подложка первого МОП-транзистора подсоединена ко входу переключагеля, второй выход которого соединен с выходом элемента сравнения, сток второго МОП-транзистора подключен ко второй шине питания. Источники информации, принятые во внимание при экспертизе 1.Аналоговые интегральные схемы. М., -Мир, 1977, с. 125-130. 2.Авторское свидетельство СССР N 729642, кл. Q 11 С 27/ОО. 1979 (прототип).

Вхо 0

Выход 0

ю

:bZ

Авторы

Даты

1981-08-23—Публикация

1979-11-02—Подача