Изобретение относится к импульсной технике.

Известно декадное пересчетное устройство, реализованное на транзисторно-транзисторных элементах, содержащее триггеры, а также входной логический блок, выполненный на основе схем «И-НЕ.

Недостатком этого устройства является ограниченность его функциональных возможностей.

Цель изобретения - расширение функциональных возможностей устройства, а также сокращение внешних связей за счет использования фазоимпульсного представления информации.

Достигается она тем, что предлагаемое устройство содержит выходной формирователь, выполненный на основе схемы «И-НЕ, один из входов которой подключен к счетному входу декады, а остальные входы соединены с единичными выходами первого и четвертого триггеров, выход схемы «И-НЕ соединен с шиной выходного сигнала, причем шипа счетных импульсов через инвертор и шина управляющих импульсов непосредственно подключены ко входу схемы «И-НЕ входного логического блока, выход которой соединен с одним из входов другой схемы «И-НЕ, второй вход которой подключен к шине синхронизирующих импульсов, а выход - к счетному входу декады.

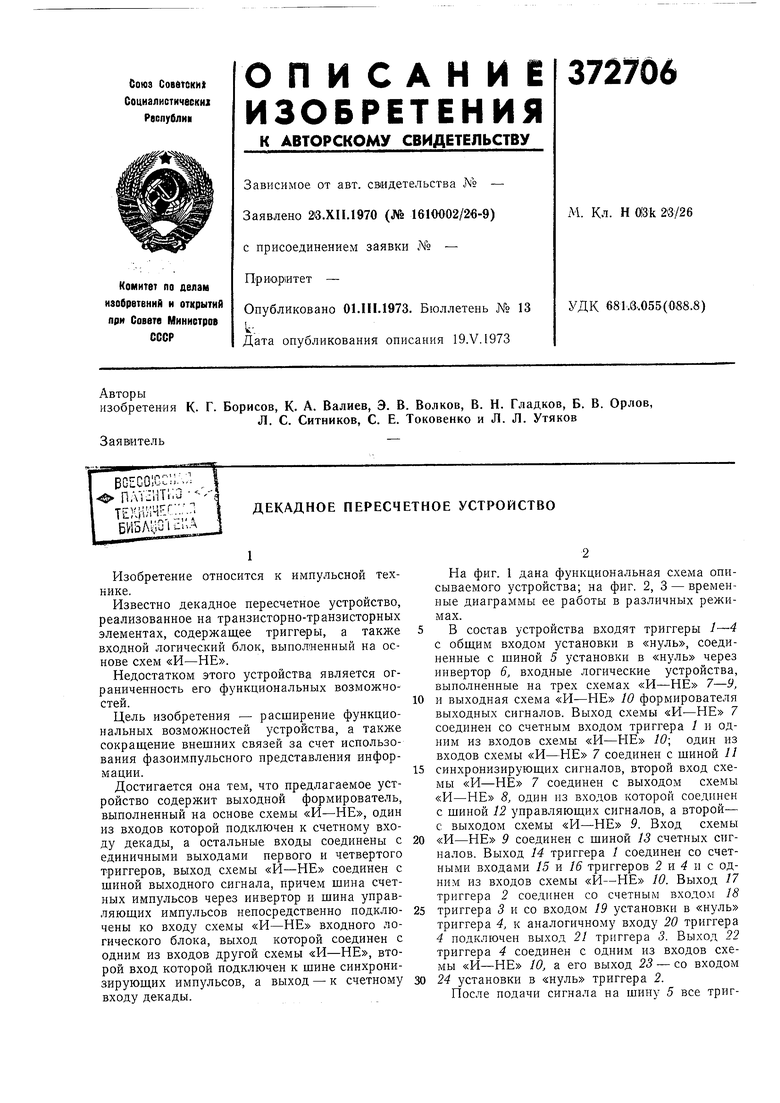

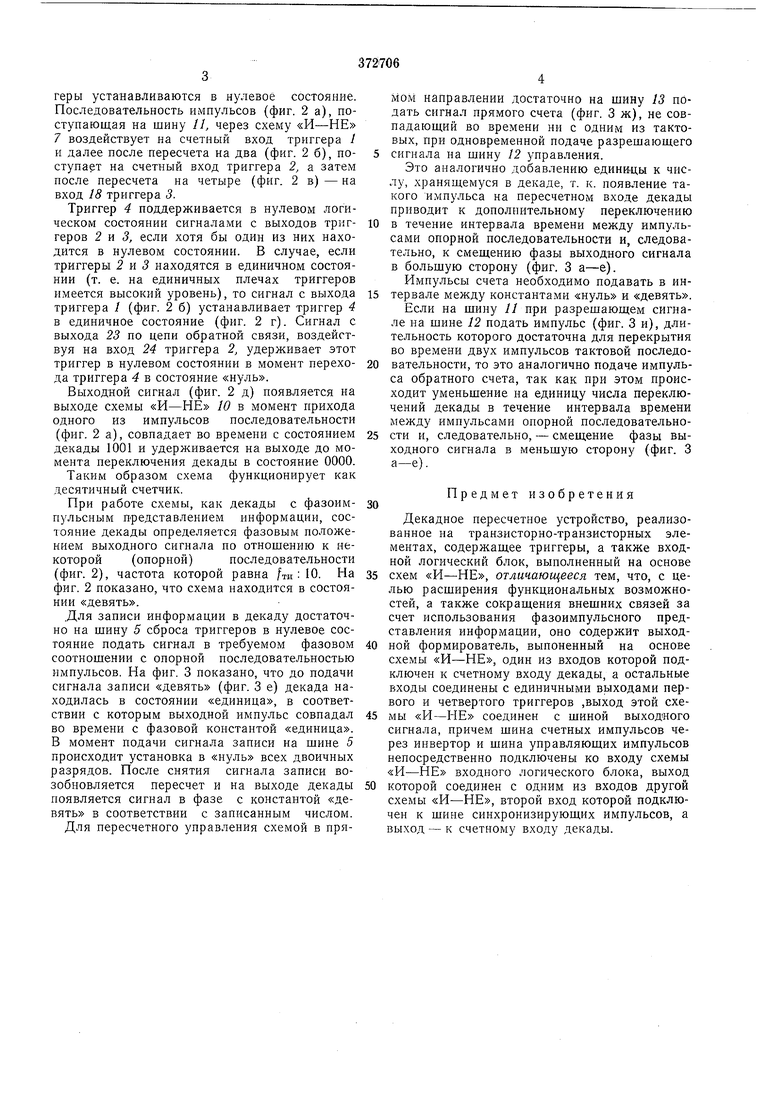

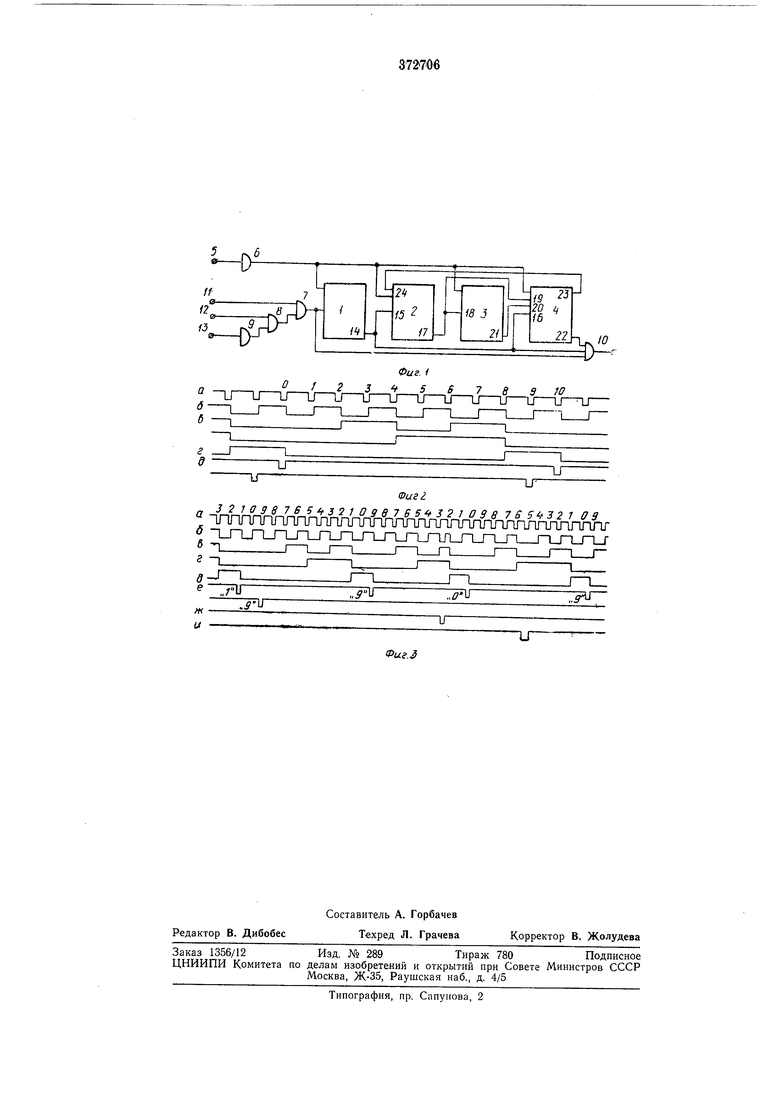

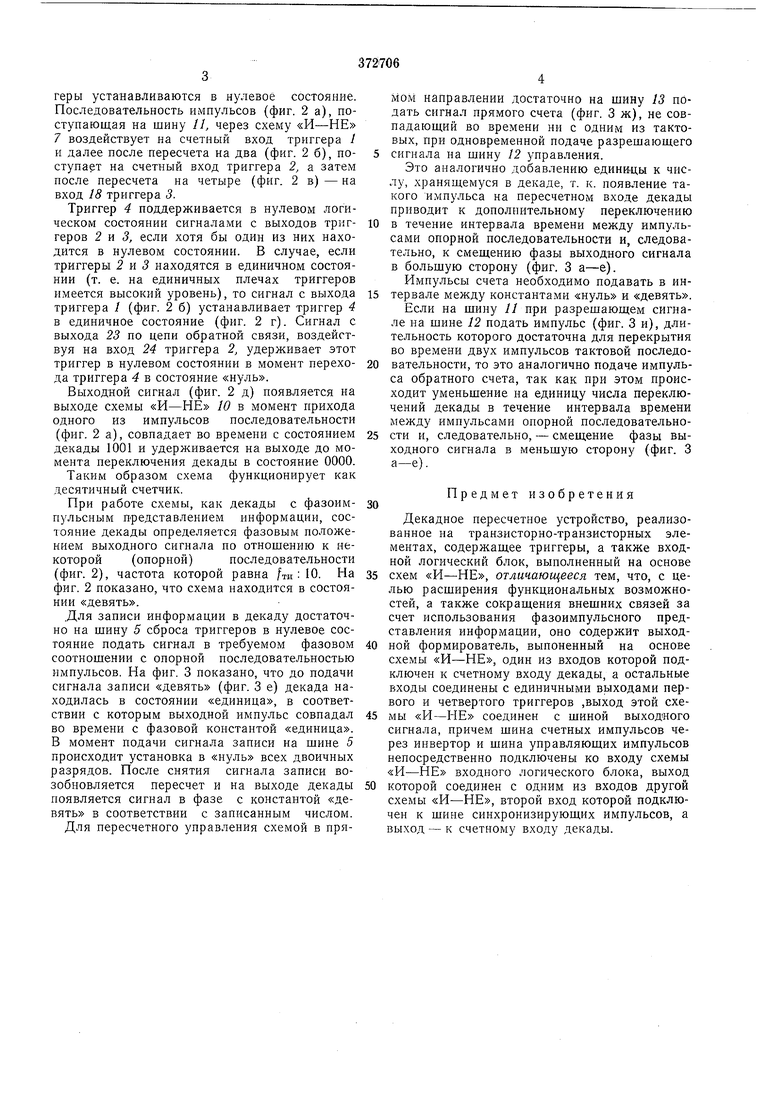

На фиг. 1 дана функциональная схема описываемого устройства; на фиг. 2, 3 - временные диаграммы ее работы в различных режимах.

В состав устройства входят триггеры 1-4 с общим входом установки в «нуль, соединенные с шиной 5 установки в «нуль через инвертор 6, входные логические устройства, выполненные на трех схемах «И-НЕ 7-9,

и выходная схема «И-НЕ 10 формирователя выходных сигналов. Выход схемы «И-НЕ 7 соединен со счетным входом триггера / и одним из входов схемы «И-НЕ 10; один из входов схемы «И-НЕ 7 соединен с шиной 11

синхронизируюших сигналов, второй вход схемы «И-НЕ 7 соединен с выходом схемы «И-НЕ 8, один из входов которой соединен с шиной 12 управляющих сигналов, а второй- с выходом схемы «И-НЕ 9. Вход схемы

«И-НЕ 9 соединен с шиной 13 счетных сигналов. Выход 14 триггера 1 соединен со счетными входами 15 и 16 триггеров 2 и 4 и с одним из входов схемы «И-НЕ 10. Выход 17 триггера 2 соединен со счетным входом 18

триггера 3 и со входом 19 установки в «нуль триггера 4, к аналогичному входу 20 триггера 4 подключен выход 21 триггера 3. Выход 22 триггера 4 соединен с одним из входов схемы «И-НЕ 10, а его выход 23 - со входом

24 установки в «нуль триггера 2.

После подачи сигнала на шину 5 все триггеры устанавливаются в нулевое состояние. Последовательность имнульсов (фиг. 2 а), ноступающая на шину //, через схему «И-НЕ

7воздействует на счетный вход триггера / и далее после пересчета на два (фиг. 2 б), ноступает на счетный вход триггера 2, а затем после пересчета на четыре (фиг. 2 в) - на вход 18 триггера 3.

Триггер 4 поддерживается в нулевом логическом состоянии сигналами с выходов триггеров 2 и 3, если хотя бы один из них находится в нулевом состоянии. В случае, если триггеры 2 и 3 находятся в единичном состоянии (т. е. на единичных плечах триггеров имеется высокий уровень), то сигнал с выхода триггера / (фиг. 2 б) устанавливает триггер 4 в единичное состояние (фиг. 2 г). Сигнал с выхода 23 по цепи обратной связи, воздействуя на вход 24 триггера 2, удерживает этот триггер в нулевом состоянии в момент перехода триггера 4 в состояние «нуль.

Выходной сигнал (фиг. 2 д) появляется на выходе схемы «И-НЕ 10 в момент прихода одного из импульсов последовательности (фиг. 2 а), совпад;ает во времени с состоянием декады 1001 и удерживается на выходе до момента переключения декады в состояние 0000.

Таким образом схема функционирует как десятичный счетчик.

При работе схемы, как декады с фазоимпульсным представлением информации, состояние декады определяется фазовым положением выходного сигнала по отношению к некоторой (опорной)последовательности (фиг. 2), частота которой равна f™ : Ю. На фиг. 2 показано, что схема находится в состоянии «девять.

Для записи информации в декаду достаточно на шину 5 сброса триггеров в нулевое состояние подать сигнал в требуемом фазовом соотношении с опорной последовательностью импульсов. На фиг. 3 показано, что до подачи сигнала записи «девять (фиг. 3 е) декада находилась в состоянии «единица, в соответствии с которым выходной импульс совпадал во времени с фазовой константой «единица.

8момент подачи сигнала записи на шине 5 происходит установка в «нуль всех двоичных разрядов. После снятия сигнала записи возобновляется пересчет и на выходе декады появляется сигнал в фазе с константой «девять в соответствии с записанным числом.

Для пересчетного управления схемой в прямом направлении достаточно на шину 13 подать сигнал прямого счета (фиг. 3 ж), не совпадающий во времени ни с одним из тактовых, при одновременной подаче разрешаюш,его сигнала на шину 12 управления.

Это аналогично добавлению едини.цы к числу, хранящемуся в декаде, т. к. появление такого импульса на пересчетном входе декады приводит к дополнительному переключению

в течение интервала времени между импульсами опорной последовательности и, следовательно, к смещению фазы выходного сигнала в большую сторону (фиг. 3 а-е). Импульсы счета необходимо подавать в интервале между константами «нуль и «девять. Если на щину // при разрешающем сигнале на шине 12 подать импульс (фиг. 3 и), длительность которого достаточна для перекрытия во времени двух импульсов тактовой последовательности, то это аналогично подаче импульса обратного счета, так как при этом происходит уменьшение на единицу числа переключений декады в течение интервала времени между импульсами опорной последовательности и, следовательно, - смещение фазы выходного сигнала в меньшую сторону (фиг. 3 а-е).

Предмет изобретения

Декадное пересчетное устройство, реализованное на транзисторно-транзисторных элементах, содержащее триггеры, а также входной логический блок, выполненный на основе

схем «И--НЕ, отличающееся тем, что, с целью расщирения функциональных возможностей, а также сокращения внещних связей за счет использования фазоимпульсного представления информации, оно содержит выходной формирователь, выпоненный на основе схемы «И-НЕ, один из входов которой подключен к счетному входу декады, а остальные входы соединены с единичными вь1ходами первого и четвертого триггеров ,выход этой схемы «И-НЕ соединен с шиной выходного сигнала, причем шина счетных импульсов через инвертор и шина управляющих импульсов непосредственно подключены ко входу схемы «И-НЕ входного логического блока, выход

которой соединен с одним из входов другой схемы «И-НЕ, второй вход которой подключен к шине синхронизирующих импульсов, а выход - к счетному входу декады.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пересчетное устройство | 1982 |

|

SU1046935A1 |

| СЧЕТЧИК С ПРЕДВАРИТЕЛЬНОЙ УСТАНОВКОЙ | 1971 |

|

SU322855A1 |

| Часы на многоустойчивых элементах с цифровой индикацией | 1978 |

|

SU769481A1 |

| ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1973 |

|

SU383085A1 |

| Цифровое фазосдвигающее устройство | 1984 |

|

SU1241148A1 |

| Устройство для формирования временных интервалов | 1976 |

|

SU564714A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| РЕВЕРСИВНАЯ ПЕРЕСЧЕТНАЯ ДЕКАДА | 1969 |

|

SU238249A1 |

| Фазоимпульсный реверсивный счетчик | 1981 |

|

SU951714A1 |

| УПРАВЛЯЕМЫЙ ДЕКАДНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1970 |

|

SU270354A1 |

„ 321038 76Sff3210ffe765 32 Offe 09 1Г1ЛГ1Г1Г 1ЛЛГ1ЛЛППЛЛГ1Г1

TFir

ж

Фиг 2.

T lrT ir

Даты

1973-01-01—Публикация