Изобретение относится к дискретной обработке импульсных сигналов и может использоваться в таймерах, делителях частоты и т.д., требующих большого коэффициента пересчета

Известно пересчетное устройство, содержащее блоки усиления и отбора, блоки реверса, основные и буферные счетные декады, устройства индикации, ключи передачи, запоминающие декады, устройства считывания, устройства записи, причем выход буферных счетных декад соединен с первым счетным входом основной счетной Декады, потенциальные выходы которой через ключи передачи соединены с соответствующимивходами триггеров запоминания запоминающих декад, а потенциальные выходы триггеров запоминания запоминающих декад соединены с импульсными входами триггеров основной счетной декада, импульсный выход переполнения последней основной счетной декады соедине с входом установки в нуль всех триггеров запоминающих декад и входом устройства считывания, выход которого соединен с вторьам счетным входом первой основной счетной декады и входом устройства записи, выход которого соединен с входом устройства передачи кода и входом установки в нуль триггеров основной счетной декады Ci J.

Недостатками этого устройства являются большие аппаратурные затраты, возрастающие пропорционально tog- делает нерациональным построение таких устройств с (большим коэффициентом пересчета , а также сложное управление работой этогоустройства.

Известно пересчетное устройство, содержащие двоично десятичный счетчик и регистры хранения, элементы задержки, селектор, элемент ИЛИ и распределитель импульсов, причем выходы регистров соединены с входам селектора, выход селектор а соединен с входом двоично-десятичного счетчика, первые выходы элементов задержки соединены с управляющим входом считывания соответствующего регистра, вторые выходы элементов задержки соединены с управлякщими входс1ми записи соответствующих регистров и входами элемента ИЛИ, третьи выходы элементов задержки соединены с входом сброса двоично-десятичного счетчика, входы элементов задержки соединены с выходом распределителя импульсов, один вход элемента ИЛИ соединен с входом устройства и входом сброса распределителя импульсов выход элемента ИЛИ соединен со счетным входом двоично- десятичного счетчика, а выход переполнения двоичнодесятичного счетчика соединен с входом распределителя импульсов Г2.

Недостатками пересчетного устройства являются относительно низкое быстродействие и большие затраты аппаратуры, необходимой для его реализации.

Известно пересчетное устройство, содержащее элемент задержки, первый счетчик, э лeмeнт памяти, первый триггер, второй счетчик, второй триггер и элемент ИЛИ, первый вход которого соединен с выходом первого триггера, информационный вход которого соединен с выходом переноса второго счетчика, а выход - переноса первого счетчика соегдинен с входом сброса второго триггера Сз.

Недостаток устройства заключается в относительно низком быстродействии.

Цель изобретения - повышение быстродействия .

Поставленная цель достигается тем что в пересчетном устройстве,содержащем элемент ЭсЩержки., первый счетI

чик, элемент памяти, первый триггер. Второй счетчик, второй триггер и элемент ИЛИ, первый вход которого соединен с выходом первого триггера, информационный вход которого соединен с инверсным выходом переноса второго счетчика, а выход переноса первого счетчика соединен с входом сброса второго триггера, вход элемента задержки, который является входом пересчетного устройства, соединен с тактовым входом элемента памяти, тактовым входом первого триггера и иняверсным входом записи второго счетчика, информационные входы и выходы которого соединены соответственно с информационными выходами, и входами элемента памяти, адресный вход которого соединен с выходом первого счетчика, инверсный импульсный счетный вход которого соединен с первым выходом элемента задержки и вторым входом элемента ИЛИ, трютий вход и выход которого соединены соответственно с вторым выходом элемента задержки и импульсным счетным входом второго счетчика, вход сброса которого соединен с выходом второго триггера, установочный вход которого соединен с входом сброса первого счетчика, который является входом сброса пересчетного устройства, а выход парено са первого счетчика соединен с входо сброса первого триггера.

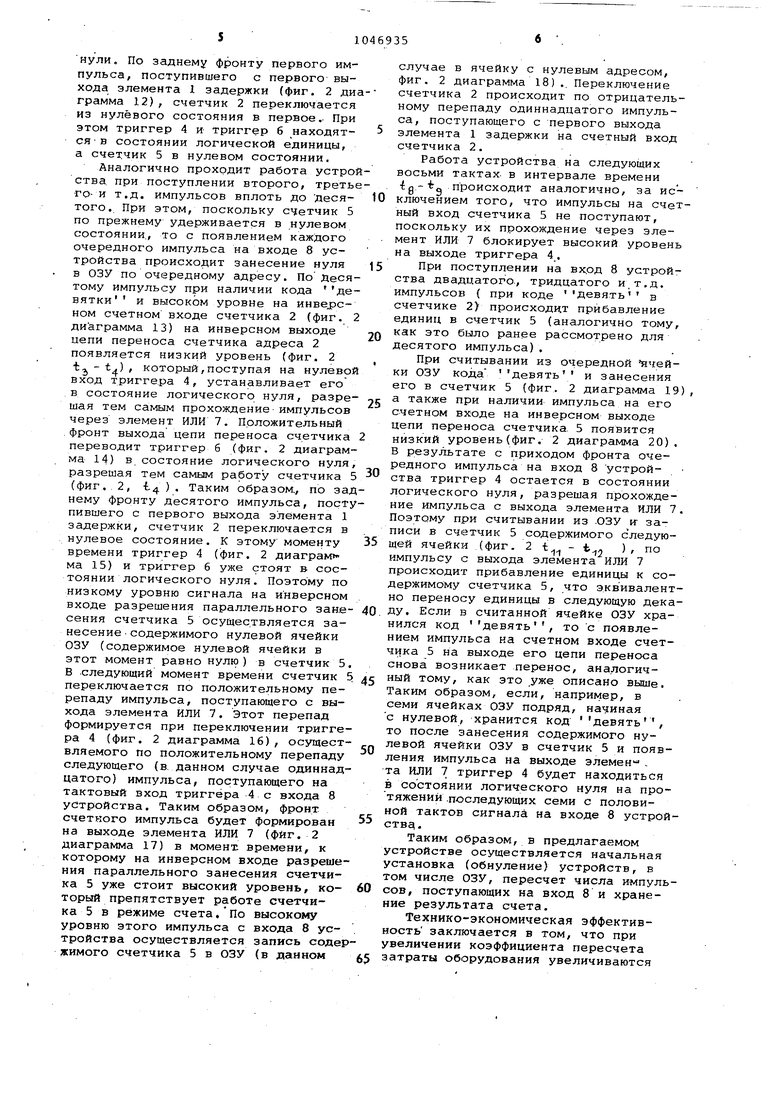

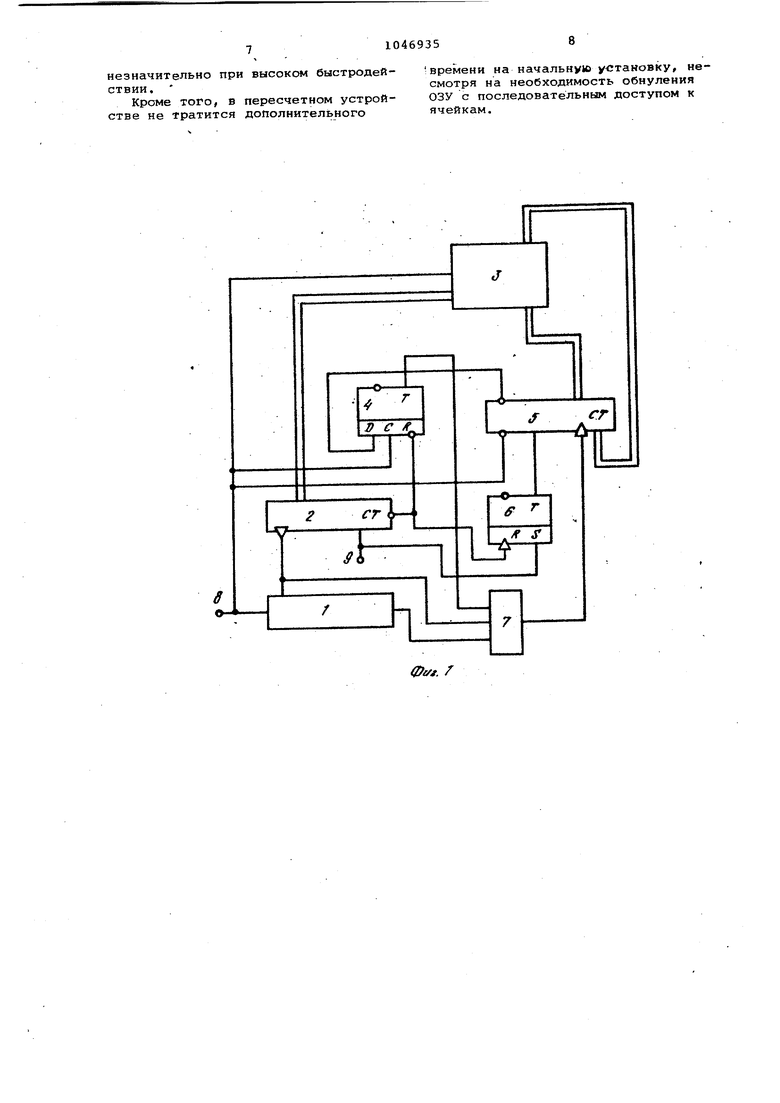

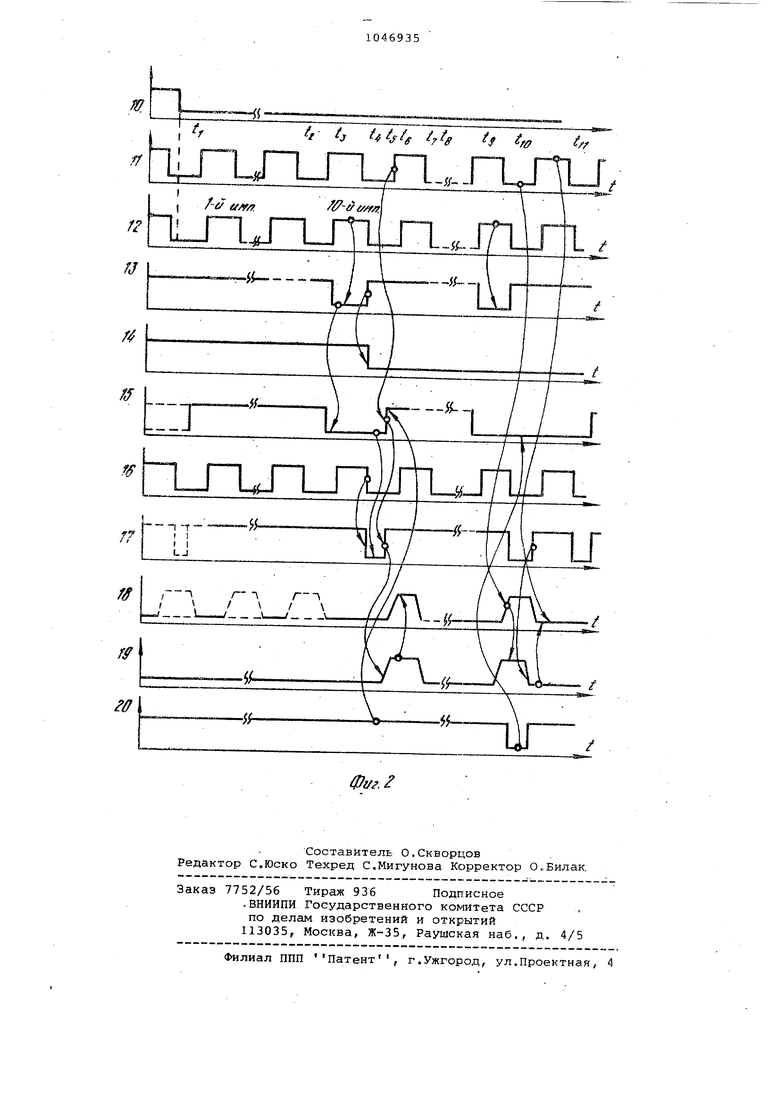

На фиг. 1 показана структурная схема пересчетного устройства j на фиг. 2 - временные диаграммы, поясняющие функционирование пересчетного .устройства.

Пересчетное устройство содержит элемент 1 задержки, первый счетчик 2 элемент 3 памяти, первый триггер 4,

второй счетчик 5, второй триггер б и элемент ИЛИ 7, первый вход которого соединен с выходом первого триггера 4, информационный вход которого соединен с инверсным выходом переноса второго счетчика 5, а выход переноса первого счетчика 2 соединен с входом сброса второго триггера 6, вход элемента задержки, который является входом 8 пересчетного устройства, соединен с тактовым входом элемента 3 памяти, тактовым входом . первого триггера 4 и инверснь1м входом запис-и второго счетчика 5, информационные входы и выходы которого соединены соответственно с информационными выходами и входами элемента 3 памяти, адресный вход которого соединен с выходом первого счетчика 2, инверсный импульсный счетный вход которого соединен с первым выходом элемента 1, задержки и вторым входом элемента ИЛИ 7,третий вход и выход которого соединены соответственно с вторым выходом элемента -1 задержки и импульсным счетным входом второго счетчика 5, вход сброса которого соединен с выходом второго триггера 6, установочный вход которого соединен с входом сброса первого счетчика 2, который является входом 9 сброса пересчетного устройства, а выход переноса первого счетчика 2 соединен с вхоЛом сброса первого триггера 4.

Элемент памяти может быть реализован на микросхеме оперативного запоминающего устройства (ОЗУ).

Пересчетное устройство работает следующим образом.

В ячейках ОЗУ элемента 1 памяти хранят значения декад счета пересчетного устройства. Для изменения значения этих декад служит счетчик 5. Счетчик 2 формирует последовательность адресов ячеек ОЗУ. В ячейке по нулевому адресу хранят младшую Декаду Деления. Счет начинается с нулевого значения кода счетчика 2. После поступления на счетчик 2 со счетного входа 8 устройства десяти импульсов на выходе переноса счетчика 2 появляется импульс, который устанавливает в нулевое состояние триггер 4.Сигнал с выхода триггера 4 поступая на элемент ИЛИ 7, раэрйпает формирование импульса суммирования в счетчик 5, по которому осугцествляется прибавление единицы в младшую декаду (ячейку ОЗУ с нулевым адресом). При отсутствии переноса из этой декады триггер 4 устанавливается в единицу и при последовательном считывании остальных девяти ячеек содержимое не изменяется . Отсчитав очередные деЬять импульсов, счетчик 2 снова формирует импульс переноса и к нулевой ячейке ОЗУ при

бавляется еще одна единица. В случае заполнения нулевой ячейки на выходе счетчика 5 возникает импульс переноса, который не дает установиться в единицу триггеру 4, и единица прибавляется в следующую ячейку. При этом в нулевую ячейку записывается код нуля. Этот процесс продолжается до окончания поступления импульсов или до появления высокого уровня

0 на входе 9. Таким образом, в предлагаемом устройстве осуществляется начальная установка (обнуление) устройства, пересчет числа импульсов, поступающих на вход 8 устройства, и хранение в ОЗУ результатов счета.

5

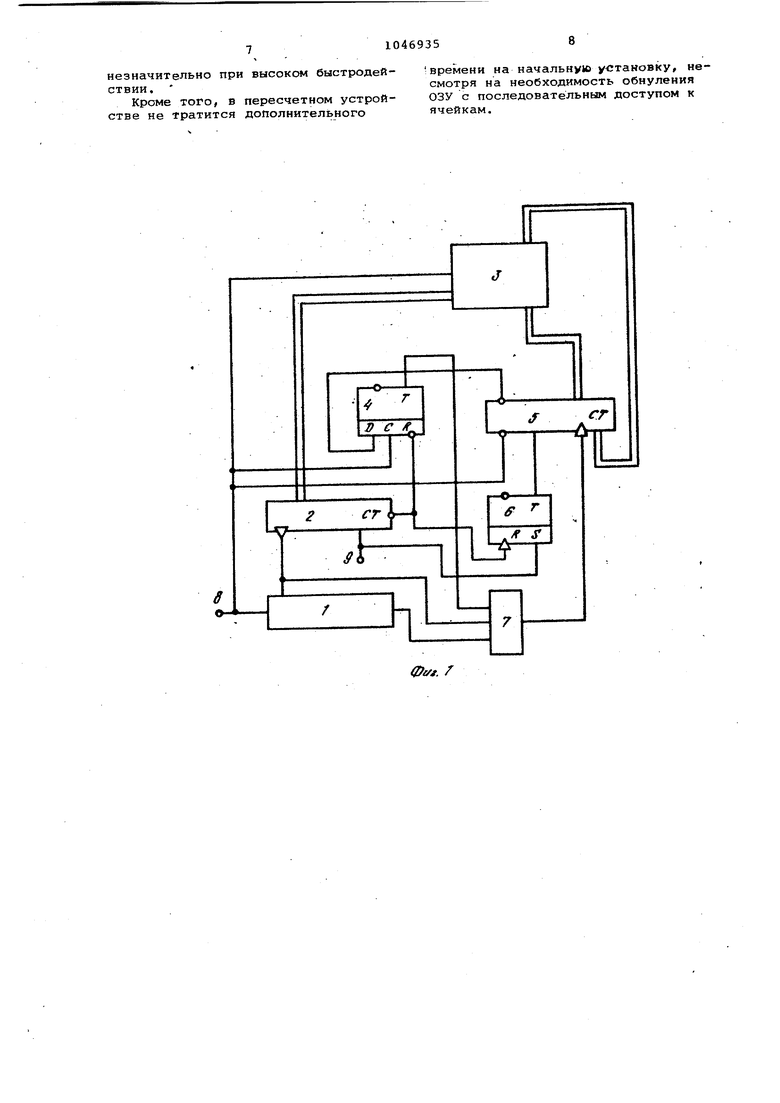

Для более подробного рассмотрения работы устройства обратимся к временным диаграммам, представленным на фиг. 2. Высокий уровень на входе начальной установки (временная диа0грамма 10) устройства обнуляет счетчик 2, блокируя его работу, а следовательно, и работу всего устройства даже при наличии импульсов на его входе. 8 (временная диаграмма 11).

5 Этот сигнал на входе. 9 устройства взводит триггер 6 в единичное состояние, . высокий уровень с выхода котого обнуляет счетчик 5, за/трещая его работу. Работа устройства начинает0ся в момент времени f с появлением фронта первого импульса на входе 8 / (после установки низкого уровня на, входе 9). При этом между появлением низкого уровня на входе 9 и фронтом

5 первого импульса на входе 8 счет- чик 2 и счетчик 5 находятся в нулевом состоянии,триггер 6 - в единичном, а триггер 4 может быть в произвольном состоянии. Передний фронт

0 первого счетного импульса, поступая в момент i на тактовый вход триггера 4, взводит его в.единичное состояние (если он стоял в нуле) или оставляет его в состоянии логической единицы, поскольку на его информа5ционнее входе в этот момент стоит высокий уровень с инверсного выхода цепи переноса счетчика 5, Высокий уровень с выхода триггера 4, поступая на вход элемента ИЛИ 7, блокиру0ет прохождение импульсов на счетный вход счетчика 5, поступающих с выходов элемента 1 задержки (фиг. 2 диаграмма 12). Кроме того, триггер 6 удерживает в нулевом состоянии счет5чик 5, не разрешая его работу при появлении низкого уровня на инверсном входе разрешения параллельного занесения этого счетчика.

Появление высокого уровня на вхо0де 8 разрешает запись в ОЗУ информации, поступающей на его информационные входы с информационных выходов счетчика5. Поскольку счетчик 2 и счетчик 5 стоят в нуле, в ячейку . ОЗУ с нулевьом адресом будут записаны

5

нули. По заднему фронту первого импульса, поступившего с первого выхода элемента 1 задержки (фиг. 2 диаграмма 12), счетчик 2 переключается ИЗ нулевого состояния в первое.. При этом триггер 4 и триггер 6 находятСЯВ состоянии логической единицы, а счетчик 5 в нулевом состоянии.

Аналогично проходит работа устройства при поступлении второго, третьего- и т.д. импульсов вплоть до десятого.. При этом, поскольку счетчик 5 по прежнему удерживается в нулевом состоянии., то с появлением каждого очередного импульса на входе 8 устройства происходит занесение нуля в ОЗУ по очередному адресу. По Десятому импульсу при наличии кода девятки и высоком уровне на инверсном счетном входе счетчика 2 (фиг. 2 диаграмма 13) на инверсном выходе цепи переноса счетчика адреса 2 появляется низкий уровень (фиг. 2 t- - t) , который,поступая на нулевой вход тригге.ра 4, устанавливает его в состояние логического нуля, разрешая тем самым прохождение-импульсов через элемент ИЛИ 7. П.оложительный фронт выхода цепи переноса счетчика переводит триггер 6 (фиг. 2 диаграмма 14) в состояние логического нуля, разрешая тем самым работу счетчика 5 (фиг. 2, -1-4 ) Таким образом., по заднему фронту десятого импульса, поступившего с первого выхода элемента 1 задержки, счетчик 2 переключается в нулевое состояние. К этому моменту времени триггер 4 (фиг. 2 диаграм ма 15) и триггер 6 уже стоят в состоянии логического нуля. Поэтому по низкому уровню сигнала на инверсном входе разрешения параллельного занесения счетчика 5 осуществляется занесение содержимого нулевой ячейки ОЗУ (содержимое нулевой ячейки в этот момент равно нулю) в счетчик 5. В следующий момент времени счетчик 5 переключается по положите.льному перепаду импульса, поступающего с выхода элемента ИЛИ 7. Этот перепад формируется при переключении триггера 4 (фиг. 2 диаграмма 16), осуществляемого по положительному перепаду следующего (в. данном случае одиннадцатого) импульса, поступающего на тактовый вход триггера 4 с входа 8 устройства. Таким образом, фронт счетного импульса будет формирован на выходе элемента ИЛИ 7 (фиг. 2 диаграмма 17) в момент времени, к которому на инверсном входе разрешения параллельного занесения счетчика 5 уже стоит высокий уровень, который препятствует работе счетчика 5 в режиме счета,По высокому уровню этого импульса с входа 8 устройства осуществляется запись содержимого счетчика 5 в ОЗУ (в данном

случае в ячейку с нулевым адресом, фиг. 2 диаграмма 18) .. Переключение счетчика 2 происходит по отрицательному перепаду одиннадцатого импульса, поступающего с первого выхода элемента 1 задержки на счетный вход счетчика 2.

Работа устройства на следующих восьми тактах- в интервале времени t происходит аналогично, за исключением того, что импульсы на счетный вход счетчика 5 не поступают, поскольку их прохождение через элемент ИЛИ 7 блокирует высокий уровень на выходе триггера 4.

При поступлении на вх.од 8 устройства двадцатого, тридцатого и,т.д. импульсов ( при коде девять в счетчике 2) происходит прибавление единиц в счетчик 5 (аналогично тому, как это было ранее рассмотрено для Десятого импульса).

При считывании иэ очередной ячейки ОЗУ кода девять и занесения его в счетчик 5 (фиг. 2 диаграмма 19 а также при наличии импульса на его счетном входе на инверсном выходе цепи переноса счетчика 5 появится низкий уровень(фиг. 2 диаграмма 20) В результате с приходом фронта очередного импульса на вход 8 устройства триггер 4 остается в состоянии логического нуля, разрешая прохождение импульса с выхода элемента ИЛИ 7 Поэтому при считывании из .ОЗУ к записи в счетчик 5 содержимого следующей ячейки (фиг. 2 t - t.., ° импульсу с выхода элемента ИЛИ 7 происходит прибавление единицы к содержимому счетчика 5, что эквивалентно переносу единицы в следующую декаду. Если в считанной ячейке ОЗУ хранился код девять , то с появлением импульса на счетном входе счетчика 5 на выходе его цепи переноса снова возникает перенос, аналогичный тому, как это уже описано выше. Таким обрс13ом, если, например, в семи ячейках ОЗУ подряд, начиная с нулевой, хранится код девять, то после занесения содержимого нулевой ячейки ОЗУ в счетчик 5 и появления импульса на выходе элемен , та ИЛИ 7 триггер 4 будет находиться в состоянии логического нуля на протяжений .последующих семи с половиной тактов сигнала на входе 8 устройства.

Таким образом, в предлагаемом устройстве осуществляется начальная установка (обнуление) устройств, в том числе ОЗУ, пересчет числа импульсов, поступающих на вход 8 и хранение результата счета.

Технико-экономическая эффективность заключается в том, что при увеличении коэффициента пересчета затраты оборудования увеличиваются

незначительно при высоком быстродействии.

Кроме того, в пересчетном устройстве не тратится дополнительного

времени на начальную установку, несмотря на необходимость обнуления ОЗУ с последовательным доступом к ячейкам.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Устройство управления | 1978 |

|

SU780007A1 |

| Многодекадное пересчетное устройство с управляемым коэффициентом пересчета | 1978 |

|

SU752814A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для измерения характеристик сверхпроводящих образцов | 1989 |

|

SU1675789A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Устройство для синхронизации воспроизведения цифровой магнитной записи | 1982 |

|

SU1048512A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1995 |

|

RU2094842C1 |

| Устройство для индикации | 1979 |

|

SU824291A1 |

ПНРЕСЧЕТНОЕ УСТРОЙСТВО, содержащее элемент задержки, первый счетчик, элемент памяти, первый триггер, второй счетчик, второй триггер и элемент ИЛИ, первый вход которого соединен с выходом первого триггера, информационный вход которого соединен с инверсным выходом переноса второго счетчика, а выход переноса первого счетчика соединен с входом сброса второго триггера, отличающееся тем, что, с целью повышения быстрюдействия, вход элемента задержки, который является входом пересчетного устройства, соел динен с тактовым входом элемента памяти, тактовым входом первого триггера и инверсным входом записи второго счетчика, информационные входы и выходы которого соединены соответственно с информационными выходами и входами элемента памяти, адресный вход которого соединен с выходом первого счетчика, инверсный импульсный счетный которого соединен с первым выходом элемента задержки и вторым входом элемента ИЛИ, третий вход и выход которого соедис в нены соответственно с вторьм выхс/дом элемента задержки и импульсным счетным входом второго счетчика, вход сброса которого соединен с выходом второго триггера, установочный вход которого соединен с входом сброса первого счетчика, который является входом сброса пересчетного устройства, а выход переноса первого счетчика соединен с входом сбро са первого триггера. 4 Л СО СО СП

8

О-г---

ff СГ

S С f 0-1Л

z

I

фг/. /

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО СРАВНЕНИЯ ПОСЛЕДОВАТЕЛЬНЫХ КОДОВ | 0 |

|

SU347925A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-10-07—Публикация

1982-01-25—Подача