1

Известны устройства для экстраполяции функций, заданных цифровым кодом, содержащие последовательно соединенные первую и вторую ячейки памяти, мелсду входами которых включена линия задержки, и масштабные резисторы.

Недостатком известных устройств является низкая точность экстраполяции.

Предложенное устройство отличается тем, что оно содержит третью ячейку памяти, входы которой непосредственно и через дополнительную линию задержки соединены со входами второй ячейки памяти, и цифро-аналого15ЫЙ блок вычисления полиномов, один из входов которого соединен со входной клеммой, два других входа подключены через масштабиые резисторы ко входам ячеек памяти, а выход присоединен к выходной клемме устройства и через масштабный резистор подключен к выходу первой ячейки памяти.

Это позволяет существенно повысить точиость экстраполяции.

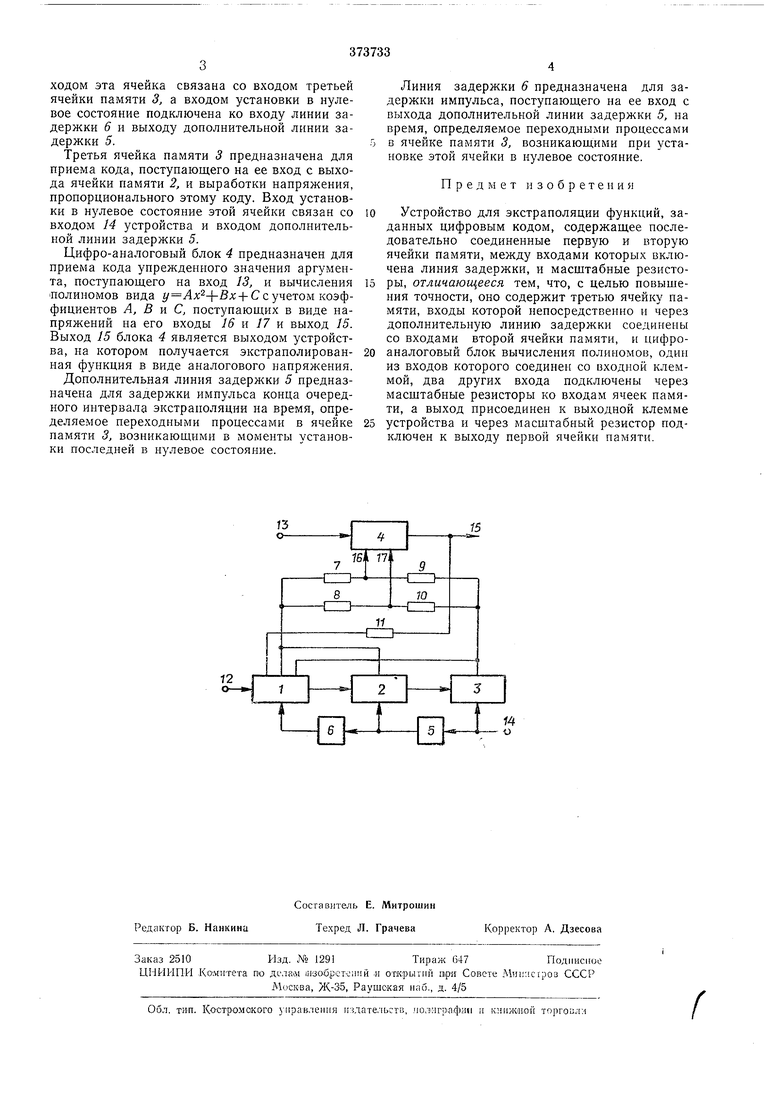

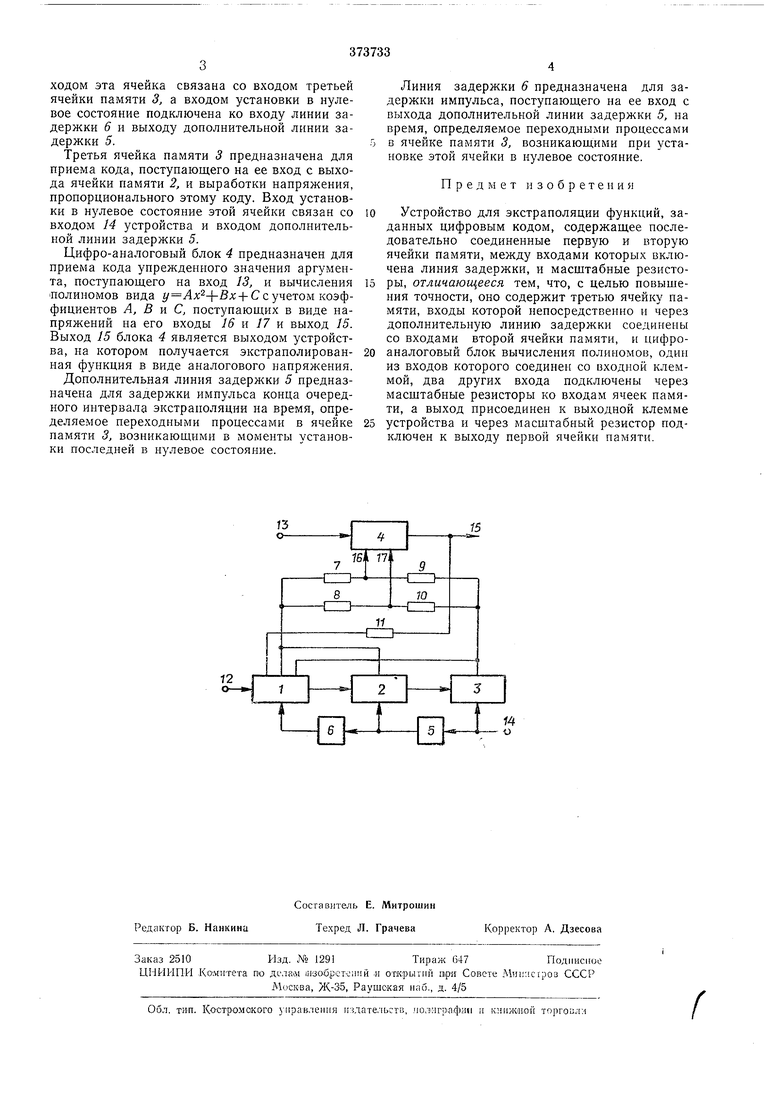

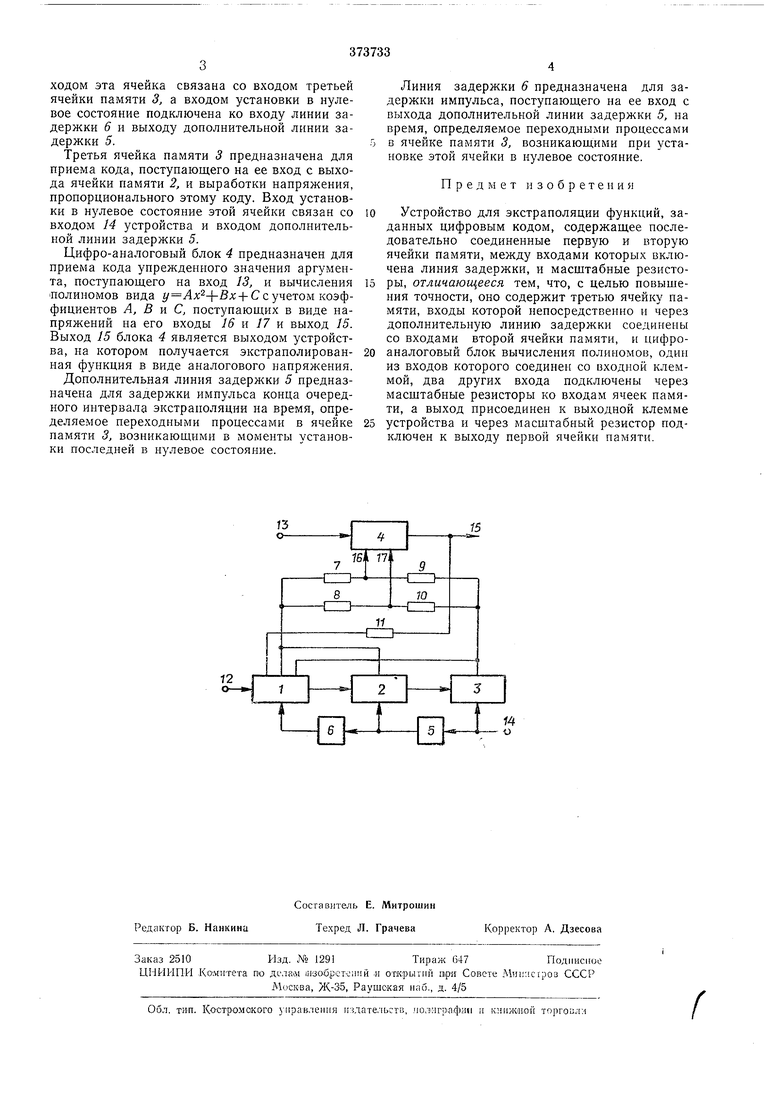

На чертеже представлена блок-схема устройства.

Устройство содержит ячейки памяти 1, 2 и 3, цифро-аналоговый блок 4 вычисления полиномов вида .- -Вх-{-С, дополнительную 5 и основную 6 линию задержки, масштабные резисторы 7-11. Цифрами 12-15 соответственно обозначены входы: кода ординат экстраполируемой функции, кода упрежденного значения аргумента, импульса конца очередного интервала экстраполяции и выход экстраполированной функции. Цифрами 16 и 17 обозначены

входы коэффициентов /1 и S блока 4.

Ячейка памяти / предназначена для приема кода ординат экстраполируемой функции, поступающих на вход 12 устройства, выработки прямого и инверсного (противофазного) напряжений, пропорциональных этому коду, и передачи в ячейку памяти 2 кода предыдущей ординаты экстраполируемой функции. Прямой выход ячейки памяти / связан с инверсным выходом ячейки памяти 2 и через масштабные

резисторы 7 и 8 - со входами 16 и 17 коэффициентов А и В цифро-аналогового блока 4 вычисления полиномов. Второй прямой выход ячейки памяти / соединен через масштабный резистор 11 с выходом 15, а инверсный выход

подключен к прямому выходу ячейки памяти 3 и через масштабные резисторы 9 и 10 - ко входам 16 и 17 блока 4. Цифровой выход ячейки памяти / связан со входом ячейки памяти 2, а вход установки в нулевое состояние иодключей к выходу линии задержки 6.

Ячейка памяти 2 предназначена для приема кода, поступающего на ее вход с выхода ячейки /, и выработки инверсного напряжения, пропорционального этому коду. Цифровым выходом эта ячейка связана со входом третьей ячейки памяти 3, а входом установки в нулевое состояние подключена ко входу линии задержки 6 и выходу дополнительной линии задержки 5.

Третья ячейка памяти 3 предназначена для приема кода, поступающего на ее вход с выхода ячейки памяти 2, и выработки напряжения, пропорционального этому коду. Вход установки в нулевое состояние этой ячейки связан со входом 14 устройства и входом дополнительной линии задержки 5.

Цифро-аналоговый блок 4 предназначен для приема кода упрежденного значения аргумента, поступающего на вход 13, и вычисления ПОЛИНОМОВ вида г/ Лл:2-|-Вх +С с учетом коэффициентов А, В и С, поступающих в виде напряжений на его входы 16 и 17 и выход 15. Выход 15 блока 4 является выходом устройства, на котором получается экстраполированная функция в виде аналогового напряжения.

Дополнительная линия задержки 5 предназначена для задержки импульса конца очередного интервала экстраполяции на время, определяемое переходными процессами в ячейке памяти 3, возникающими в моменты установки последней в нулевое состояние.

Линия задержки 6 предназначена для задержки импульса, поступающего на ее вход с выхода дополнительной линии задержки 5, на время, определяемое переходными процессами в ячейке памяти 3, возникающими при установке этой ячейки в нулевое состояние.

Предмет изобретения

Устройство для экстраполяции функций, заданных цифровым кодом, содержащее последовательно соединенные первую и вторую ячейки памяти, между входами которых включена линия задержки, и масштабные резисторы, отличающееся тем, что, с целью повышения точности, оно содержит третью ячейку памяти, входы которой непосредственно и через дополнительную линию задержки соединены со входами второй ячейки памяти, и цифроаналоговый блок вычисления полиномов, один из входов которого соединен со входной клеммой, два других входа подключены через масштабные резисторы ко входам ячеек памяти, а выход присоединен к выходной клемме

устройства и через масштабный резистор подключен к выходу первой ячейки памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| СТУПЕНЧАТО-ЛИНЕЙНЫЙ ЭКСТРАНОЛЯТОР | 1973 |

|

SU370611A1 |

| Ступенчато-линейный экстраполятор | 1976 |

|

SU591873A1 |

| Ступенчато-линейный экстраполятор | 1980 |

|

SU942059A1 |

| Экстраполятор | 1977 |

|

SU696493A1 |

| Ступенчато-линейный экстраполятор второго порядка | 1977 |

|

SU705472A1 |

| УСТРОЙСТВО для КУСОЧНО-КВАДРАТИЧНОЙ АППРОКСИМАЦИИ ФУНКЦИЙ | 1973 |

|

SU374622A1 |

| ВПТБ | 1973 |

|

SU397941A1 |

| УСТРОЙСТВО ДЛЯ ИНТЕРПОЛЯЦИИ ФУНКЦИЙ | 1972 |

|

SU432546A1 |

| Экстраполятор | 1982 |

|

SU1042037A1 |

| Линейный экстраполятор | 1977 |

|

SU691882A1 |

Авторы

Даты

1973-01-01—Публикация