1

Устройство для иитерполяции функций относится к области автоматнш и вычислительной те.. Оно может найти нримеиение для интерноляции произвольиы.х сЬункщиХ заданных в узлах значениями ординат и величинами нроизводных интериолируемой ф нкцни. Результаты интерполяции иредставляются ,в аналоговом виде.

Известен иитериолятор цифро-аналогового типа, реализующий линейную иитериоляцию функций, задавае.мых дискретньпги зиачения.мн ординат Ь{ и первой производной а, в узлах интер.поляции.

Oii содержит цифро-аналоговый блок вычисления полино.мов, первый вход которого соедннен с тгервы.м входом устройства, три цифро-аналоговых преобразователя, выход первого из которых соеди:нен через масштабный резистор с выходо.м устройства и первнлм выходом цифро-а.налогового блока вычисления полиномов; первый вход соедииеп со вторьгм входо.м устройства, а второй соединен со вторы.м выходом цнфро-аналогового блока, первым входо.м третьего цифро-аналогового преобразователя и через блок задержки - с первым входом .второго циф ро-аналогового преобразователя, второй вход которого соединен с третьи.м входо.м устройства.

Существенный недостаток этого интерполятора - сложность конструкцин ; низкая

точность воспроизведения и;1териолируемой фу,НКции, что связано с использова1 ием метода линеЙ1 ой н терполяции.

С целью уирощения устройства лсрвый выход второго и; фро-пиалогового преобразс ателя соед:рне:1 со вторым входом цифро-аналогового блока, второй выход - с выходом третьего цнфро-аналогового нреооразсвате.1я и третьи-м входом н.нфро-аналогового блока и выход - со вторы м входом третьего цифро-а 1алогозого иреоб:раловатсля.

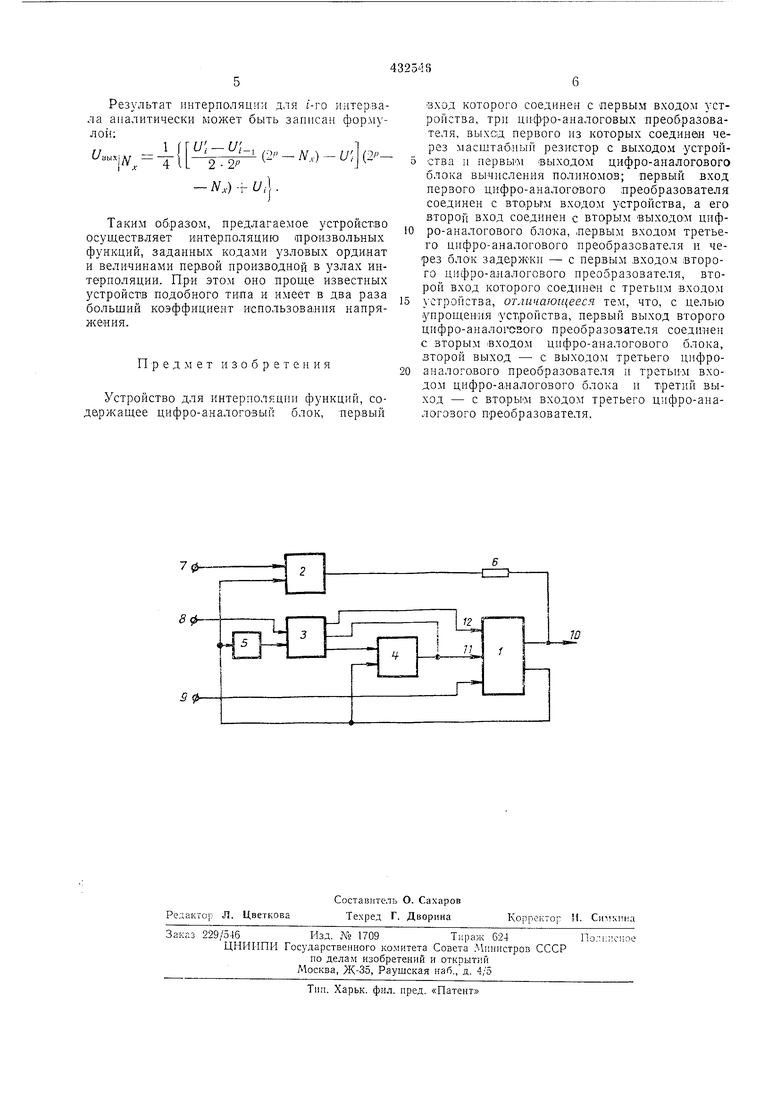

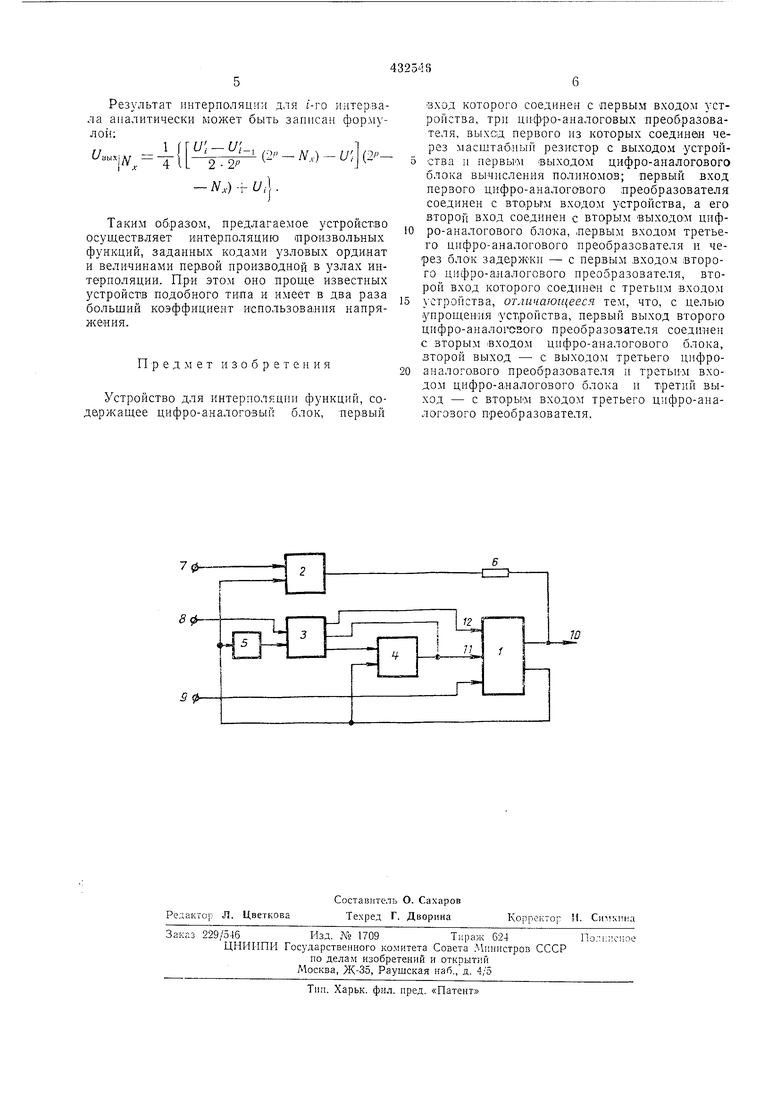

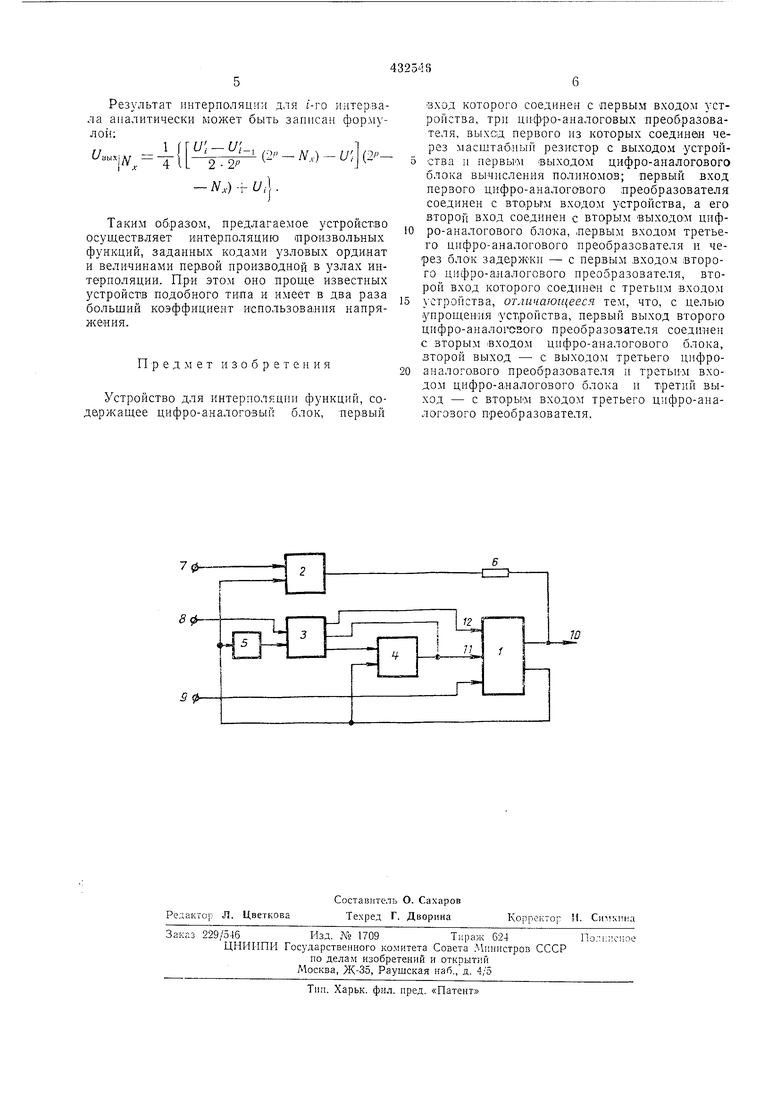

На чертеже представлена блок-схема предлагае.мо1о устройства для интерполяции ф нкций, состоящая л,- :1пфро-аналого53ого блока / вычисления полино юв вида /{.)Ах-+Вх. ци(рр()-аналого ых иреобразоватслсй 2--f, блока задержки 5 и масштабного резистора 5. Цифрами 7, 8, 9, 10 обозначены соответственно: вход кода узловых ордшпгг нитерполируе.мой ф нкции, вход кода величин иро зводных интерполи-руемой функции в узлах интерполяции, вход кода :Уд. аргумента Ли пыход устройства, на котором получается рез льтат iniтериоляци; в виде аналогово10 напря/ксн1 я. Цифрами 1} и 12 обозиачснг-: соответственно входы ианряжен;и 1. пропорциональных коэффициентам .4 и В иитериоляцномнсго полиHOiia.

Ц фро-а; ало;-азый блс

пред-лазиачеи

для поиема тек -;цего значения аргумента, задаваемого последовательностью ИМпульсов унитарного кода, который поступает на вход Я для вычисления полиномов вида f(x) Ах + Вх с учетом коэффициентов А и В, постунающих па его входы // и 12 в виде напряже(ПИЙ, а также для выработки си1гпала конца очередного интервала интерполяции и передачи этого сигнала на Зстано вочный вход цифро-аналогового преобразователя 4 и вход блока задержки 5.

Вход // коэффициента Л связан с инверсным выходом цифро-аналотового нреобразователя 4 и выходом цнфро-аналогсвого преобразователя 3. Вход 12 коэффициента В связа.п с нпверспым выходом цифро-аналогового преобразователя 3. Выход 10 блока / соединен через масштабный резистор 6 с выходОМ диф-ро-аналогового преобразователя 2 и выходом W устройства. Выход сигнала конца очередного интервала интерполяции связан с установочными входами цифро-апалоговых преобразователей 4 и 2 и через блок задержки 5 - с установочным входом цифро-аналогового преобразователя 3. Цифровой вход блока / подключен ко входу 9.

Цифро-аналсгозый преобразователь 2 предназначен приема кода очередной узл{;вой ординаты ннтернолИруемой функции и преобразования его в напряжение, пропорциональное Коэффициенту С.

Вход цифро-аналогового преобразователя 2 подключеи ко входу 7.

Цифро-аналоговый преобразователь, предназначен для приема кода очередного узлового значения первой производной интерполнруемой функции преобразования этого кода в пропорциональные ирямое и инверсное напряжения .па аналоговых выходах, а также для передачи этого кода в цифро-аналоговый преобразователь 4 в моменты поступления импульсов с выхода блока задержки 5.

Вхо1Д цифро-аналогового преобразователя соединен с входом 8 устройства, а цифровой выход связан с соответствующим входо м цифро-аналогового преобразователя 4.

Цифро-аналоговый преобразователь 4 предназначен для приема кода, поступающего с выхода ци1фро-аналогового преобр-азозателя 3, и преобразования его в напряжение.

Блок задержки 5 предназначен для задержки сигнала конца очередного интервала интерполяции на время, определяемое переходпыми процессами в цифро-аналоговом преобразователе 4 при установке последнего в нулевое состояние.

Внутренние сопротивления цифро-аналоговых преобразователей 2-4 и блока 1 приняты равными друг другу.

Устройство работает следующ:;м образом.

В исходном состоянии в вычитающем счетчике цифро-аналогового блока / установлено максималыюе число /У,„ 2 - 1, а в регистрах цифро-аналоговых .преобразователей 2, 3

и 4 соответственно установлены код 1-й ордииаты интерполируемой функции и коды величнн производных yi и yi-iВ режиме холостого хода (при отключениых аиалочовых выходах цифро-аналоговых преобразователей 2-4) на выходе цифро-аналогового преобразователя 2 имеется напряжение Ui, на обонх выходах цифро-аналогового преобразователя 3 - напряжения Ul, а

на инверсном выходе цифро-аналогового иреобразователя 4 - инверсное напряжение (-Ui-i), соответствующие выщеуказанным кодам.

В рабочем режиме от воздействия выщеуказанных напряжений на входе // блока / имеется напряжение:

,, fy.,---2

на входе 12 - напряжение ,

а на выходе 10 устройства (с }четом величины масштабного резистора 6 имеем;

U:-.

и.

iN,n

4

:По мере заполнения очетчика цифро-аналогового блока 1 импульсами текущего значения аргумента число в нем, равное (Лм,-.х), уменьщается н, наконец, при N,,n становится равиым нулю. При этом напряжение на выходе 10 изменяется по ступенЧато-параболическому зако1гу до величииы:

// // 1

L BLIXIO о.

где Д Увыхл - уровень квантования блока /. С поступлением на вход 9 следующего импульса текущего значения аргумента рассматтриваемый интервал интерполяции заканчивается. Сигналом конца интервала, который вырабатывается при этом в блоке 1, устанавливаются в пулевое состояние цифро-аналоговые преобразователи 2 и 4, а через некоторое время, определяемое параметрами блока за;1,ержки 5, в пулевое состояние устанавливается цифро-аналоговый преобразователь 3. Код производной ui интерполируемой функции в

это время передается в регистр цифро-аналогового преобразователя 3. Затем на входы 7 и 8 устройства подаются коды очередной ()-й узловой ординаты и производной г,//-.,.

По окончании переходных процессов и по мере иостушлепия очередных импульсов текущего значения аргумеита рассматриваемым устройством производится интерполяция па интервале, ограниченном /-и и (-г1)-й узловыми ординатами. Результат интерполяции для t-ro интерзала аналитически может быть заннсан формулой: 4-((.)(4 IL 2-2 .-) -i- U, . Таким образом, предлагаемое устройство осуществляет интерполяцию произвольных функций, заданных кодами узловых ординат и величинами первой производной в узлах интерполяции. При этом оно проще известных устройств подобного типа и имеет в два раза больший коэффициент использования напрял е«ия. Предмет изобретения Устройство для интерполяции функций, содержащее цифро-аналоговый блок, первый вход которого соединен с первым входом устройства, три цифро-аналоговых преобразователя, выхса первого из которых соединен через масщтабный резистор с выходом устройства и первым выходом цифро-аналогового блока вычисления полиномов; первый вход первого цифро-аналогового преобразователя соединен с вторым входом устройства, а его второй вход соединен с вторым выходом цифро-аналогового блока, первым входом третьего цифро-аналогового преобразователя и через блок задержки - с первым входом второго цифро-аналогового преобразователя, второй вход которого соединен с третьим входом -стройства, отличающееся тем, что, с целью упрощения устройства, первый выход второго цифро-аналогсзого преобразователя соединен с вторым входом цифро-аналогового блока, второй выход - с выходом третьего цифроаналогового преобразователя и третьи м входом цифро-аналогового блока и третий выход - с вторЫМ входом третьего цифро-аналогового преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВПТБ | 1973 |

|

SU397941A1 |

| УСТРОЙСТВО для КУСОЧНО-КВАДРАТИЧНОЙ АППРОКСИМАЦИИ ФУНКЦИЙiS^,fi-\?-t "JP'ltpT^^ФУ-ЗД и ;i,'';^r «^'.) | 1973 |

|

SU408329A1 |

| УСТРОЙСТВО для КУСОЧНО-КВАДРАТИЧНОЙ АППРОКСИМАЦИИ ФУНКЦИЙ | 1973 |

|

SU374622A1 |

| Нелинейный интерполятор | 1985 |

|

SU1267446A1 |

| Устройство для интерполяции знакопеременных функций | 1974 |

|

SU481052A1 |

| ЙСЕСОЮЗН'-^-'V г •' •- ^' ^1' • •• • | 1973 |

|

SU373733A1 |

| Функциональный преобразователь | 1982 |

|

SU1049929A1 |

| Функциональный преобразователь | 1986 |

|

SU1403078A1 |

| Ступенчато-линейный экстраполятор | 1976 |

|

SU627489A1 |

| Нелинейный интерполятор | 1984 |

|

SU1265809A1 |

Даты

1974-06-15—Публикация

1972-07-13—Подача