1

Изобретение относится к области техники связи.

Известна соединительная сеть с импульсным временным разделением каналов, содержащая управляющее запоминающее устройство, входной, промежуточный и выходной коммутаторы, каждый из которых состоит из входных и выходных регистров. Такая сеть имеет недостаточно больщую емкость.

В целях увеличения емкости предлагаемая сеть выполнена в виде двух идентичных сетей, в которых промежуточный коммутатор содержит дополнительные входные регистры. Последние соединены с дополнительным буферным запоминающим блоком, который связан с управляющим запоминающим устройством, имеющий дополнительный сдвоенный элемент на каждое слово, и с выходными регистрами промежуточного коммутатора. При этом каждый выходной регистр входного коммутатора одной сети соединен с соответствующим дополнительным выходным регистром такого же промежуточного коммутатора другой сети.

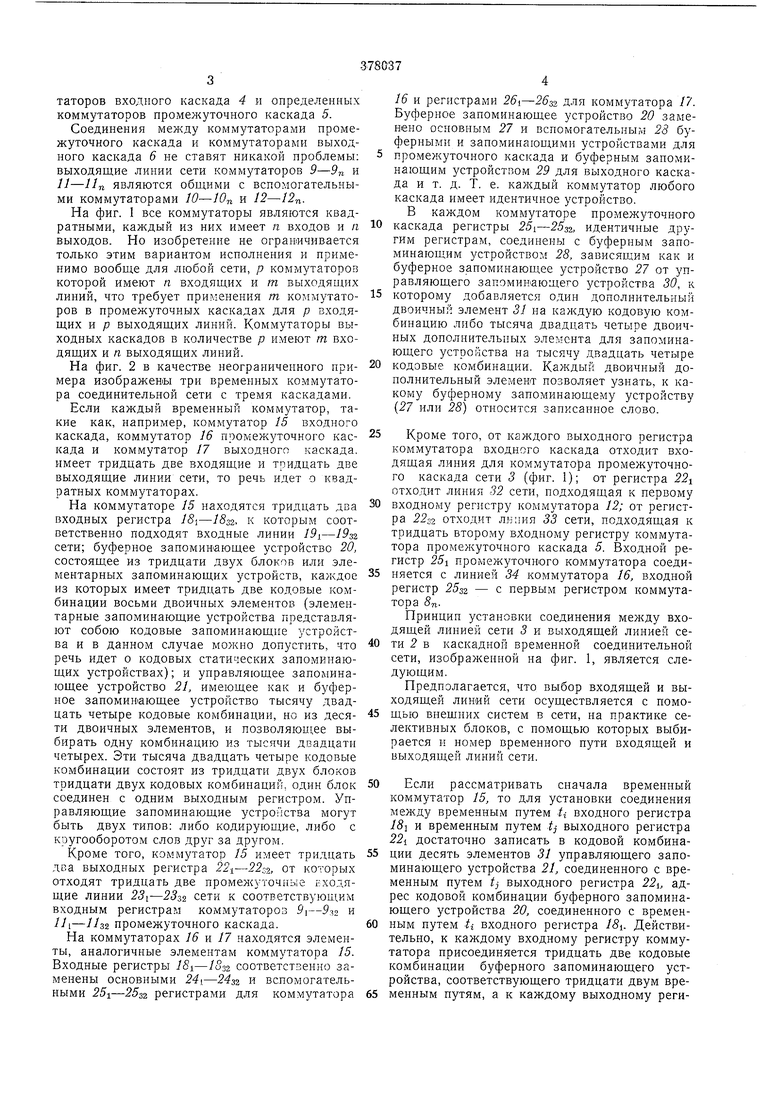

На фиг. 1 изображена схема временной соединительной сети с тремя каскадами; на фиг. 2-временная соединительная сеть, обеспечивающая появление основных составляющих временных коммутаторов.

Трехкаскадная соединительная сеть}на2п линий состоит из двух сетей 2 и 3 с п линиями каждая. Каждая из сетей 2 и 5 состоит из входного 4, промел уточного 5 и выходного 6 каскадов.

Входной каскад сети 2 имеет п коммутаторов 7-7„; входной каскад сети 3 имеет п коммутаторов 8-8пПромежуточный каскад сети 2 имеет п основных 9-9п и п вспомогательных 10-Юп коммутаторов. Промежуточный каскад сети 3 содержит п основных 11-Ип и п вспомогательных 12-12п коммутаторов.

Выходной каскад 6 сети 2 содержит п коммутаторов 13-13п, выходной каскад сети 3 содержит п коммутаторов 14-14пВыходы коммутаторов 7 входного каскада 4 сети 2 соединяются с входами основных коммутаторов 9-9п промежуточного каскада 5 указанной сети и с входами вспомогательных коммутаторов 12-/2„ промежуточного каскада сети 3. Выходы коммутаторов 8-8п входного каскада сети 3 соединяются с входа п1 коммутаторов 11-//„ указанной сети, а также с входами вспомогательных коммутаторов 10-Юп промежуточного каскада сети 2.

В общем случае для соединения коммутаторов 7-7п и 11-Пп, 8-8п и П-Пп, 5- 8п и 10-10п следует иметь в виду каждый раз соединительную сеть, образованную из коммутаторов входного каскада 4 и определенных коммутаторов промежуточного каскада 5.

Соединения между коммутаторами промежуточного каскада и коммутаторами выходного каскада 6 не ставят никакой проблемы: выходящие линии сети коммутаторов 9-9„ и //-11п являются общими с вспомогательными коммутаторами 10-10п и 12-12п.

На фиг. I все коммутаторы являются квадратными, каждый из них имеет п входов и я выходов. Но изобретение не ограничивается только этим вариантом исполнения и применимо вообще для любой сети, р коммутаторов которой имеют п входящих и т выходяндах лииий, что требует применения т коммутаторов в промежуточных каскадах для р входящих и р выходящих линий. Коммутаторы выходных каскадов в количестве р имеют т входящих и п выходящих лииий.

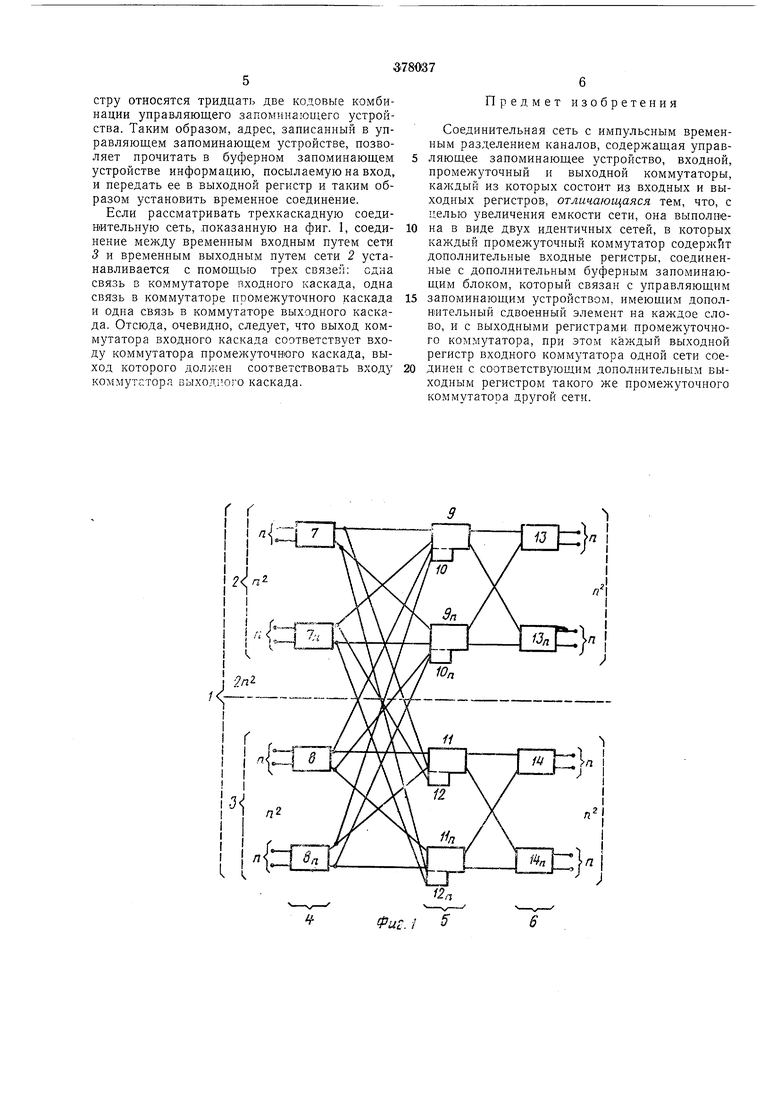

На фиг. 2 в качестве неограниченного примера изображены три временных коммутатора соединительной сети с тремя каскадами.

Если каждый временный коммутатор, такие как, например, коммутатор 15 входного каскада, коммутатор 16 промежуточного каскада и коммутатор 17 выходного каскада, имеет тридцать две входящие и тридцать две выходящие линии сети, то речь идет о квадратных коммутаторах.

На коммутаторе 15 находятся тридцать два входных регистра .§32, к которым соответственно подходят входные линии 19 -/9з2 сети; буферное запоминающее устройство 20, состоящее из тридцати двух блоков или элементарных запоминающих устройств, каждое из которых имеет тридцать две кодовые комбинации восьми двоичных элементов (элементарные запоминающие устройства представляют собою кодовые заноминающие устройства и в данном случае можно допустить, что речь идет о кодовых статических запоминающих устройствах); и управляющее запоминающее устройство 21, имеющее как и буферное запоминающее устройство тысячу двадцать четыре кодовые комбинации, но из десяти двоичных элементов, и позволяющее выбирать одну комбинацию из тысячи двадцати четырех. Эти тысяча двадцать четыре кодовые комбинации состоят из тридцати двух блоков тридцати двух кодовых комбинаций, один блок соединен с одним выходным регистром. Управляющие запоминающие устройства могут быть двух типов: либо кодирующие, либо с кругооборотом слов друг за другом.

Кроме того, коммутатор 15 имеет тридцать два выходных регистра 22i-.2.232, от которых отходят тридцать две промелсуточные входящие линии 23i-25з2 сети к соответствующим входным регистрам коммутаторов и 11{-//32 промежуточного каскада.

На коммутаторах 16 и 17 находятся элементы, аналогичные элементам коммутатора 15. Входные регистры 18 -/с5з2 соответственно заменены основными и вспомогательными 25i-.25з2 регистрами для коммутатора

16 и регистрами для коммутатора 17. Буферное запоминающее устройство 20 заменено основным 27 и вспомогательным 28 буферными и запомииающими устройствами для промежуточного каскада и буферным запоминающим устройством 29 для выходного каскада и т. д. Т. е. каждый коммутатор любого каскада имеет идентичное устройство. В каждом коммутаторе промежуточного

каскада регистры 25i-25з2, идентичные другим регистрам, соединены с буферным запоминающим устройством 28, зависящим как и буферное запоминающее устройство 27 от управляющего запоминающего устройства 30, к

которому добавляется один дополнительный двоичный элемент 31 на каждую кодовую комбинацию либо тысяча двадцать четыре двоичных дополнительных элемента для запоминающего устройства на тысячу двадцать четыре

кодовые комбинации. Каждый двоичный донолнительный элемент позволяет узиать, к какому буферному запоминающему устройству (27 или 28} относится записанное слово.

Кроме того, от каждого выходного регистра коммутатора входного каскада отходит входящая линия для коммутатора промежуточного каскада сети 3 (фиг. 1); от регистра 22 отходит линия 32 сети, подходящая к первому

входному регистру коммутатора 12; от регистра отходит лклия 33 сети, подходящая к тридцать второму входному регистру коммутатора промежуточного каскада 5. Входной регистр 25i промежуточного коммутатора соединяется с линией 34 коммутатора 16, входной регистр 25з2 - с первым регистром коммутатора 8п.

Принцип установки соединения между входящей лииией сети 5 и выходящей линией сети 2 в каскадной временной соединительной сети, изображенной на фиг. 1, является следующим.

Предполагается, что выбор входящей и выходящей линий сети осуществляется с помощью внещних систем в сети, иа практике селективных блоков, с помощью которых выбирается и номер временного пути входящей и выходящей линий сети.

Если рассматривать сначала временный коммутатор 15, то для установки соединения временным путем ti входного регистра 18i и временным нутем tj выходного регистра 22i достаточно записать в кодовой комбинации десять элементов 31 управляющего запоминающего устройства 21, соединенного с временным путем tj выходного регистра 22i, адрес кодовой комбинации буферного заноминающего устройства 20, соединенного с временным путем ti входного регистра 18i. Действительно, к каждому входному регистру коммутатора присоединяется тридцать две кодовые комбинации буферного заноминающего устройства, соответствующего тридцати двум временным путям, а к каждому выходному регистру относятся тридцать две кодовые комбинации уцравляющего запоминающего устройства. Таким образом, адрес, записанный в унравляющем запоминающем устройстве, позволяет прочитать в буферном запоминающем устройстве информацию, посылаемую на вход, и передать ее в выходной регистр и таким образом установить временное соединение.

Если рассматривать трехкаскадную соединительную сеть, .показанную на фиг. 1, соединение между временным входным путем сети 3 и временным выходным путем сети 2 устанавливается с помощью трех связей: одна связь в коммутаторе входного каскада, одна связь в коммутаторе промежуточного каскада и одна связь в коммутаторе выходного каскада. Отсюда, очевидно, следует, что выход коммутатора входного каскада соответствует входу коммутатора промежуточного каскада, выход которого должен соответствовать входу коммутатора выходного каскада.

6

Предмет изобретения

Соединительная сеть с импульсным временным разделением каналов, содержащая управляющее запоминающее устройство, входной, промежуточный и выходной коммутаторы, каждый из которых состоит из входных и выходных регистров, отличающаяся тем, что, с целью увеличения емкости сети, она выполнена в виде двух идентичных сетей, в которых каждый промежуточный коммутатор содержит дополнительные входные регистры, соединенные с дополнительным буферным запоминающим блоком, который связан с управляющим

запоминающим устройством, имеющим дополнительный сдвоенный элемент на каждое слово, и с выходными регистрами промежуточного коммутатора, при этом каждый выходной регистр входного коммутатора одной сети соединен с соответствующим дополнительным выходным регистром такого же промежуточного коммутатора другой сети.

| название | год | авторы | номер документа |

|---|---|---|---|

| Неблокирующая система связи,например телефонной | 1970 |

|

SU510179A3 |

| УСТРОЙСТВО ДЛЯ ПРЕДОСТАВЛЕНИЯ УСЛУГ ИНТЕЛЛЕКТУАЛЬНОЙ СЕТИ | 1999 |

|

RU2156037C1 |

| Устройство цифровой коммутации | 1982 |

|

SU1308209A3 |

| Система управления печатающим устройством | 1969 |

|

SU473345A3 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ВИДЕОСИГНАЛА ИЗОБРАЖЕНИЙ | 1995 |

|

RU2090011C1 |

| УСТАНОВЛЕНИЕ ТРАКТОВ ВЫЗОВОВ СЕТЕЙ СВЯЗИ В ШИРОКОПОЛОСНЫХ СЕТЯХ СВЯЗИ | 1993 |

|

RU2117403C1 |

| СИНХРОННО-АСИНХРОННЫЙ И АСИНХРОННО-СИНХРОННЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2097929C1 |

| КОСМИЧЕСКИЙ РАДИОЛОКАТОР С СИНТЕЗИРОВАННОЙ АПЕРТУРОЙ, ФОРМИРУЮЩИЙ ИЗОБРАЖЕНИЕ В РЕАЛЬНОМ ВРЕМЕНИ | 1999 |

|

RU2158008C1 |

| Буферное запоминающее устройство с произвольной выборкой двумерного фрагмента | 1986 |

|

SU1444784A1 |

1в

J2 3

tpuz.2

Даты

1973-01-01—Публикация