1

Изобретение Относится к области цифровой вычислительной техники и может быть использовано при построении запоминающих устройств (ЗУ).

Известны запоминающие устройства, содержащие накопитель, соединенный с блоком управления по адресным и разрядным цепям, блоками считывания и блоком синхронизации, связанным с блоком унравлення по адресным и разрядным цепям.

Однако такие устройства имеют небольшую надежность работы при изменении температуры впешней среды и при изменении значений напряжений и внутренних параметров ЗУ.

В нредлагаемом запоминающем устройстве на ферритовых сердечниках в блок управления но адресным и разрядным цепям введен дополнительный адресно-разрядный канал, соединеиный с адресными и разрядными цепями дополнительного разряда наконителя, цень считывания которого связана с усилителем считывания, соединенным выходом со входами Л амплитудных дискриминаторов с различными уровнями порогов срабатывания, выходы которых подключены к единичным входам Л триггеров, нулевые входы которых и блокировочные входы амплитудных дискриминаторов объединены и соединены с блоком синхронизации, причем едипичиые выходы триггеров связаны с цифроаналоговым преоёраЗователеМ, выход которого Подключен t управляющим входам блоков считывания.

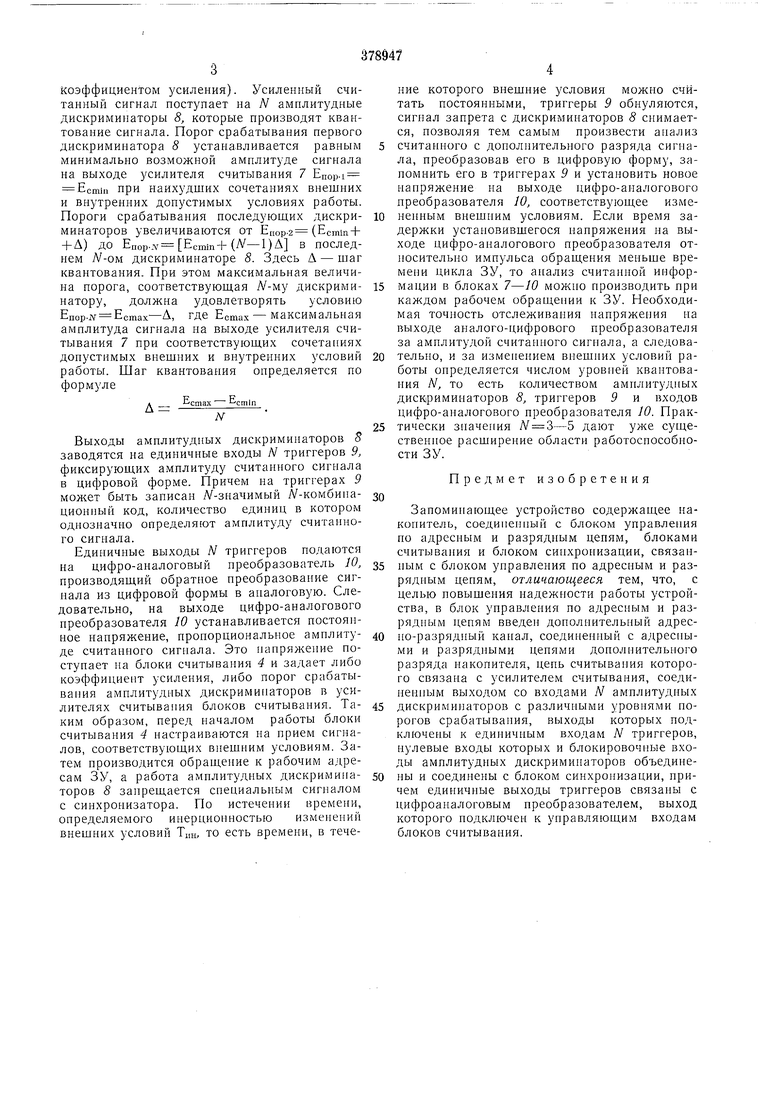

На чертеже изображена блок-схема предлагаемого ЗУ.

Оно состоит из накопителя /, сипхронизатора 2, блока 3 управления по адресным и разрядным цепям, блоков считывания 4, дополнительного разряда 5 в накопителе J, одного дополпительного адресно-разрядного канала

в блоке 3 управления по адресным и разрядным цепям, усилителя считьсвания 7 с дополнительного разряда 5, N амплитудных дискриминаторов 8, N триггеров 9, цифроаналогового преобразователя 10.

На вход 11 синхронизатора поступает импульс обращения, а на вход 12 - сигнал режима работы (занись или считывание), на входы 13 и М блока управления ностунают соответственно сигналы выбора адреса и ииформация, а с выходов 15 считанная, информация поступает на выход ЗУ. Схема работает следующим образом. Перед началом работы с синхронизатора 2 подается обращепие к дополнительному адресно-разрядному каналу 6 блока управления по адресным и разрядным ценям. Сигнал, считанный при этом с дополнительного адреса в дополнительном разряде 5, в котором постоянно записывается единица, подается на

вход усилителя считывания 7 (с постоянным Коэффициентом усиления). Усиленный считанный сигнал поступает на N амплитудные дискриминаторы 8, которые производят квантование сигнала. Порог срабатывания первого дискриминатора 8 устанавливается равным минимально возможной амплитуде сигнала на выходе усилителя считывания 7 Enop-i Ecmin при наихудших сочетаниях внешних и внутренних допустимых условиях работы. Пороги срабатывания последующих дискриминаторов увеличиваются от Егюр-2 (Ecmin + + Д) до Enop..Y Ecmm+()А В последнем дискриминаторе 5. Здесь Д - шаг квантования. При этом максимальная величина порога, соответствуюш,ая дискриминатору, должна удовлетворять условию Enop-Jv Ecmax-А, где Естах - максимальная амплитуда сигнала па выходе усилителя считывания 7 при соответствуюш,их сочетаниях донустимых внешних и внутренних условий работы. Шаг квантования определяется по формуле РF стах cmin Выходы амплитудных дискриминаторов S заводятся на единичные входы N триггеров 9, фиксируюш,их амплитуду считанного сигнала в цифровой форме. Причем на триггерах 9 может быть занисан //-значимый Л -комбинационный код, количество единиц в котором однозначно определяют амплитуду считанного сигнала. Единичные выходы Л триггеров подаются на цифро-аналоговый преобразователь 10, производяший обратное преобразование сигнала из цифровой формы в апалоговую. Следовательно, на выходе цифро-аналогового преобразователя 10 устанавливается постоянное напряжение, пропорциональное амплитуде считанного сигнала. Это напряжение поступает на блоки считывания 4 и задает либо коэффициент усиления, либо порог срабатывания амплитудных дискриминаторов в усилителях считывания блоков считывания. ТаКИМ образом, перед началом работы блоки считывания 4 настраиваются на прием сигналов, соответствуюш,их внешним условиям. Затем производится обран;ение к рабочим адресам ЗУ, а работа амнлитудных дискриминаторов 8 запрешается специальным сигналом с синхронизатора. По истечении времени, определяемого инерционностью изменений внешних условий Тин, то есть времени, в течение которого внешние условия можно считать постоянными, триггеры 9 обнуляются, сигнал запрета с дискриминаторов 8 снимается, позволяя тем самым произвести анализ считанного с донолнительного разряда сигнала, преобразовав его в цифровую форму, запомнить его в триггерах 9 и установить новое нанряжение на выходе цифро-аналогового преобразователя 10, соответствуюш.ее измененным внешним условиям. Если время задержки установившегося нанряжения на выходе цифро-аналогового преобразователя относительно импульса обращения меньше времени цикла ЗУ, то анализ считанной информации в блоках 7-10 можно производить при каждом рабочем обращении к ЗУ. Необходимая точность отслеживания напряжения на выходе аналого-цифрового преобразователя за амплитудой считапного сигнала, а следовательно, и за изменением внешних условий работы онределяется числом уровней квантования N, то есть количеством амнлитудных дискриминаторов 8, триггеров 9 и входов цифро-аналогового преобразователя 10. Практически значения /V 3-5 дают уже существенное расширение области работоспособиости ЗУ. Предмет изобретения Запомипающее устройство содержащее накопитель, соединенный с блоком управления но адресным и разрядным цепям, блоками считывания и блоком синхронизации, связанным с блоком унравления по адреспым и разрядным цепям, отличающееся тем, что, с целью повышения надежности работы устройства, в блок унравления по адресным и разрядным цепям введен дополнительный адресно-разрядный канал, соединенный с адресными и разрядными цепями дополнительного разря/;а накопителя, цепь считывапия которого связана с усилителем считывания, соединенным выходом со входами Л амнлитудных дискриминаторов с различными уровнями норогов срабатывания, выходы которых подключены к единичным входам Л триггеров, нулевые входы которых и блокировочные входы амплитудных дискриминаторов объединены и соединены с блоком синхронизации, причем единичные выходы триггеров связаны с цифроаналоговым нреобразователем, выход которого нодключен к управляющим входам блоков считывапия.

ГГ Г Г Г

| название | год | авторы | номер документа |

|---|---|---|---|

| ВХОДНОЕ УСТРОЙСТВО МНОГОКАНАЛЬНОГО АНАЛИЗАТОРА | 1967 |

|

SU199528A1 |

| Устройство для стабилизации средней частоты шумовых выбросов над пороговым уровнем | 1980 |

|

SU902269A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1970 |

|

SU287422A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368643A1 |

| Запоминающее устройство | 1972 |

|

SU474845A1 |

| Анализатор амплитудных распре-дЕлЕНий | 1979 |

|

SU798868A1 |

| Устройство для считывания графической информации | 1989 |

|

SU1635203A1 |

| УСТРОЙСТВО ДЛЯ ИНДИКАЦИИ ИНФОРМАЦИИ НА ЭКРАНЕ | 1973 |

|

SU377761A1 |

| Многофункциональное запоминающее устройство | 1972 |

|

SU458037A1 |

| Логическое запоминающее устройство | 1972 |

|

SU442512A1 |

Авторы

Даты

1973-01-01—Публикация