1

Изобретение относится к блокам памяти иифровых вычислительных машин и системам обработки информации, работоспособность котрых должна сохраняться в широком диапазоне изменения внешних условий (температуры, напряжений питания).

Известны запоминаклцие устройства (ЗУ), содержащие накопитель, блок синхронизации, ВЫХОД которого соединен с адресным блоком управления, и блок записи-воспроизведения, соединенный с накопителем и блоком синхронизации, в которых для повышения отношения сигнал/помеха иа входе усилителя .считывания (УС) в диапазоне температур управление накопителем производится токами, выборки, изменяющимися по определенному закону в зависимости от температуры окружающей среды.

В известных устройствах производится косвенное отслеживание токами выборки в-диа.аазоие температур за отношением сигнал/ромеха на выхсде матриц памяти накопителя. Точное воспроизведение требуемых законов изменения токов выборки от температуры затруднено из-за сложного и многофакторно-

го влияния температуры на процессы в магнитных элементах памятк, а линеаризация этих законов ведет к потере точности.

Цель изобретения - повышение информационной надежности ЗУ. Достигается это тем, что в устройство введены дополннтель ный блок синхронизации состояишй из генератора raKfoB и контрольных обращений, сч тчика контрольных офащений и блока режи ма, блок адаптации, содержащий усилитель воспроизведения, преобразователь амплитудакод, регистр делителя, блок деления, буферный регистр, блок сравнения, триггер; элемент ИЛИ, два элемента И, реверсией ыйсчвт чик, дря преобразователя ; код-напряжение, сумматор.

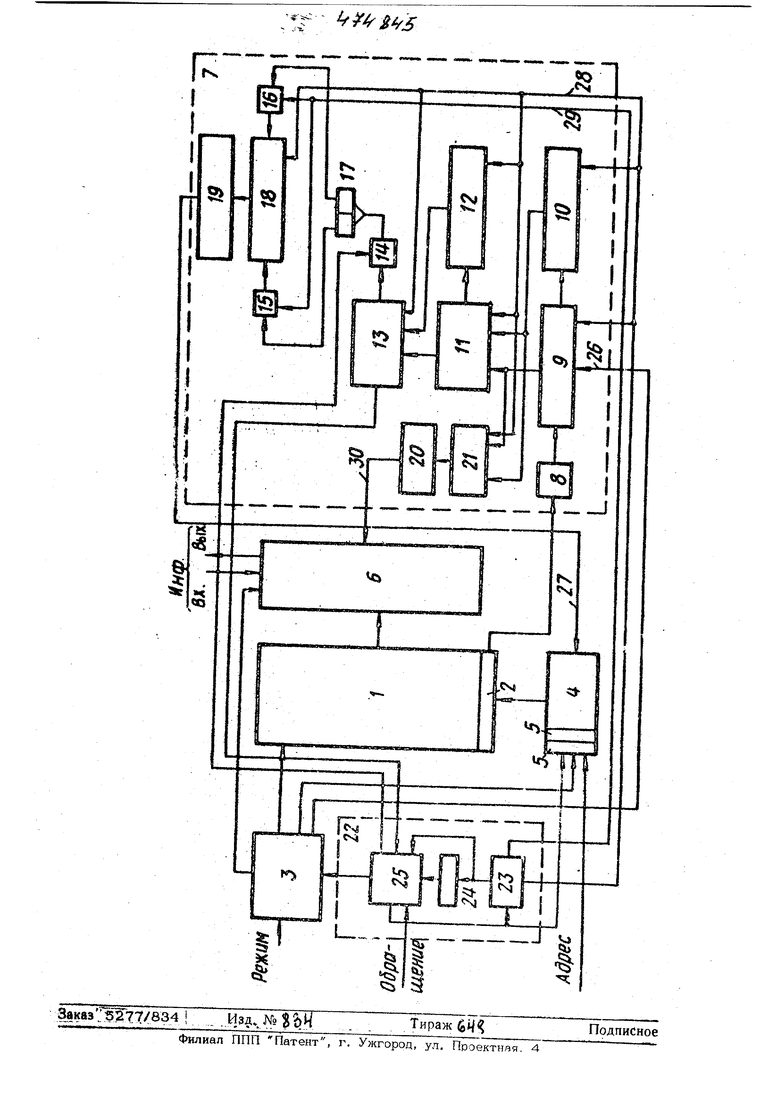

Блок адаптации обеспечивает дискретное j оптимальное управление токами выборки, а Iдополнительный блок синхронизации производит выбор режима контроль или работа и управляет работой блока адаптации. В адресный блок управления введены два дополнительных адресных канала, причем в первом дополнительном адресном канале постоянно за-писан О, а во втором - , В дополнительном рёорйде накош1теля постоянно aami сантяжелый код (например, шахматный порядок - По всем четным адресам - 1, по нечетным адресам - О), На чертеже изображена блок-чзхема ЗУ. Запоминающее устройство содержит нйко питель 1 с дополнительным разрядом 2, блох синхронизации 3, адресный блок управления 4 с двумя дополнительными адреса- ными каналами 5i блок записи-вое произвел ения информации €, ёлок адаптации 7, состоявши из усипителя воспроизведения 8, преоб- раЗователя амплиту;да код .Э, регистра делителя 10, блока деления 11, буферного реги-™ стра 12, блока сравнения 13, элемента (ИЛИ 14, элементов ГИ 15,16, тригтера 17, р&версивного счетчика 18, преобразователей код-напряжение 19 и 2О и сумматора 21. Кроме того, в ЗУ введен допопнительный блок синхронизации 22, состоящий из генератора 23 тактов и контрольных обращений, счетчика 24 контрольных обращений |и блока режима 25. , . . ЗУ работает; следую1цим образом. Перед I началом работы-ycraiiaanHBaeTC я исходноасостояние ycTpoiicTBaj Этому состояниюсоответствует установка блока режима 25 в режим контроль, обнуление всех триггеров схемы ЗУ и установка реверсивного счетчика 18 в состояние, соответствующее коду 2 , где пг - число разрядов регистра делителЪ 10, буферного регистра 12 и ревер сивного счетчика 18. При этом преобразователь код-напряжение . 19 в,ыдает усредненное значение управляющего напряжения и соответственно исходное значение токов выборки равно - LiilSiLiiHJiiS . Затем начинается первый цикл адаптации, состояшлй из двух контрольных обращений iio дополнительным адресным каналам.; Считанные гфи контрольных обращениуос с игналы поступают.; на линейный уститель воспроизведения 8 блока адаптации 7, с выхода которого усиленный сигнал подается на преобразователь ампл.итуда-код 9. Работой преобразователя I а1 плитуда-код 9 управляет строб с вьгхода усилителей воспроизведения основного блока синхронизации 3 (провод 26),.р- зрешающий работу преобразователя 9 только во время действия полезного считанного сигнала. При первом контрольном обращении амп литуда считанной помехи (сигнал ООЕ преобразуется в цифровую форму преобразова телей амплитуда-код 9 и -переписывается регистр делителя 10. При втором контрольном обращении первого цикла амплитуда считанного стЕгнала 1 преобрзуеФся в цифровую форму преобразователем амплитуда-код 9 и ,в блоке деления 11 вычис-iляется OTHoaifeHHe сигнал/помеха: ж-Д- Выходы блока деления 11 и буферного регистра 12 соединены с, входами блока сравнения 13 Так как при первом цикле адаптации буферный регистр 12 был обнулен, .Q к блок сравнения всегда определяет, что pj . На блока cpaBHef1шя 13 формируется сигнал, если П в; 1тротивном случае (т.е. ког- л j.,.i( да ni)- . ) сигнал на выходе блокасравнения отсутствует. Выход блока сравнения 13 соединен со счетным входом тригге ра, 17, а его выходь управляют элементами -Й 15 и 16, тактируемыми одиночными импульсами генератора 23 тактов и контрольных обращений. Элементы И 15 и 16 управляют соответственно входами сложения и вылитания реверсивного счетчика 188 задающего через преобразователь код-напряжение 19 сигнал управления токами выборки адресного блока упрашения 3 (шина 27). Все тактовые цепи блока адаптация, 7 пкт&ются генератором 23 тактов и контрольных обраш НИИ (провода 28 а 29). Сигнал установки в исходное состояние формируатся в блоке ; режима 25 (на чертеже цепи установки в исходное состояние не показаны). Контрольные циклы, адаптации продолжаются, до тех пор, пока не окажется, , пока не пройдет 2 контрольных циклов, В первом случае производится изменение токов выборки на один шаг в обратном направлении и перевод устройства блоком режшла 25 в режим забота Во втором случае воэмояшы; две сит}/ацииг если хотя бы. в одном из 2 контрольных циклов блок сравнения 13 фиксировал несовпадение отноще- НИИ сигнал/помеха то блок режима 25 переводит ЗУ в режим рабг ты; если при всех 2. контрольных обращениях отнбшение const (где 1 L $2 ), то производится возврат токов выборки к первоначальному значению и подача новых контрольных циклов обращений с изменением токов выборки в противоположном направлении до тех пор, пока не будет найден максимумП-МАКСЕсли и здесь при 2 контрольных циклах отношение rM -COnst , то блок режима25 (по команде с блока сравнения 13) переводит схему ЗУ в режим работа Количество контрольньгх циклов обращений может быть различным и определяетсл. тем, насколько начальное значение токов вы-борки удалено от оптимального. Максимаатьное количество контрольных циклов адаптации равно всем возможнь м комбинациям реверсивного сЧетчика 18, т. е, 2, j Число разрядов преобразования пх в блоке |адапташш 7 определяет точность установки настраиваемого параметра; Практ11чески впод не достаточно иметь tv 4T5s так как в 1 случае точность установки токов вЫ. 1борки на максимум отноидения еигнал/по-меха составит i-{9,5)%. Таким образом, перед началом работы, ,а затем периодически блок управления 4 настраивается на максимум отношения сиг™ |н ал/помеха для любь5х внешних условий раб :ты. Однако для различных внешнюс условий мож.вт потребоваться различный оптнмалъны .режим работы усилителей считывания блоков 1запис1 воспроизведе1« я 6.Действительно, оптимальное значение порога дискримш15ййи Е|чможет быть ра-зличным в зависимости от : имеющих место . .j -ых внеияшх условий. .Поэтому при работе с фиксированньш значением-порога Е область работоспособности ограничена возможностью сбоев при таких J fn -bix внешних условиях, ковда ное значение порога Е сильно отличает.. ся от фиксированного значения Е „ф . Поэтому для дальнейшего расширения области работоспособности ЗУ необходимо пЬред на«чалом работы настраивать не только токи |выборки адресного блока утфавления 4, но и порог дискриминации усилителей воспроиз.Ведения в разрядном блоке записи-воспроизведения 6. Для этого после настрой Ш , блока адаптации 7 на оптимальное значение оков вы.борки необходш.10 амплитуды ci .лов Е и Е , хранящиеся в цифровой форме ;соответственно в преобразователе амплиту- ; да-код 9 Ирегистре делителя Ю. подать на сумматор 21 {формула 1), а его выход Через преобразователь код-напряжение 2О I ПОДКЛЮЧИТЬ к входу, управляющему порогом дискриминации (или коэффтшентом ус1.1ления усилителей воспроизведения разрядного блока записи-восгфоизведения 6 (щина 30). Следовательно .для любых внешних условий работы (температуры, напряжений питания накопителя) реализуется i наилучший реЖ1Ш воспроизведения информации, так как обеспечивается максимальное отношение сигнал/пемеха, а порог дискриминации всегi да выбирается посередине между полезньп 1 сигналом и помехой (формула 1). Поэтому предложенное устройство позволяет полностью использовать физические возможности элементов памяти, обеспечивая максималь- ;но достижимую область работоспособности ЗУ, Предмет кзобретения Запоминающее устройство, согГержашее на/копитель, соединенный с блоком сиюсрониэа«ии, выход которого соединен с адресным |блоком Ipaвлeния, блок эапнси-воспроизве ;дения, соединенный с накопителем и блоком синхронизации, отличающе е я |тбм, что, с целью повышения надежности/ в устройство введены дополнитачьный блок СИ1Ь хронизацин, состояийий из генератора контрольк.к обращений, счетчика контроль обращений и блока режима, блок адаптаi,,,, содерх ащиГ усилитель воспрЬизведения .;преоёразоБатель амплитуда-код, регистр делителя, блок деления, буферный регистр, бло1с сравнения, триггер, элемент ИЛИ, иваэлемента И, реверсивный счетчик, два прёобразователя код-напряжение, сумматор.ТФИдчем вход обращение запоминающего устрой.. соединен с входом блока реишма, выхО, ГхОторого подключены к входу основного д,,,. сшщюн зашш, входу генератора так:, контрольных обращений и входу адрес ого блока управления, выходы генератора соединены с входом счетчика контрольных о6ращениЙ5 выходы которого подключены |с управляющим входам блока режима, выход дополнительного разряда накопителя через iycT-щитель воспроизведения соединен с преобразователем амплитудаг-код блока адаптаЕпи, выходы преобразователя амплитуда-код подюпочены к входам ;блока деления и ре1истра делителя; выход блока деления сое- .en с одним из входов блока сравнениям входом бу(ерного регистре, выход которого |годключен к другому входу блока сравнения, вь5ход котого подключен к первому входу элемента ИЛИ, другой вход которого соединен с выходом блока режима, а выход элемента ИЛИ соединен со счетным входом триггера, выходы триггера подклкзчены к первым входам элементов И, вторые входы которых соед}тены с выходом генератора дополнительного блока синхронизации, а выходы элементов И соединены со входами соответственно сложения и вычитания реверсивног-о счетчика, выход реверсивного счетчика через первый преобразователь коД онапряжение соединен с уп1завлягощим входом адресного блока управления; входы сумматора соединены с выходами преобразователя амплитуда-код и регистра делителя, вьтходы сумматора соединены со входами второго преобразователя код напряжение, выход которого подклю-чен к входу записи-воспроизведения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1976 |

|

SU731473A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| ПРИЕМНОЕ УСТРОЙСТВО ГИДРОЛОКАТОРА БОКОВОГО ОБЗОРА | 1993 |

|

RU2060516C1 |

| Устройство подавления помех | 1988 |

|

SU1589403A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ГИДРОЛОКАТОРА БОКОВОГО ОБЗОРА | 1992 |

|

RU2060515C1 |

| Цифровая адаптивная антенная система | 1990 |

|

SU1810943A1 |

| Устройство синхронизации М-последовательности | 1989 |

|

SU1748274A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1988 |

|

SU1606996A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

Авторы

Даты

1975-06-25—Публикация

1972-06-16—Подача