1

Изобретение относится к области запоминающих устройств (ЗУ).

Известно логическое ЗУ, содержащее накопитель, выполненный на ферромагнитных сердечниках с прямоугольной петлей гистерезиса, входы которого соединены с выходами формирователей разрядных и адресных токов, а выходы - с усилителями считывания, регистр числа, входы которого подсоединены к выходам соответствующих схем «И, а выходы - к одним входам схем «И и входам схем унравления, подсоединенным к формирователям разрядных токов, и схемы задержки, подключенные к усилителям считывания.

Недостатком известного ЗУ является то, что оно содержит громоздкие и ненадежные элементы - схемы задержки.

Описываемое ЗУ отличается от известного тем, что оно содержит схемы «НЕ по числу разрядов накопителя, входы которых подключены к выходам соответствующих усилителей считывания, а выходы - к другим входам схем «И.

Это позволяют упростить устройство и повысить надежность его работы.

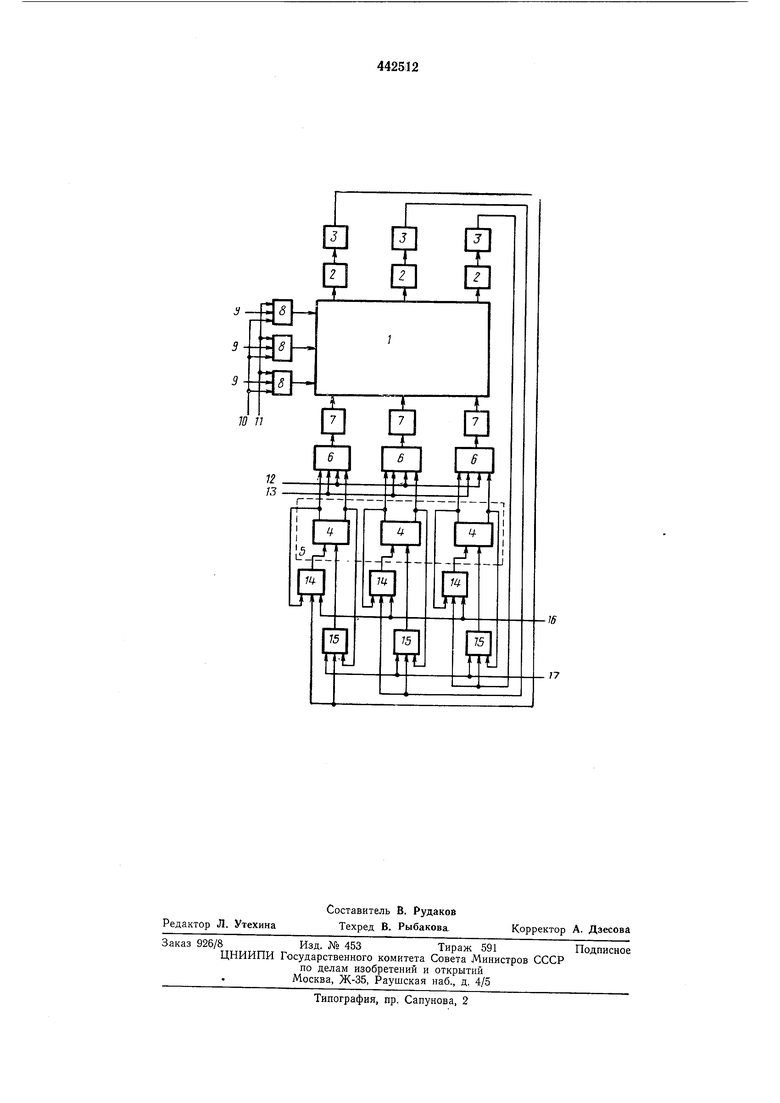

На чертеже показ ана структурная схема логического ЗУ, выполняющего логические операции «сумма по модулю два и «логическая равнозначность с образованием результата операций в ячейке памяти.

Оно содержит накопитель, выполненный по одной из схем 2Д или ЗД, усилители считывания 2, схемы «НЕ 3 по числу разрядов, триггеры 4 регистра числа 5, схемы унравления 6, формирователи разрядных токов 7, формирователи адресных токов 8, имеющие адресные входы 9.

Другие входы формирователей 8 подключены к управляющим шинам 10 и 11. Входы схем управления 6 подключены к управляющим щинам 12 и 13. «Нулевые выходы триггеров 4 соединены с одними входами схем

«И 14, а «единичные - с одними входами схем «И 15. Входы схем «НЕ подключены к выходам усилителей считывания 2, а выходы- к другим входам схем «И 14 и 15. Третьи входы схем «И 14 и 15 подсоединены к управляющим щинам 16 и 17.

Устройство работает следующим образом. При выполнении логической операции «сумма по модулю два выбранный формирователь 8 формирует импульс тока записи, а

формирователь 7 - ток запрета записи в тех разрядах, где триггеры 4 установлены в «нуль. В результате действия адресных и разрядных токов в ячейке памяти накопителя 1 образуется результат поразрядной дизъюнкции двух слов: хранимого в ячейке памяти и записанного в регистр числа 5. При этом в выбранной ячейке памяти производится неремагничивание сердечников из нулевого состояния в единичное в тех разрядах, где в регистре числа о записана «единица, а в 5 ячейке памяти пакопителя 1 хранится «нуль. Следовательно, па выходах усилителей считывания 2 возникают единичные сигналы, соответствующие поразрядной логической функцни «запрет от У, а ца выходах схем «НЕ Ю 3 - сигналы, соответствующие функции «импликация от X к У. На входы схем «И 14 подается синхросигнал по шине 16, а на их выходах появляется сигнал, соответствующий поразрядной «конъюнкции двух слов: хра- 15 нимого в ячейке памяти и записанного в регистр числа 5. Код с выходов схем «И 14 записывается в регистр числа 5. В следующем такте осуществляется коррекция результата путем считывапия в тех 20 разрядах, где сигнал на выходах схем «И 14 соответствовал логической «единице. Для этого формирователь 8 вырабатывает ток считывания, который поступает в выбранные адреспые шипы пакопителя 1. В тех разря- 25 дах, где выходной сигнал схем «И 14 «нулевой, считывание не производится, так как формирователи 7 в этом случае по сигпалу, поступающбхму на шину 13, выдают в разрядные шины токи занрета считывания. Нри выполнении онерации «логическая равнозначность в первом такте по сигпалу на шине 10 формирователь 8, как и в первом случае, вырабатывает импульс тока записи, но формирователи 7 но сигналу на шине 1235 формируют импульсы тока запрета записи в тех разрядах, где триггеры 4 установлены в состояние «единица. В результате в ячейке памяти образуется код, соответствующий результату логической операции «импликация40 от X к F, а па выходах усилителей считывания 2 - результат «операции Пирса. Единич30ный сигнал на выходах схем «НЕ 3 соответствует дизъюнкции одноименных разрядов слов: записанного в регистре 5 и хранимого в ячейке памяти. Эти сигналы подаются на входы схем «И 15 и, при наличии сигнала на шине 17 с их выходов на входы триггеров 4. Этот код является результатом конъюнкдни отрицания переменной X, храняпгейся в регистре 5, и дизъюнкции переменных X и Y, т. е. «запрет по А . В следующем такте производится коррекция путем считывания в тех разрядах, где сигнал на выходах схем «И 15 был равен «единице, в остальных разрядах формируются токи запрета считывания, так как содержимое ячейки памяти является дизъюнкпией двух функций: «логическая равнозначность и «запрет по X двух переменных. Предмет изобретения Логическое запомипающее устройство, содержащее накопитель, выполненный на ферромагнитных сердечниках с прямоугольной петлей гистерезиса, входы которого соединены с выходами формирователей разрядных и адресных токов, а выходы - с усилителями считывания, регистр числа, входы которого подсоединены к выходам соответствующих схем «И, а выходы - к одним входам схем «И и входам схем управления, подсоединенным к формирователям разрядных токов, отличающееся тем, что, с целью упрощения устройства и повышения надежности его работы, оно содежит схемы «НЕ по числу разрядов пакопителя, входы которых подключены к выходам соответствующих усилителей считывания, а выходы - к другим входам схем «И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1972 |

|

SU464017A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368643A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU258388A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО" | 1973 |

|

SU368606A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО3 :1 Т ВФОН]] Я-И;ф'РТГЩ <" t- J J^^ '^ • i .• f S .„ J i, is i* | 1972 |

|

SU433541A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВОФШД | 1973 |

|

SU429466A1 |

| Логическое полноточное запоминающее устройство | 1974 |

|

SU470861A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

Авторы

Даты

1974-09-05—Публикация

1972-10-02—Подача