11

Изобретение относится к области автоматики, телемеханики и вычислительной техники и может быть использовано при реализации технических средств дискретной автоматики, телемеханики и вычислительнмх машин.

Известны распределители импульсов, содержащие п триггеров, входы установки в нулевое и единичное состояние каждого i-ro из которых, кроме первого (t-2, З...п), через схемы «И сброса и установки связаны соответственно с инверсным и прямым выходами п-то триггера, дешифратор, состояш,ий из 2 п схем «И, выходы которых связаны с выходными шинами устройства.

Однако известные устройства имеют невысокое быстродействие Предлагаемое устройство отличается от известных тем, что в нем один из входов каждой t-ой схемы «И дешифратора, «роме /г-ой (М, 2, 3,... (п-1)), другим входом связанной с выходом 1-ой схемы «И сброса, соединен с инверсным выходом (г+1)-го триггера, а входы п-ой схемы «И дешифратора связаны с прямым выходом первого триггера и выходом ге-ой схемы «И сброса соответственно; один из входов каждой Ki-OH схемы «И дешифратора (Кг п+1, ,... ..., Кп 2п-1) другим входом связанной с выходом г-й схемы «И установки , 2, 3, ... («-1)), соединен с прямым -выходом (i+l)-ro

И

триггера, а входы 2 п-ой схемы «И дешифратора связаны с инверсным выходом первого триггера и выходом п-ои схемы «И сброса соответственно; другие входы каждой г-ой

схемы «И сброса (/-нечетное число) связаны с первой шиной тактовых сигналов, а /-ОЙ схемы «И сброса (/-четное число) - со второй шиной тактовых сигналов; другие входы каждой из схем «И установки

связаны с одной из шин тактовых сигналов. Такое выполнение устройства позволяет увеличить его быстродействие.

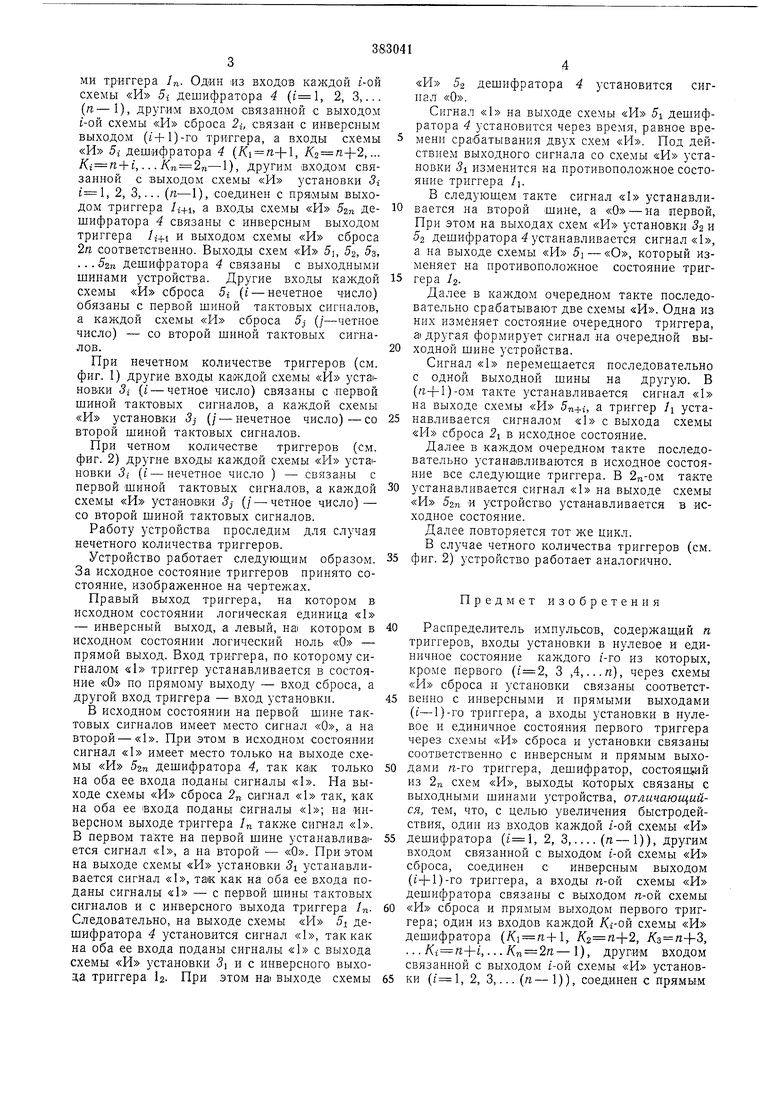

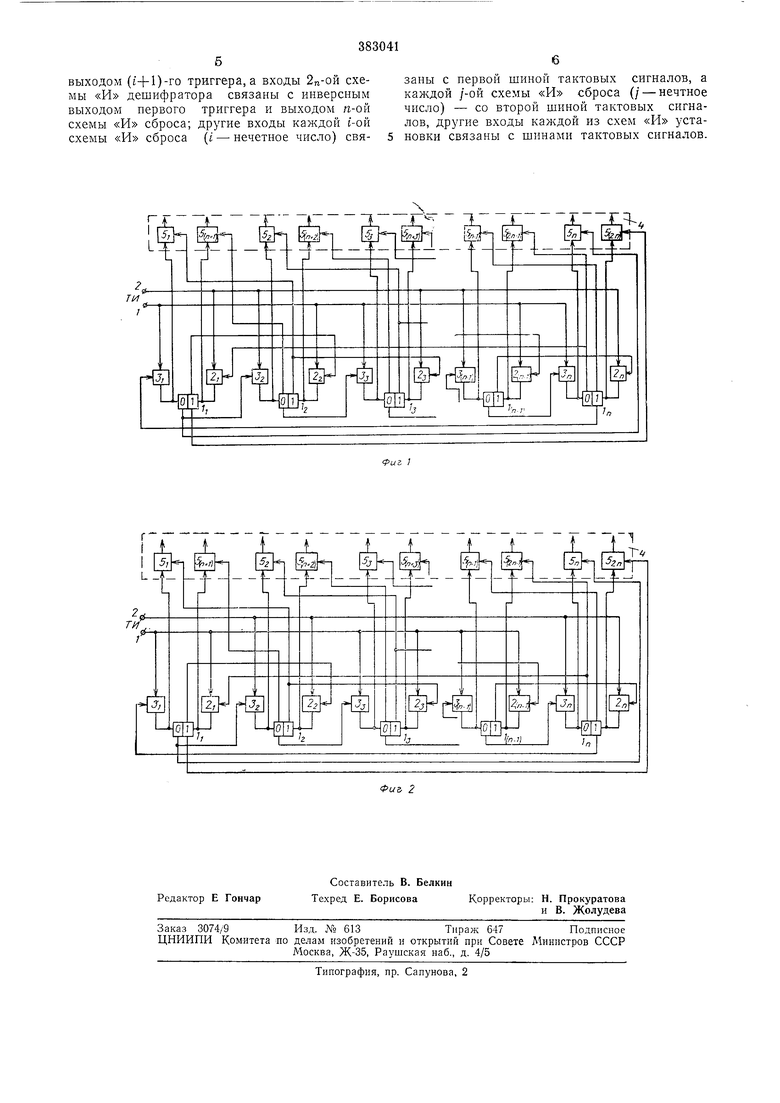

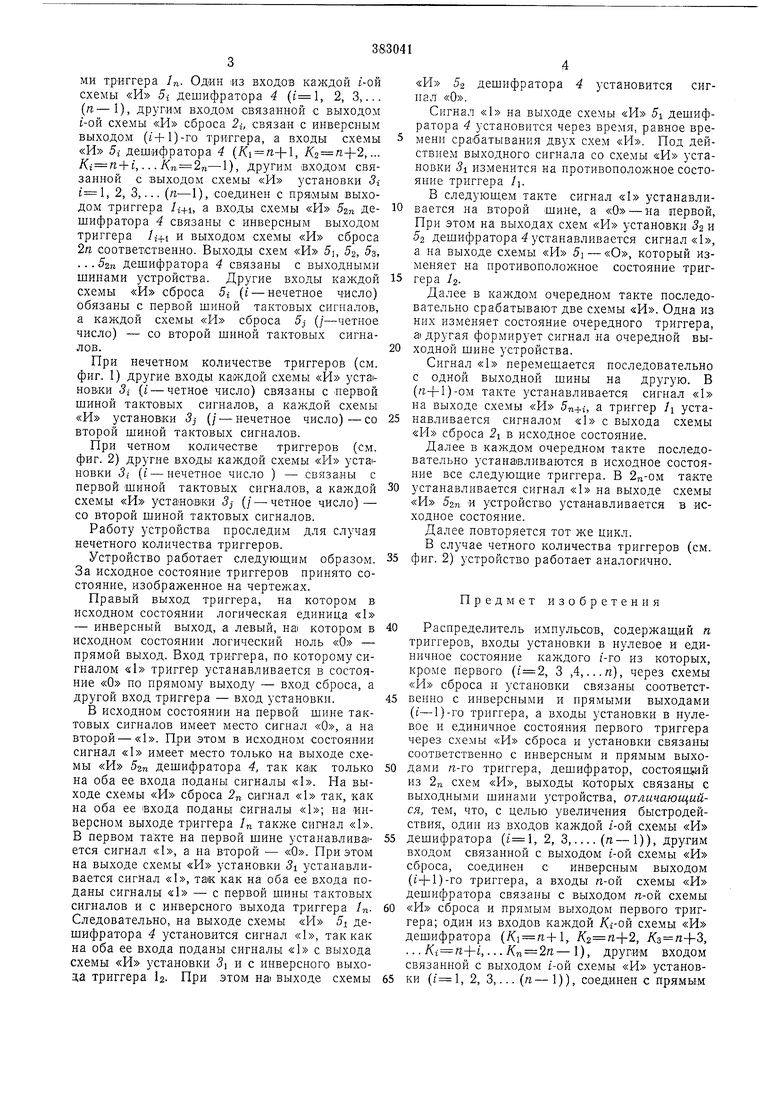

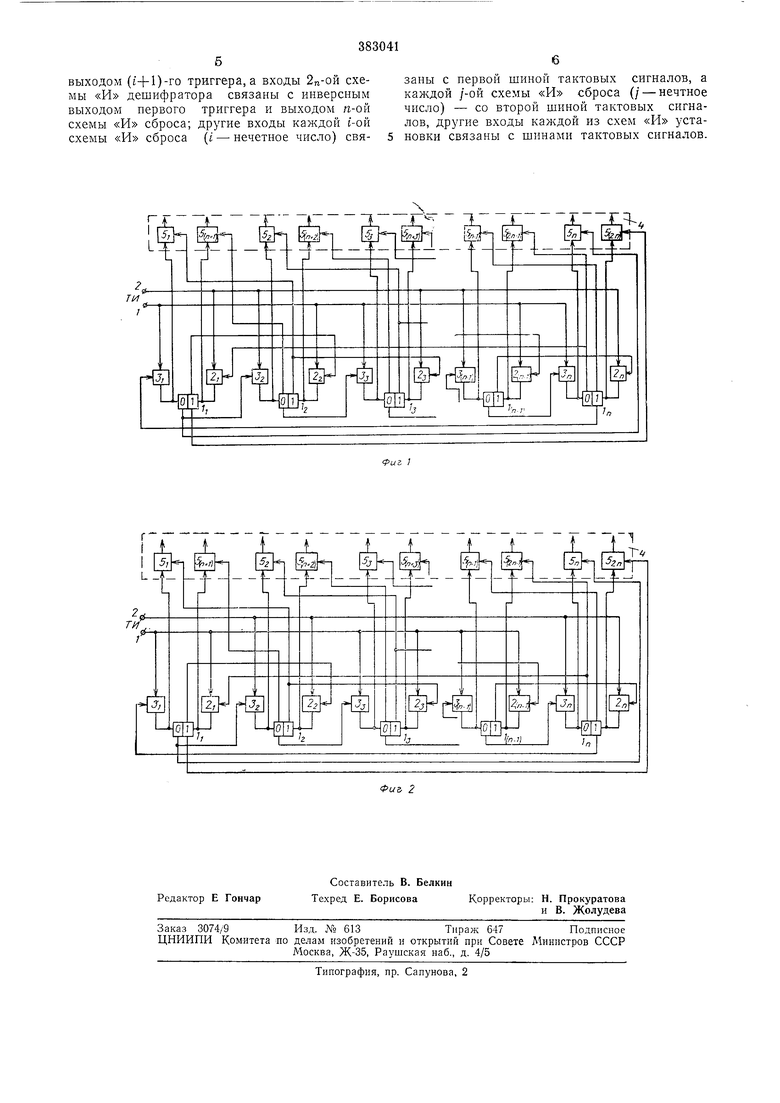

На фиг. 1 представлена блок-схема предлагаемого устройства для случая четкого количества триггеров (); на фиг. 2 - для нечетного количества триггеров (n 2fe+i).

Предлагаемое устройство содержит п триггеров (/1, /2, /3, - 71, п схем «И сброса 2, 22, 2з2„, п схем «И установки

5, 52, 5зЗп, дешифратор 4, состояш,ий

из 2п схем «И 5i, 5, 5з,.... 5п.

Входы установки в нулевое и еднннчное состояния каждого t-ro триггера (Ij), кроме первого (i -2, 3, 4, ...п) через схему «И

сброса 2; и схему «И установки Зг связаны соответственно с инверсными прямыми выходами (г-1) триггера l, а входы установки в нулевое и единичное состояния триггера /1 через схему «И сброса 2i и схему «И

установки 3i с инверсными прямыми выхода3ми триггера In- Один «з входов г-ой схемы «И 5г дешифратора 4 (, 2, 3,... (п-1), другим входом связанной с выходом t-ой схемы «И сброса 2i, связав с инверсным выходом (i+l)-ro триггера, а входы схемы «И 5г дешифратора 4 (К п,-{-, 7(2 ,... + i,... )), другим входом связанной с выходом схемы «И установки Зг , 2, 3,... (п-1), соединен с прямым выходом триггера /i+i, а входы схемы «И Дешифратора 4 связаны с инверсным выходом триггера /i+i и выходом схемы «И сброса 2/г соответственно. Выходы схем «И 5, 5, 5з, -.Szn дешифратора 4 связаны с выходными шинами устройства. Другие входы каждой схемы «И сброса 5t (i - нечетное число) обязаны с нервой шиной тактовых сигналов, а каждой схемы «И сброса 5j (j-четное число) - со второй шиной тактовых сигналов. При нечетном количестве триггеров (см. фиг. 1) другие входы каждой схемы «И ycTaiновки 3i (i - четное число) связаны с нервой шиной тактовых сигналов, а каждой схемы «И установки 5j (/ - нечетное число)-со второй шиной тактовых сигналов. При четном количестве триггеров (см. фиг. 2) другие входы каждой схемы «И ycTaiновки Зг (i - нечетное число ) - связаны с иервой шиной тактовых сигналов, а каждой схемы «И установки 5,- (/ - четное число) - со второй шиной тактовых сигналов. Работу устройства проследим для случая нечетного количества триггеров. Устройство работает следуюшим образом. За исходное состояние триггеров принято состояние, изображенное на чертежах. Правый выход триггера, на котором в исходном состоянии логическая единица «1 - инверсный выход, а левый, Hai котором в исходном состоянии логический ноль «О - прямой выход. Вход триггера, по которому сигналом «1 триггер устанавливается в состояние «О по прямому выходу - вход сброса, а другой вход триггера - вход установки. В исходном состоянии на первой шине тактовых сигналов имеет место сигнал «О, а на второй - «1. При этом в исходном состоянии сигнал «1 имеет место только на выходе схемы «И Szn дешифратора 4, так как только на оба ее входа поданы сигналы «I. На выходе схемы «И сброса 2п сигнал «1 так, как на оба ее входа поданы сигналы на инверсном выходе триггера In также сигнал «1. В первом такте на первой шине устанавливай ется сигнал «1, а на второй - «О. При этом на выходе схемы «И установки 5i устанавливается сигнал «1, так как на оба ее входа поданы сигналы «1 - с первой шины тактовых сигналов и с инверсного выхода триггера InСледовательно, на выходе схемы «И 5 дешифратора 4 установится сигнал «I, так как на оба ее входа поданы сигналы «1 с выхода схемы «И установки 5i и с инверсного выхода триггера Ь. При этом Hai выходе схемы «И 59 дешифратора 4 установится сигпал «О. Сигнал «1 на выходе схемы «И 5i дешифратора 4 установится через время, равное времени срабатывания двух схем «И. Под действием выходного сигнала со схемы «И установки 5i изменится на противоположное состояние триггера /. В следующем такте сигнал «I устанавливается на второй шине, а «О - на первой. При этом на выходах схем «И установки 82 и 52 дешифратора 4 устанавливается сигнал «1, а на выходе схемы «И 5 - «О, который изменяет на противоположное состояние триггера IzДалее в каждом очередном такте последовательно срабатывают две схемы «И. Одна из них изменяет состояние очередного триггера, ai другая формирует сигнал на очередной выходной шине устройства. Сигнал «1 перемешается последовательно с одной выходной шины на другую. В («-|-1)-ом такте устанавливается сигнал «1 на выходе схемы «П 5n+i, а триггер /i устанавливается сигналом «1 с выхода схемы «И сброса 2i в исходное состояние. Далее в каждом очередном такте последовательно устанавливаются в исходное состояние все следуюпдие триггера. В 2ri-OM такте устанавливается сигнал «1 на выходе схемы «И 5zn и устройство устанавливается в исходное состояние. Далее повторяется тот же цикл. В случае четного количества триггеров (см. фиг. 2) устройство работает аналогично. Предмет изобретения Распределитель импульсов, содержащий п триггеров, входы установки в нулевое и единичное состояние каждого ;-го из которых, первого (, 3 ,4, ...п), через схемы «И сброса и установки связаны соответственно с инверсными и прямыми выходами (i-1)-го триггера, а входы установки в нулевое и единичное состояния первого триггера через схемы «И сброса и установки связаны соответственно с инверсным и прямым выходами п-го триггера, дешифратор, состояц ий из 2п схем «И, выходы которых связаны с выходными шинами устройства, отличающийся, тем, что, с целью увеличения быстродействия, один из входов каждой i-ой схемы «И дешифратора (, 2, 3,- (п-1)), другим входом связанной с выходом f-ой схемы «И сброса, соединен с инверсным выходом (i-}-l)-ro триггера, а входы п-ой схемы «И дешифратора связаны с выходом п-ой схемы «И сброса и прямым выходом первого триггера; один из входов каждой Ki-ой схемы «И дешифратора (, К2 п-{-2, /Сз л+3, ,.. /Сг - tt+i,... /Си 2п - 1), другим входом связанной с выходом f-ой схемы «И установки (, 2, 3,... (я-1)), соединен с прямым

б

выходом (i+l)-ro триггера, а входы 2п-ой схемы «И дешифратора связаны с инверсным выходом первого триггера и выходом п-ой схемы «И сброса; другие входы каждой t-ой схемы «И сброса (i - нечетное число) свя6

заны с первой шиной тактовых сигналов, а каждой /-ОЙ схемы «И сброса (/ - нечтное число) - со второй шиной тактовых сигналов, другие входы каждой из схем «И установки связаны с шинами тактовых сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сортировки чисел | 1989 |

|

SU1793438A1 |

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| Устройство для индикации | 1988 |

|

SU1702418A1 |

| Распределитель тактовых импульсов | 1986 |

|

SU1411966A1 |

| Устройство для контроля 2-кода Фибоначчи | 1988 |

|

SU1662009A1 |

| Делитель частоты следования импульсов | 1988 |

|

SU1596453A1 |

| Голографическое постоянное запоминающее устройство | 1990 |

|

SU1725258A1 |

| Делитель частоты с нечетным коэффициентом деления (его варианты) | 1982 |

|

SU1132368A1 |

| Устройство для передачи цифровой информации | 1976 |

|

SU595761A1 |

| Кольцевой счетчик | 1988 |

|

SU1531213A1 |

Авторы

Даты

1973-01-01—Публикация