Изобретение относится к импульсной технике и может быть использовано в 1ЩФРОВОЙ измерительной аппаратуре, в синтезаторах частоти в устройствах автоматики.

.Цель изобретения - повышение рабочего диапазона частот при делении на нечетные козффициенты деления.

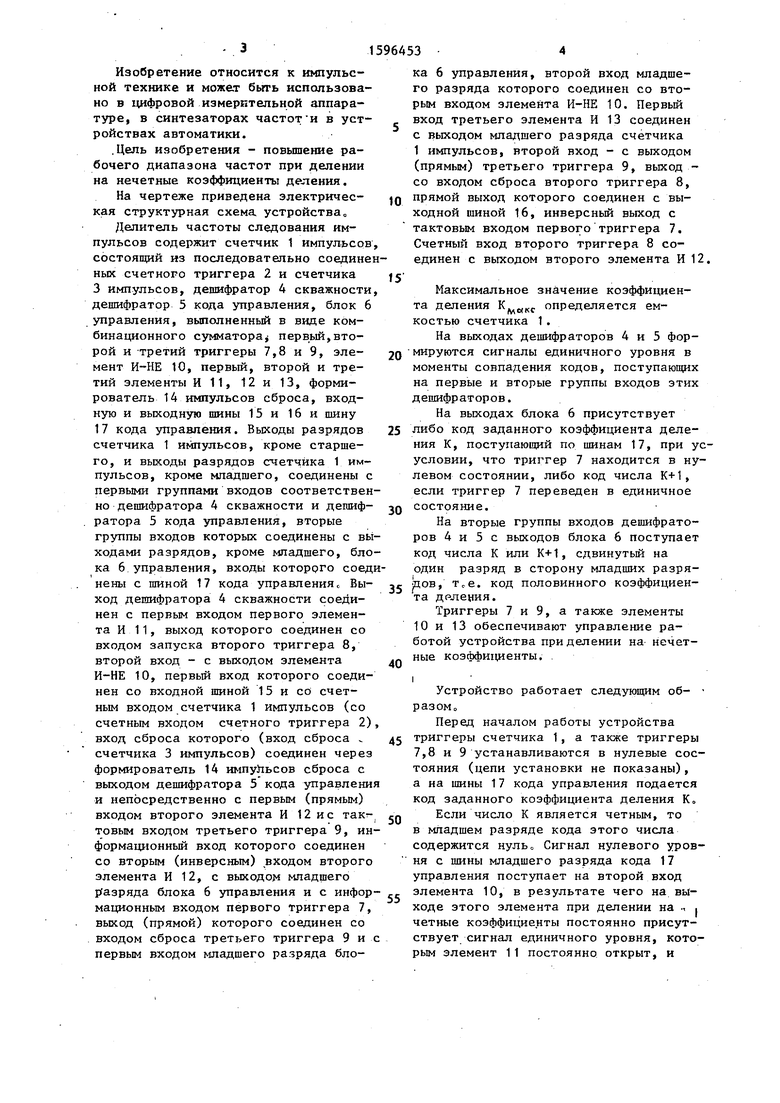

На чертеже приведена электрическая структурная схема, устройства,,

Делитель частоты следования импульсов содержит счетчик 1 импульсов, состоящий из последовательно соединенных счетного триггера 2 и счетчика 3 импульсов, дешифратор 4 скважности, дешифратор 5 кода управления, блок 6 управления, выполненньй в виде комбинационного сумматораj первь1й,второй и третий триггеры 7,8 и 9, элемент И-НЕ 10, первый, второй и третий элементы И 11, 12 и 13, формирователь 14 импульсов сброса, входную и выходную шины 15 и 16 и шину 17 кода управления. Выходы разрядов счетчика 1 иьшульсов, кроме старшего, и выходы разрядов счетчика 1 импульсов, кроме младшего, соединены с первыми группами входов соответственно дешифратора 4 скважности и дешифратора 5 кода управления, вторые группы входов которых соединены с выходами разрядов, кроме младшего, блока 6 управления, входы которого соединены с шиной 17 кода управления с Выход дешифратора 4 скважности соединен с первым входом первого элемента И 11, выход которого соединен со входом запуска второго триггера 8, второй вход - с выходом элемента И-НЕ 10, первый вход которого соединен со входной шиной 15 и со счетным входом счетчика 1 импульсов (со счетным входом счетного триггера 2), вход сброса которого (вход сброса . счетчика 3 импульсов) соединен через формирователь 14 импульсов сброса с выходом дешифратора 5 кода управления и непосредственно с первым (прямым) входом второго элемента И 12 и с такгтовым входом третьего триггера 9, информационный вход которого соединен со вторым (инверсным) входом второго элемента И 12, с выходом младшего разряда блока 6 управления и с информационным входом первого триггера 7, выход (прямой) которого соединен со входом сброса третьего триггера 9 и с первым входом младшего разряда блока 6 управления, второй вход младшего разряда которого соединен со вторым входом элемента И-НЕ 10. Первый вход третьего элемента И 13 соединен с выходом младшего разряда счетчика 1 импульсов, второй вход - с выходом (прямым) третьего триггера 9, выход со входом сброса второго триггера 8, прямой выход которого соединен с выходной шиной 16, инверсный выход с тактовым входом первого триггера 7. Счетный вход второго триггера 8 соединен с выходом второго элемента И 1

Максимальное значение коэффициента деления К. определяется емкостью счетчика 1.

На выходах дешифраторов 4 и 5 формируются сигналы единичного уровня в моменты совпадения кодов, поступающих на первые и вторые группы входов этих дешифраторов.

На выходах блока 6 присутствует либо код заданного коэффициента деления К, поступаюш 1й по шинам 17, при уусловии, что триггер 7 находится в нулевом состоянии, либо код числа К+1, если триггер 7 переведен в единичное состояние.

На вторые группы входов дешифраторов 4 и 5 с выходов блока 6 поступает код числа К или К+1, сдвинутьй на один разряд в сторону младших разрядов, . код половинного коэффициента дрлеиия.

Триггеры 7 и 9, а также элементы 10 и 13 обеспечивают управление работой устройства при делении на нечетные коэффициенты. .

I

Устройство работает следующим образомо

Перед началом работы устройства триггеры счетчика 1, а также триггеры 7,8 и 9 устанавливаются в нулевые состояния (цепи установки не показаны), а на шины 17 кода управления подается код заданного коэффициента деления К„

Если число К является четным, то в мпадшем разряде кода этого числа содержится нуль о Сигнал нулевого уровня с шины младшего разряда кода 17 управления поступает на второй вход элемента 10, в результате чего на выходе этого элемента при делении на ., четные коэффициенты постоянно присутствует сигнал единичного уровня, которым элемент 11 постоянно открыт, и сигналы с выхода дешифратора 4 могут беспрепятственно проходить через эле мент 11 на вход запуска триггера 8. На выходе младшего разряда блока 6 при делении на четные коэффициенты также присутствует сигнал нулевого уровня. Этот сигнал поступает на информационные входы триггеров 7 и 9 и на второй вход элемента 12, в резуль тате этого триггеры 7 и 9 при делении на четные коэффициенты остаются нулевых состояниях, элемент 12 постоянно открыт, разрешая прохождение сигналов с выхода формирователя 14 на счетный вход триггеров 8, элемент 13 постоянно закрыт и устройство ра ботает слвдукяцнм образом. При подсчете 0,5К-го входного импульса с шины 15 на выходах счетчика 1 формируется код числа 0,5К. При этом срабатьюает дешифратор 4 и его выходным сигналом через открытый элемент 11 триггер 8 переводится в единичное состояние.На шине 16 при этом появляется выходной импульс. При подсчете К-го входного импуль са на выходах счетчика 1 формируется код числа К, а на выходах счетчика 3 - код числа 0,5К. При этом срабаты вает дешифратор 5 и его вькодной сиг нал запускает формирователь 14. Сигнал с выхода формирователя 14 поступает на вход сброса счетчика 1, а через открытьш элемент 12 - на счетный вход триггера 8. Счетчик 3 импульсов при этом сбрасывается в исходное состояние, а триггер 8 перехо дит в нулевое состояние. При этом заканчивается выходной импульс на ши не 16. В дальнейшем при делении на четные коэффициенты работа устройства повторяется. При делении на нечетные коэффициенты в младшем разряде кода управления содержится .единица. Сигнал единичного уровня с шины младшего разря да кода управления 17 поступает на второй вход элемента 10, Единичньй сигнал на выходе элемента 10 появляется в этом случае тольков паузах между входными импульсами. Поскольку исходное состояние триггера 7 нулевое, то на выходах блока6 в начале работы устройства устанавливается код числа Ко При этом на вто рые группы входов дешифраторов 4 и 5 поступает код числа 0,5 (К-1), а на информационные входы триггеров 7 и 1 3 9 и на второй вход элемента 12 с выхода младшего разряда блЬка 6 - сигнал единичного .уровня о Триггеры 7 и 9 подготавливаются при этом к переходу в единичные состояния, а счетньШ вход триггера 8 отключается от выхода формирователя 14 и устройство работает следующим образомо При подсчете 0,5(К-1)-го входного импульса срабатывает дешифратор 4 и его выходной сигнал поступает на второй вход элемента 11, В момент окончания О,5(к-1)-го входного импульса элемент 11 открьгоается и сигнал с выхода дешифратора 4 поступает на вход аапуска триггера 8 о Триггер 8 переходит в единичное состояние и на шине 16 появляется выходной импульс. При подсчете (К-1)-го входного импульса срабатывает дешифратор 3 и запускается формирователь 14. Сигнал с выхода формирователя 14, поступая на вход сброса счетчика 1, сбрасывает счетчик 3 в исходное состояние. Этот же сигнал поступает на тактовый вход тригге за 9, что приводит к переходу его в единичное состояние.Сигнал единичного уровня с выхода триггера 9 поступает на второй вход элемента 13. На первом входе элемента 13 в это время присутствует сигнал нулевого уровня, так как после подсчета каждого четного входного импульса триггер 2 оказывается в нулевом состоянии. При подсчете очередного К-го входного импульса триг-. гер 9 переходит в единичное состояние, в результате чего на выходе элемента 13 появляется сигнал единичного уровня, который поступает на вход сброса триггера 8, устанавливая его в нулевое состояние При этом заканчивается выходной импульс на шине 16, а на тактовом входе триггера 7 появляется сигнал единичного уровня, что приводит к переходу триггера 7 в единичное состояние. Сигнал единичного уровня с выхода, триггера 7 поступает на вход сброса триггера 9 и на первый вход младшего разряда блока 6. Триггер 9 при этом возвращается в исходное состояние, а на выходах блока 6 устанавливается код числа К+1о На этом заканчивается первьй цикл работы устройства при делении на нечетные коэффициенты . Состояние устройства перед вторым даклом работы при делении на нечетные коэффициенты отличается от исходного тем, что в счетчике 1 записана единица (так как К - число нечетное), а на вторые группы входов дешифраторов Л и 5 с выходов блока 6 поступает код числа 0,5(К+1). Поэтому во второй цик ле деления на нечетные коэффициенты устройство работает следующим образом При подсчете (К+0,5(К-1))-го входного импульса на выходах счетчика 1 формируется код числа 0,5(К-1)+1 0,5(К+1), в результате чего срабатывает дешифратор 4 и его выходным сигналом, после окончания (К+0,5(К-1))го входного импульса, триггер 8 переводится в единичное состояние. При подсчете 2К-го входного импуль са на выходах счетчика 1 формируется код числа К+1, а на выходах счетчика 3 - код числа 0,5(К+1). При этом срабатьшает дешифратор 5, запускается формирователь 14 и производится сброс счетчика 3, триггер 8 переходит в нулевое состояние/При переходе триггера 8 в нулевое состояние происходит переключение триггера 7 также в нулевое состояние, в результате чего на выходах блока 6 устанавливается код числа К и. устройство оказывается приведенным в исходное состояние В дальнейшем при делении на нечетные коэффициенты работа устройства повторяется сдвоенными циклами. Формула изобретения Делитель частоты следования импульсов, содержащий счетчик импульсов, выходы разрядов которого, кроме младшего, и выходы разрядов которого, кроме старшего, соединены с первыми группами входов соответственно дешифратора кода управления и дешифратора скважности, вторые группы входов которых соединены с выходамиразрядов, кроме младшего, блока управления, входы которого соединены с шинами кода управления, выход младшего разряда соединен с. информационным входом первого триггера, второй триггер,прямой выход которого соединен с выходной шиной, вход запуска - с выходом первого элемента И, первый вход которого соединен с выходом депшфратора скважности, второй вход - с выходом элемента И-НЕ, первый вход которого соединен с входной шиной и со счетным входом счетчика импульсов, вход сброса которого соединен с первым входом второго элемента И и через формирователь импульса сброса с выходом дешифратора кода управлеНИН, и третий триггер, отличающийся тем, что, с целью повышения рабочего диапазона частот при делении на нечетные- коэффициенты деления, блок управления выполнен в виде комбинационного сумматора и в него введен третий элемент И, первый вход которого соединен с выходом младшего разряда счетчика импульсов, выход - с входом сброса второго триггера, второй вход - с выходом третьего триггера, тактовый вход которого соединен с входом сброса счетчика импульсов, и информа1щонный вход - с выходом младшего разряда блока управления и с вторым входом второго элемента И, выход которого соединен со счетным входом второго триггера, инверсный выход которого соединен с тактовым входом первого триггера, выход которого соединен с входом сброса третьего триггера и с первым входом младшего разряда блока управления, второй вход младшего разряда которого соединен с вторым входом элемента И-НЕ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1547057A2 |

| Делитель частоты следования импульсов | 1985 |

|

SU1265996A1 |

| Делитель частоты следования импульсов | 1982 |

|

SU1045400A1 |

| Делитель частоты импульсов | 1985 |

|

SU1298907A1 |

| Симметричный делитель частоты импульсов | 1982 |

|

SU1089763A2 |

| Делитель частоты следования импульсов | 1987 |

|

SU1431069A1 |

| Управляемый делитель частоты следования импульсов | 1987 |

|

SU1478323A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1119176A1 |

| Делитель частоты с переменным коэффициентом деления | 1987 |

|

SU1444939A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU884152A1 |

Изобретение может использоваться в цифровой измерительной аппаратуре, в синтезаторах частот и в устройствах автоматики. Цель изобретения - повышение рабочего диапазона частот при делении на нечетные коэффициенты деления - достигается за счет введения элемента И 13, выполнения блока 6 управления в виде комбинационного сумматора и организации новых функциональных связей. Устройство также содержит счетчик 1 импульсов, дешифратор 4 скважности, дешифратор 5 кода управления, триггеры 7-9, элемент И-НЕ 10, формирователь 14 импульсов сброса, элементы И 11 и 12, входную и выходную шины 15 и 16 и шину 17 кода управления. На выходе устройства формируются симметричные выходные импульсы. 1 ил.

| Синхронный делитель частоты на 15 на @ -триггерах | 1985 |

|

SU1307585A1 |

Авторы

Даты

1990-09-30—Публикация

1988-10-10—Подача