1

Изобретение относится к электроизмерительной технике.

Известны аналого-цнфровые преобразователи, работающие но принципу параллельнопоследовательного уравновешивания.

На первом такте с номояцяо k сра1внивающих устройств и определенного числа образцовых мер весь диапазон преобразуемых сигразбивается на зону, равналов U:,,,,

fJx ную определяется зона, в которой

1

находится измеряемая величина Ux- Иа втором такте зона, в которой находится Vx, вновь

-с,.

делится на А+1 зону величиной гит. д.

(и + 1)За я тактов измеряемая величина Их онределяется как сумма образцовых мер, соответствующих определенным в каждом такте зонам с погрешностью дискретности

1

(k + 1)«

и.

В -известном устройстве для получения образцовых мер используются два одинаковых преобразователя кода в напряжение (IlKHi и ПКНз), между выходами которых включен делитель напряжения с числом выводов k, состоящий из /г-|-1 одинаковых прецизионных

сопротивлении, равных выходному сопротивлению икн.

Иаличие двух независимых ИКИ отрицательно сказывается на точности и быстродействии таких АЦП, кроме того, увеличивает объем оборудования.

Цель изобретения - повыщепие точности и быстродействия и упрощение устройства.

Предлагаемый преобразователь отличается тем, что вместо двух нреобразователей код напряжение используется один, между двумя выходами которого включен делитель напряжения с числом выводов k.

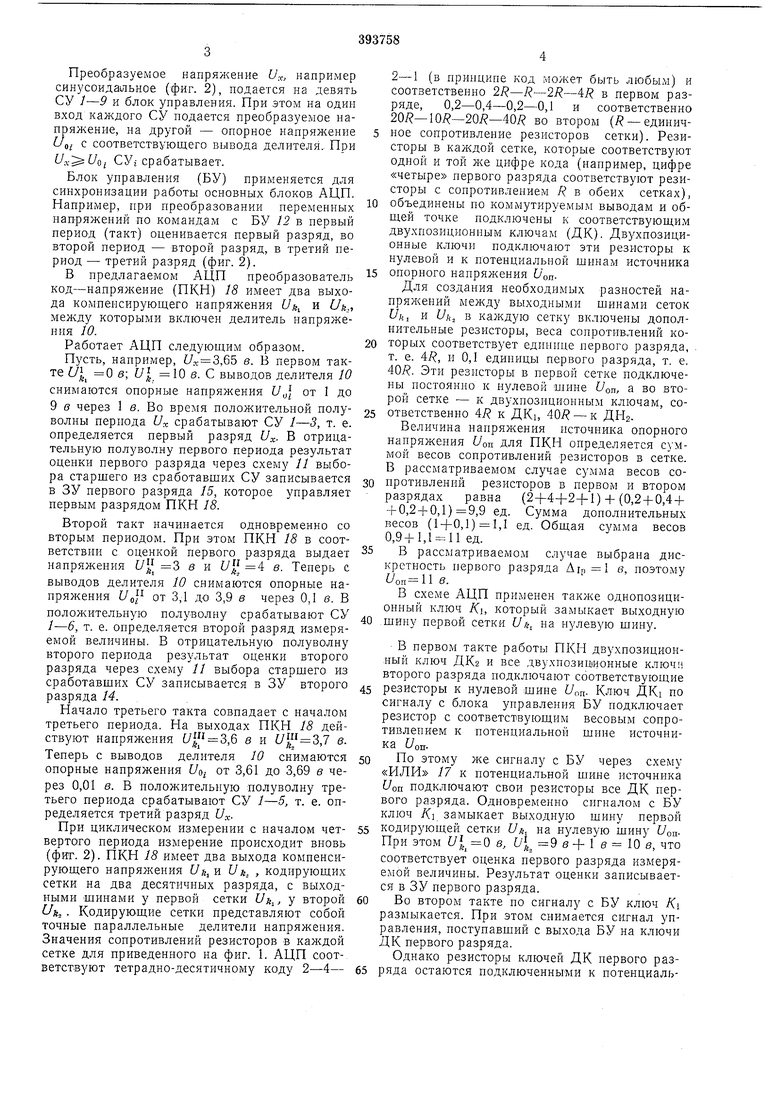

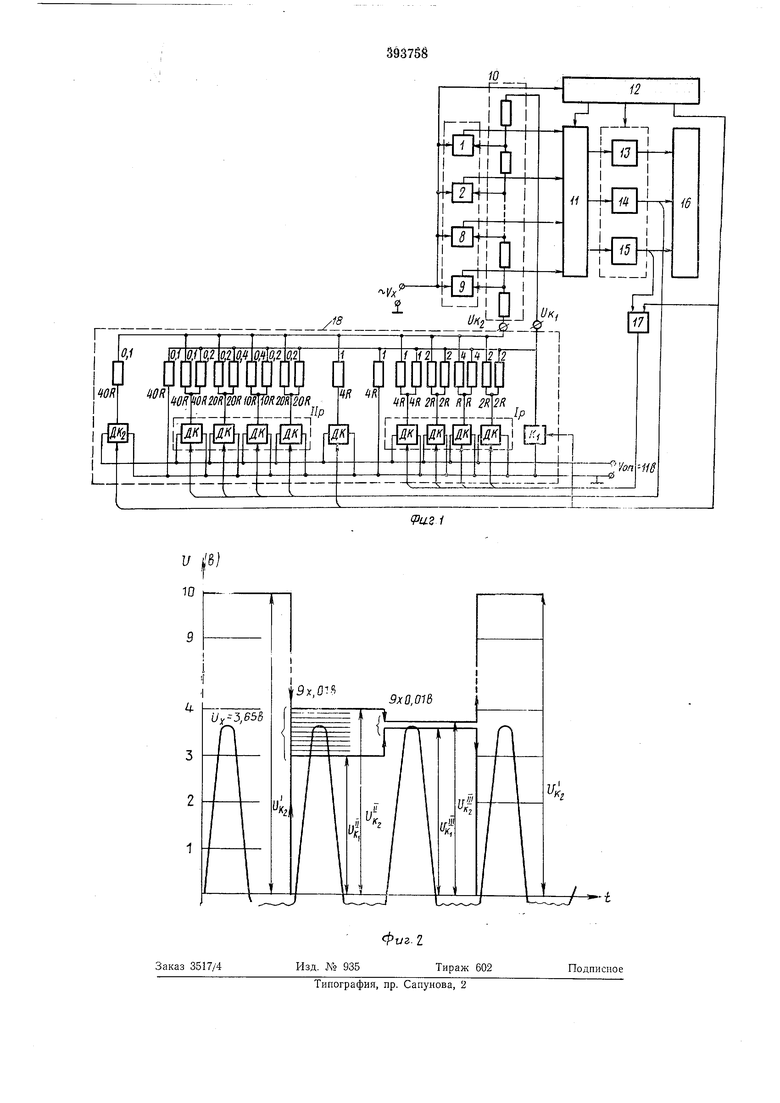

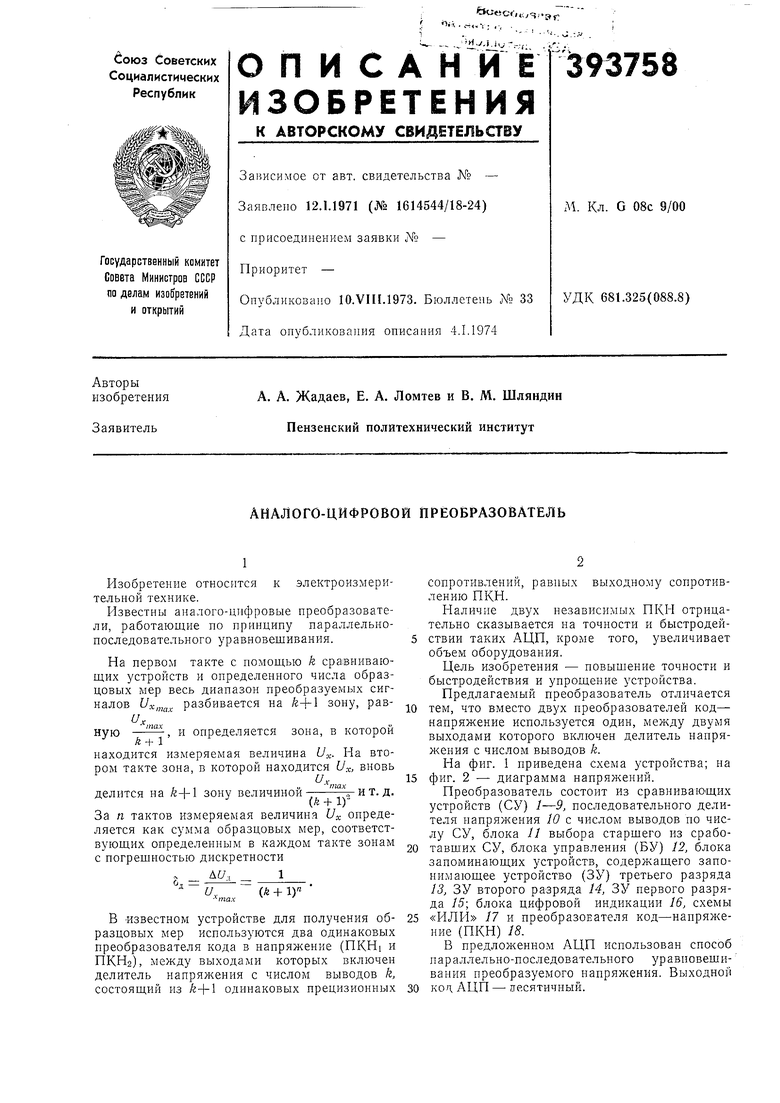

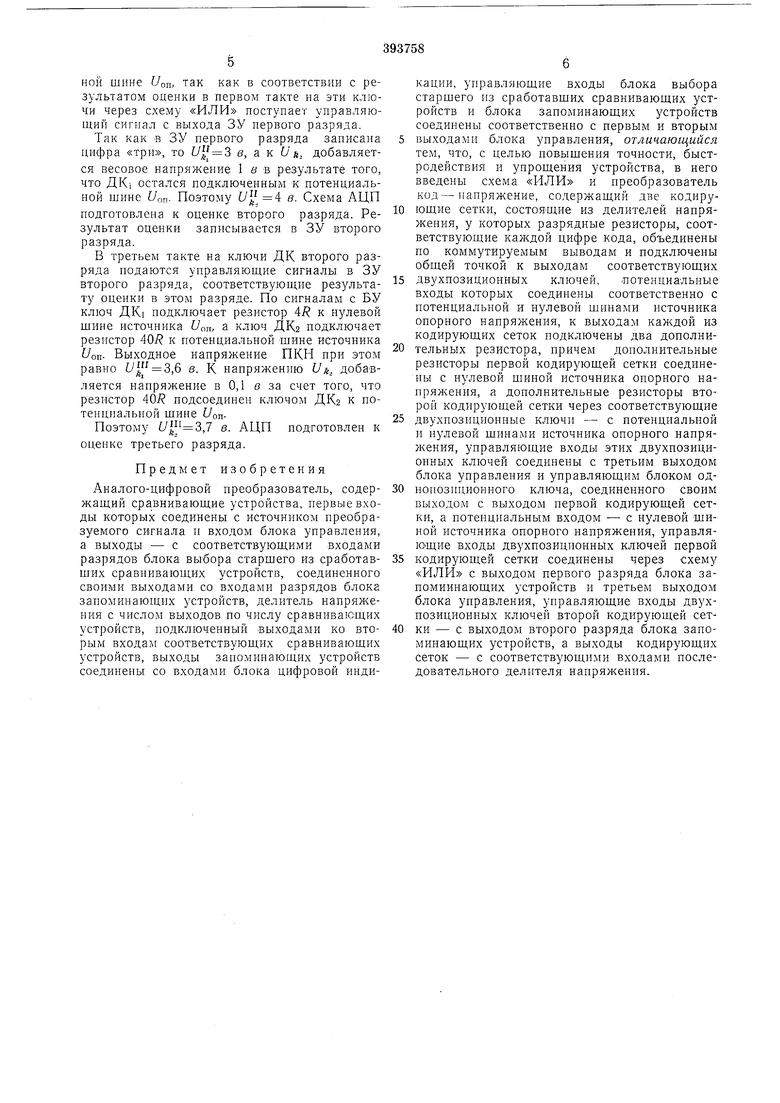

На фиг. 1 приведена схема устройства; на фиг. 2 - диаграмма напряжений.

Преобразователь состоит из сравнивающих устройств (СУ) 1-9, последовательного делителя напряжения 10 с числом выводов по числу СУ, блока // выбора старшего из сработавших СУ, блока управления (БУ) 12, блока запоминающих устройств, содержащего запонимающее устройство (ЗУ) третьего разряда 13, ЗУ второго разряда 14, ЗУ первого разряда 15; блока цифровой индикации 16, схемы «ИЛИ 17 и преобразователя код-напряжение (ПКН) 18.

В предложенном АЦП использован способ параллельно-последовательного уравповешивания преобразуемого напряжения. Выходной коп, АЦП - ггесятичный.

Преобразуемое напряжение 6.-, например синусоидашьное (фиг. 2), подается на девять СУ 1-9 и блок управления. При этом на один вход каждого СУ подается преобразуемое папряжение, на другой - опорное напряжение f/or с соответствующего вывода делителя. При СУг срабатывает.

Блок управления (БУ) применяется для синхронизации работы основных блоков АЦП. Например, при преобразовании переменных напряжений по командам с БУ 12 в первый период (такт) оценивается первый разряд, во второй период - второй разряд, в третий период - третий разряд (фиг. 2).

В предлагаемом АЦП преобразователь код-напряжение (ПКН) 18 имеет два выхода компенсирующего напрял ения Uk и Uk,, меладу которыми включен делитель напряжепия 10.

Работает АЦП следующим образом.

Пусть, например, ,65 в. В первом такте Uj 0 в; и 10 8. С выводов делителя 10 снимаются опорные напряжения U от 1 до 9 в через 1 в. Во время полол ительной полуволны периода Ux срабатывают СУ /-3, т. е. определяется первый разряд f/. В отрицательную полуволну первого периода результат оценки первого разряда через схему 11 выбора старшего из сработавших СУ записывается в ЗУ первого разряда 15, которое управляет первым разрядом ПКН 18.

Второй такт начинается одновременно со вторым периодом. При этом ПКН 18 в соответствии с оценкой первого разряда выдает напряжения t/ 3 в и И 4 в. Теперь с выводов делителя 10 снимаются опорные напряжения t/oj от 3,1 до 3,9 8 через 0,1 б. В полол ительную полуволну срабатывают СУ /-6, т. е. определяется второй разряд измеряемой величины. В отрицательную полуволну второго периода результат оценки второго разряда через схему // выбора старшего из сработавших СУ записывается в ЗУ второго разряда 14.

Начало третьего такта совпадает с началом третьего периода. На выходах ПКН 18 действуют напряжения t/| 3,6 в и 3,7 в. Теперь с выводов делителя 10 снимаются опорные напряжения С/о от 3,61 до 3,69 в через 0,01 8. В полол ительную полуволну третьего периода срабатывают СУ /-5, т. е. определяется третий разряд U.

При циклическом измерепии с началом четвертого периода измерение происходит вновь (фиг. 2). ПКН 18 имеет два выхода компенсирующего напряжения f7ft, и /4, , кодируюших сетки на два десятичных разряда, с выходными шинами у первой сетки Uk, У второй t/jj . Кодирующие сетки представляют собой точные параллельные делители напряжения. Значения сопротивлений резисторов в каладой сетке для приведенного на фиг. 1. АЦП соответствуют тетрадно-десятичному коду 2-4-

2-1 (в принципе код может быть любььм) и соответственно 2R-R-2R-4/ в первом разряде, 0,2-0,4-0,2-0,1 и соответственно во втором (/ -единичное сопротивление резисторов сетки). Резисторы в сетке, которые соответствуют одной и той цифре кода (например, цифре «четыре первого разряда соответствуют резисторы с сопротивлением R в обеих сетках),

объединены по коммутируемым выводам и общей точке подключены к соответствующим двухпозиционпым ключам (ДК). Двухпозиционные ключи подключают эти резисторы к нулевой и к потенциальной шинам источника

опорного напряжения DonДля создания необходимых разностей напрял ений между выходными шинами сеток /и, и и hi в сетку включены дополнительные резисторы, веса сопротивлений которых соответствует единице первого разряда, т. е. 4/, и 0,1 едипрщы первого разряда, т. е. 40/. Эти резисторы в первой сетке подключены постоянно к нулевой шине и, а во второй сетке - к двухпозиционным ключам, соответственно 4/ к ДКь 40/ - к ДН2.

Величина напрял ения источника опорного напряжения боп для определяется суммой весов сопротивлений резисторов в сетке. В рассматриваемом случае сумма весов сопротивлении резисторов в первом и втором разрядах равна (2+4-f 2+1) + (0,2 + 0,4-Ь + 0,2 + 0,1) 9,9 ед. Сумма дополнительных весов (1+0,1) 1,1 ед. Общая сумма весов 0,9+1,1 11 ед.

В рассматриваемом случае выбрана дискретность первого разряда 0, поэтому

в.

В схеме АЦП применен однопозиционный ключ Ki, который замыкает выходную шину первой сетки Uп на нулевую шину.

В первом такте работы ПКН двухпозиционный ключ ДК2 и все двухпозицйонные второго разряда подключают соответствующие резисторы к нулевой шипе f/on- Ключ ДК: по сигналу с блока управления БУ подключает резистор с соответствующим весовым сопротивлением к потенциальной шине источника t/onПо этому Лсе сигналу с БУ через схему «ИЛИ 17 к потенциальной щине источника Uon подключают свои резисторы все ДК первого разряда. Одповременно сигналом с БУ ключ /С замыкает выходную шину первой

кодирующей сетки f/д, на нулевую шину t/onПри этом б 0 8, L/ 9 8 + 1 0 10 8, что соответствует оценка первого разряда измеряемой величины. Результат оценки записывается в ЗУ первого разряда.

Во втором такте по сигналу с БУ ключ /(i размыкается. При этом снимается сигнал управления, поступавщий с выхода БУ на ключи ДК первого разряда. Однако резисторы ключей ДК первого разряда остаются подключенными к потенциальной шине Uon, так как в соответствии с результатом оценки в первом такте на эти ключи через схему «ИЛИ поступает управляющий сигнал с выхода ЗУ первого разряда.

Так как в ЗУ первого разряда записана цифра «три, то 3 в, а к U ь, добавляется весовое напряжение 1 в в результате того, что ДК1 остался подключенным к потенциальной шине Lon. Поэтому О 4 в. Схема АЦП подготовлена к оценке второго разряда. Результат оценки записывается в ЗУ второго разряда.

В третьем такте на ключи ДК второго разряда подаются управляющие сигналы в ЗУ второго разряда, соответствующие результату оценки в этом разряде. По сигналам с БУ ключ ДК1 подключает резистор 4 к нулевой шине источника Uf, а ключ ДК2 подключает резистор 40/ к потенциальной шине источника t/on- Выходное напряжение ПКП при этом равно 3,6 в. К напряжению Vk., добавляется напряжение в 0,1 в за счет того, что резистор 40/ подсоединен ключом ДК2 к потенцпальной щине f/onПоэтому ,7 8. АЦП подготовлен к оценке третьего разряда.

Предмет изобретения

Аналого-цифровой цреобразователь, содержащий сравнивающие устройства, иервые входы которых соединены с источником преобразуемого сигнала ц входом блока управления, а выходы - с соответствующими входами разрядов блока выбора старшего из сработавщих сравнивающих устройств, соединенного своими выходами со входами разрядов блока запоминающих устройств, делитель напряжения с числом выходов по числу сравнивающих устройств, подключенный выходами ко вторым входам соответствующих сравнивающих устройств, выходы запоминающих устройств соединены со входами блока цифровой индикации, управляющие входы блока выбора старщего из сработавших сравнивающих устройств и блока запоминающих устройств соединены соответственно с первым и вторым выходами блока управления, отличающийся тем, что, с целью повышения точности, быстродействия и упрощения устройства, в него введены схема «ИЛИ и преобразователь код - напряжение, содержащий две кодирующие сетки, состоящие из делителей напряжения, у которых разрядные резисторы, соответствующие каждой цифре кода, объединены по коммутируемым выводам и подключены общей точкой к выходам соответствующих

двухпозиционных ключей, -потенциальные входы которых соединены соответственно с потенциальной и нулевой шинами источника опорного напряжения, к выходам каждой из кодирующих сеток подключены два дополнительных резистора, причем дополнительные резисторы первой кодирующей сетки соединены с нулевой тиной источника опорного напряжения, а дополнительные резисторы второй кодирующей сетки через соответствующие

двухпозиционные ключи - с потенциальной и нулевой щинами источника опорного напряжения, управляющие входы этих двухпозиционных ключей соединены с третьим выходом блока управления и управляющим блоком однопозиционного ключа, соединенного своим выходом с выходом первой кодирующей сетки, а потепциальным входом - с нулевой шиной источника опорного напряжения, управляющие входы двухпозиционных ключей первой

кодирующей сетки соединены через схему «ИЛИ с выходом первого разряда блока запомиинающих устройств и третьем выходом блока управления, управляющие входы двухпозициоиных ключей второй кодирующей сетки - с выходом второго разряда блока запоминающих устройств, а выходы кодирующих сеток - с соответствующими входами последовательного делителя напрялсенпя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ контроля аналого-цифровых преобразователей | 1976 |

|

SU708506A1 |

| Двухканальный аналого-цифровой преобразователь | 1981 |

|

SU995314A1 |

| Устройство для измерения функции распределения случайной погрешности аналого-цифровых преобразователей | 1984 |

|

SU1246370A1 |

| Преобразователь угловых перемещений в код | 1976 |

|

SU641480A1 |

| Способ определения степени успокоения электромеханического преобразователя и устройство для его осуществления | 1988 |

|

SU1721568A1 |

| АНАЛОГО-ЦИФРОВОЕ ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU368615A1 |

| Многоканальный преобразователь кода в напряжение | 1973 |

|

SU660233A1 |

| Устройство для аналого-цифрового преобразования | 1988 |

|

SU1608796A1 |

| Преобразователь напряжение-код сКОНТРОлЕМ | 1979 |

|

SU822342A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU1005305A1 |

Авторы

Даты

1973-01-01—Публикация