1

Изобретение относится к вычислительной технике, в частности к преобразованию кодов в напряжение в цифровых управляющих системах.

Известен многоканальный преобразователь, содержащий счетчик адреса, аналоговое запоминающее устройство, преобразователь кода в напряжение, дещифратор н коммутационный блок 1.

Недостатком его является отсутствие автоматического контроля за процессом преобразования по всем каналам.

Известен многоканальный преобразователь кода в напряжение (МПКН), содержащий нреобразователь кода в напряжение, связанный с входным регистром и аналоговым запомина1ОП1,им устройством, счетчнк адреса, соединенный с генератором импульсов, щинами кода адреса и дешифратором, связанным с аналоговым запоминающим устройством, а также триггер запрета, единичный вход которого подключен на (ян-1)-ю из щин входного кода, а единичный выход триггера запрета связан с дешифратором, при этом входной регистр подключен к щинам входного кода, генератор импульсов соединен с шиной запросов кода числа н нулевым входом триггера запрета, аналоговое запоминающее устройство связано с шннами выходных напряжений 2.

Недостатком известных многоканальных преобразователей кода в напряжение является невозможность контроля преобразователя в процессе его работы с локализацией

места неисправности.

Целью изобретения является обеспечение возможности автоматического контроля преобразователя без его отключения от нотребнтелей нреобразуемых напряжений,

уменьшенне времени контроля н локализации меета неисправности.

Цель достигается тем, что в многоканальный нреобразователь кода в напряжение, содержапи1Й нреобразователь кода в напряжение, соединенный с входным регистром и аналоговым запоминающим устройством, счетчик адреса, соединенный с генератором импульсов, тинами кода адреса и ден1ифратором, соединенным с аналоговым

запоминающим устройством, триггер запрета, единичный вход которого подключен (п+1)-н шине входного кода, а единичный выход триггера запрета связан с дешифратором, входной регистр подключен к шинам

Г)Ходного кода, второй выход генератора импульсов соединен с шиной запросов кода числа и нулевым входом триггера запрета, а аналоговое заноминающее устройство связано с щинами выходных напряжений,

введены цифровой и аналоговый сумматоры, регистр суммы, элементы считывания и сравнения кодов, преобразователь напряжение - код и два ключа, при этом п шин входного кода связаны с первыми входами цифрового сумматора, а (т + п) выходов последнего через регистр суммы соединены со вторыми входами цифрового сумматора, п последних выходов регистра суммы через элемент считывания кода связаны с элементом сравнения кодов, выходы которого подключены к шинам обш,его и вспомогательного сигналов неиснравности, выходы аналогового запоминаюш;его устройства через аналоговый сумматор и первый ключ соединены с входом преобразователя напряжение - код, выходы которого связаны с элементом сравнения кодов, т-я выходная шина дешифратора соединена с первым ключом, элементом сравнения кодов и элементом считывания кодов, а (т+)-я шина дешифратора соединена со вторым ключом, элементом сравнения кодов, регистром суммы, входным регистром и цифровым сумматором, нри этом выход преобразователя кода в напряжение соединен с другим выходом второго ключа.

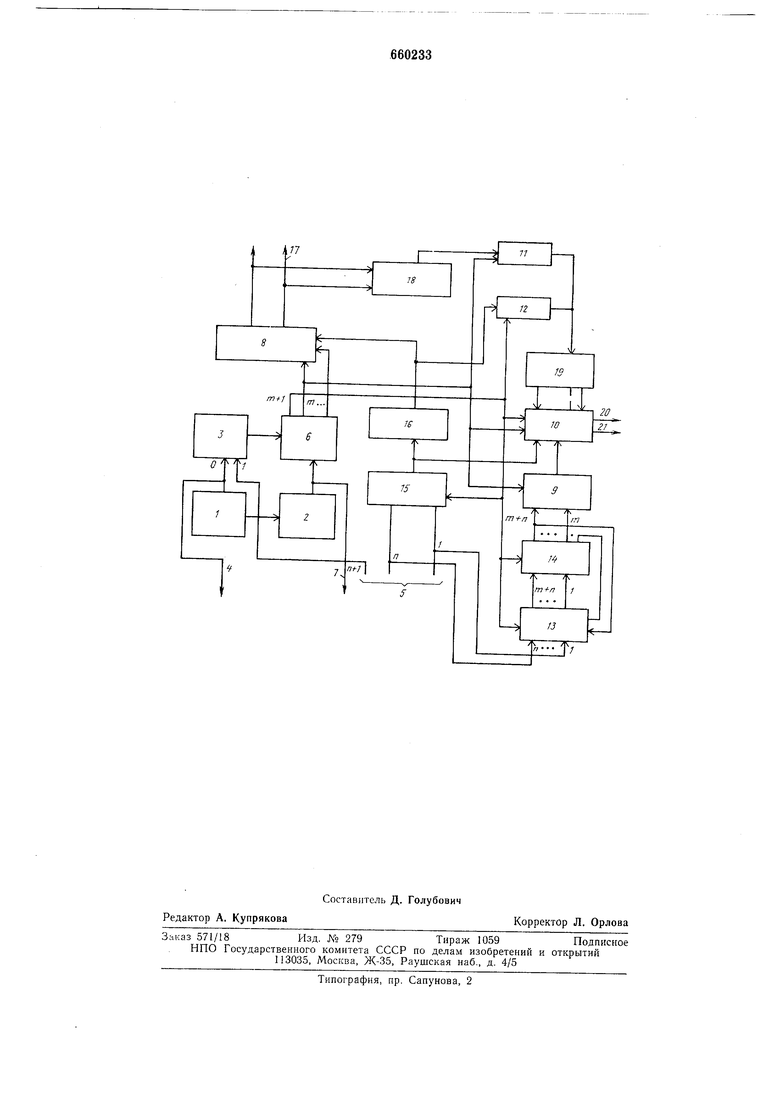

Структурная схема многоканального преобразователя, показана на чертеже.

Генератор 1 импульсов одним выходом соединен со счетчиком 2 адреса, а вторым выходом - с нулевым входом триггера 3 запрета и шиной 4 запроса кода числа. Единичный вход триггера 3 соединен с {/г-|-1)-й из шин 5 входного кода, а нулевой выход триггера 3 - со входом дешифратора 6. Счетчик 2 адреса связан с дешифратором 6 и шииами 7 кода адреса, т выходных шин дешифратора 6 подсоединены к аналоговому заноминаюшему устройству (ЗУ) 8, причем /п-я шина дешифратора 6 соединена с элементом 9 считывания кодов, элементом 10 сравнения кодов и первым ключом 11, а (т+1)-я выходная шина дешифратора 6 соединена со вторым ключом 12, цифровым сумматорам 13 и регистром 14 суммы. Шины 5 входного кода соединены с входным регистром 15, связанным с преобразователем 16 кода в напряжение (ПКН), выход которого соединен с аналоговым запоминающим устройством 8. Аналоговое запоминающее устройство 8 через шины 17 выходных напряжений соединено с аналоговым сумматором 18, выход которого связан с ключом 11. Выход ПКН 16 соединен с ключом 12, выходы ключей 11 и 12 объединены и связаны с преобразователем 19 напряжения в код (ПНК) 19, выходы которого связаны с элементом 10 сравнения кодов, соединенным по выходу с шинами общего сигнала неисправности (ОСН) 20 и вспомогательного сигнала неисправности (ВСП) 21; п первых шин 5 входного кода соединены через цифровой сумматор 13 с региетром 14 еуммы, все выходы которого связаны с цифровым сумматором 13, а т последних через элемент 9 считывания кода подключены к элементу 10 сравнения кодов.

Преобразователь работает следующим образом.

По сигналу с генератора 1 импульсов формируется сигнал на шине 4 занроса кода числа и сигнал запрета дешифрации адреса. Одновременно импульсом с генератора 1 импульсов счетчик 2 адреса формирует код адреса на шинах 7 кода адреса, который пока не дешифрируется, так как есть сигнал запрета. выдачи сигналов на шинах 4 и 7 на щины 5 входного кода поступает преобразуемый код, причем на п шин поступают информационные разряды кода, а не (л+1)-ю шину всегда поступает единичный код, который снимает сигнал запрета с трнггера 3, при этом дешифратор 6 включает канал аналогового запоминаюН1,его устройства 8. Код, ностунивший на входной регистр 15, преобразуется в напряжение на нреобразователе 16 кода в напряжение. Это выходное напряжение поступает на канал аналогового запоминающего устройства 8, номер которого определяется возбужденным выходом дешифратора 6. С выхода аналогового ЗУ 8 напряжение поступает на одну из шин 17 выходного напряжения и одновременно на вход аналогового сумматора 18. Кроме того, входной преобразуемый код поступает па цифровой сумматор 13, с которого он носле суммирования с содержимым регистра 14 суммы опять же через регистр суммы поступает на вход элемента 9 считывания кода. Такой процесс продолжается при преобразовании по каждому из т каналов. При этом осуществляется аналоговое суммирование выходных нанряжений, соответствующих преобразуемым кодам и цифровое суммирование этих кодов па цифровом сумматоре 13 и регистре 14 суммы. После т тактовых импульсов с генератора I с выхода аналогового сумматора 18 будет снято среднее значение т преобразуемых нанряжений, а с регистра - п старших разрядов суммы преобразуемых кодов. По сигналу с /п-ой шины дешифратора будет открыт ключ 11, и на вход ПНК 19 поступит среднее значение преобразуемых напряжений, которое будет преобразовано на ПНК 19 в код. Затем одновременно выходной код ПНК 19 и выходной код регистра 14 суммы через элемент 9 считывания кодов поступят на вход элемента 10 сравнения кодов. При несовпадении этих кодов будет сформирован общий сигнал неиснравности на щине 20.

Для локализации неиснравности ПКН 16 производится проверка по (m-f 1)-му каналу. В этом случае выходное напряжение ПКН 16, соответствующее (т-1-1)-му каналу поступает через ключ 12 на вход ПНК

19, который преобразует это напряжение в

код. Одновременно по сигналу с (/п + 1)-й шнны дешифратора 6 будет произведено считывание кода входного регистра 15 в элемент 10 сравнения кодов, после чего будет произведено сравнение выходного кода ПНК 19 и кода, записанного во входном регистре 15.

При несовпадении этих кодов элемент 10 сравнения кодов формирует вспомогательный сигнал неисправности на шипе 21. По сигналу на (т+1)-м выходе дешифратора происходит обнуление цифрового сумматора 13 и регистра 14 суммы.

Формула изобретения

Многоканальный преобразователь кода в напряжение, содержаший преобразователь кода в напряжение, соединенный с входным регистром и аналоговым запоминаюш,им устройством, счетчик адреса, соединенный с генератором импульсов, шинамп кода адреса и дешифратором, соединенным с аналоговым запоминаюш,им устройством, триггер запрета, единичный вход которого подключен к (п+)-й шипе входного кода, а единичный выход триггера запрета связан с дешифратором, входной регистр подключен к шипам входного кода, второй выход генератора импульсов соединен с шиной запроса кода числа и пулевым входом триггера запрета, аналоговое запоминаюшее устройство связано с шинами выходных напряжений, отличающееся тем, что, с целью обеспечения возможности автоматического контроля преобразователя, снижепия времени контроля и локализации

места неисправности, в него введены цифровой и аналоговый сумматоры, регистр суммы, элементы считывания и сравнения кодов, преобразователь напряжение - код и два ключа, при этом п шин входного кода связаны с первыми входами цифрового сумматора, а (т+п) выходов последнего через регистр суммы соединены со вторыми входами цифрового сумматора, л последних выходов регистра суммы через элемент считывания кода связаны с элементом сравнения кодов, выходы которого подключены к шинам общего и вспомогательного сигналов неисправпости, выходы anavioroBOго запоминающего устройства через аналоговый сумматор и первый ключ соедипепы с входом преобразователя напряжения в код, выходы которого связаны с элементом сравнения кодов, ш-я выходная шина дешифратора соединена с первым ключом, элементом сравнения кодов и элементом считывания кодов, а (т+1)-я шина дешифратора соединена со вторым ключом, элементом сравнения кодов, регистром суммы,

входным регистром и цифровым сумматором, при этом выход преобразователя кода в напряжение соединен с другим входом второго ключа.

Источники информации,

принятые во внимание при экспертизе

1. Смолев В. Б. Полупроводниковые кодирующие п декодирующие преобразователи напряжения. М., «Энергия, 1967, рис. 6-8.

2. Гитис Э. И. Преобразователи информации для электронных вычислительных устройств. М., «Энергия, 1970, рис. 5-11.

20

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный преобразователь кода в напряжение | 1985 |

|

SU1279071A1 |

| Многоканальный преобразователь напряжения в код | 1975 |

|

SU656203A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Адаптивный коммутатор системы телеизмерений | 1980 |

|

SU886032A1 |

| Преобразователь кода во временной интервал | 1985 |

|

SU1300637A1 |

| ТАНКОВЫЙ БАЛЛИСТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 1987 |

|

RU2226715C2 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Запоминающее устройство | 1980 |

|

SU894789A1 |

| Устройство для передачи телеметрической информации | 1986 |

|

SU1336077A1 |

| Устройство для сопряжения ЦВМ с магнитофоном | 1985 |

|

SU1317445A1 |

Авторы

Даты

1979-04-30—Публикация

1973-07-30—Подача