Изобретение ртносится к автоматике и вы1ислительной технике и может быть использовано дяя преобразования быстроиз- меияющихся аналоговых сигналов в цифровой код. .

Цель изобретения - повышение быстродейния

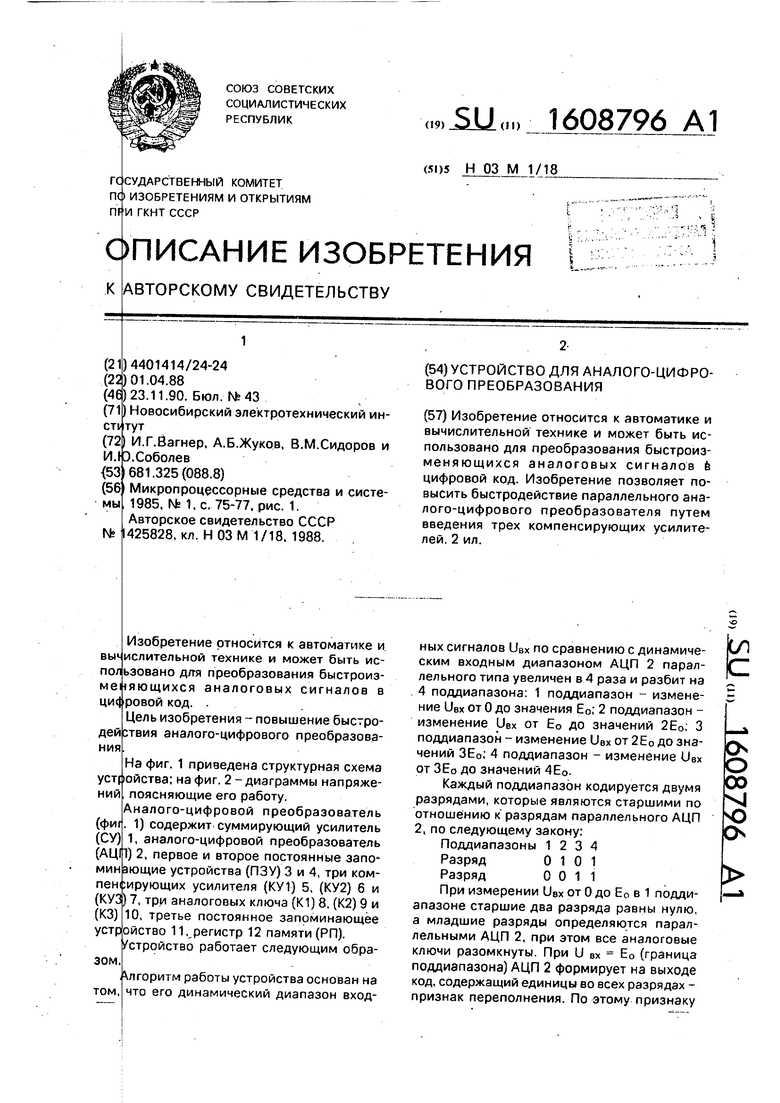

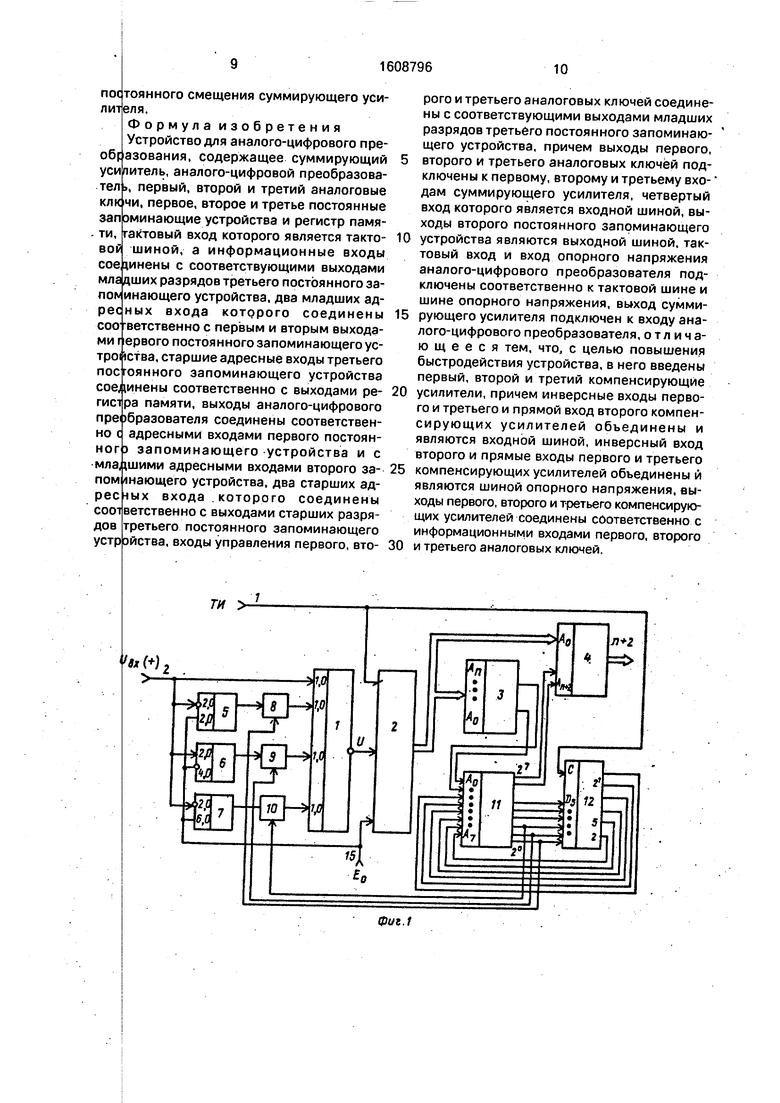

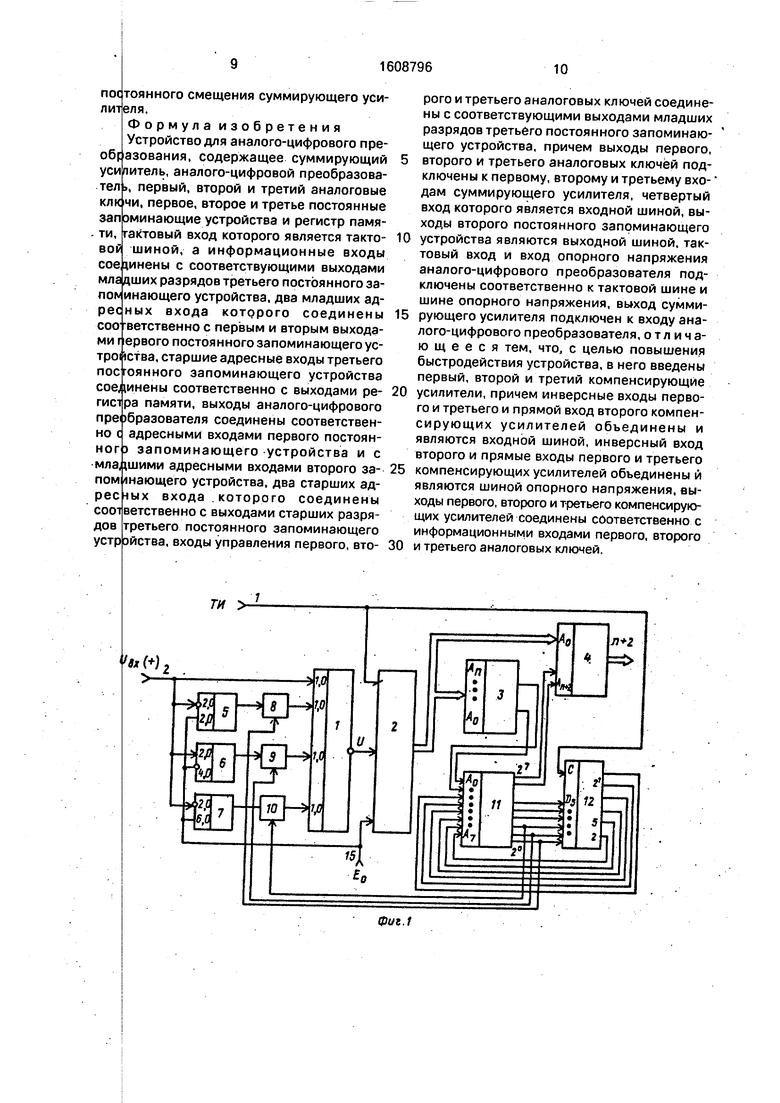

ствия аналого-цифрового преобразована фиг. 1 приведена структурная схема юйства; на фиг, 2 - диаграммы напряже- , поясняющие его работу. Аналого-цифровой преобразователь 1) содержит суммирующий усилитель 1, аналого-цифровой преобразователь 1) 2, первое и второе постоянные запо- эющие устройства (ПЗУ) 3 и 4, три ком- :ирующих усилителя (КУ1) 5, (КУ2) 6 и ) 7. три аналоговых ключа (К1) 8, (К2) 9 и 10, третье постоянное запоминающее

том.

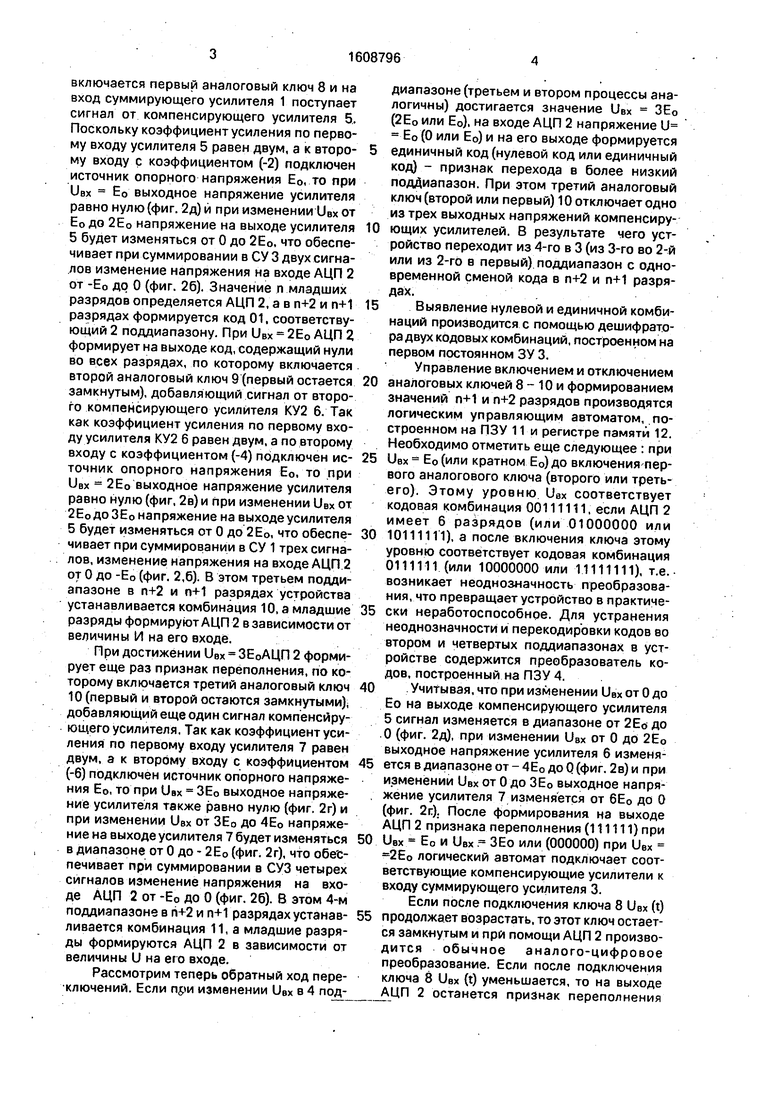

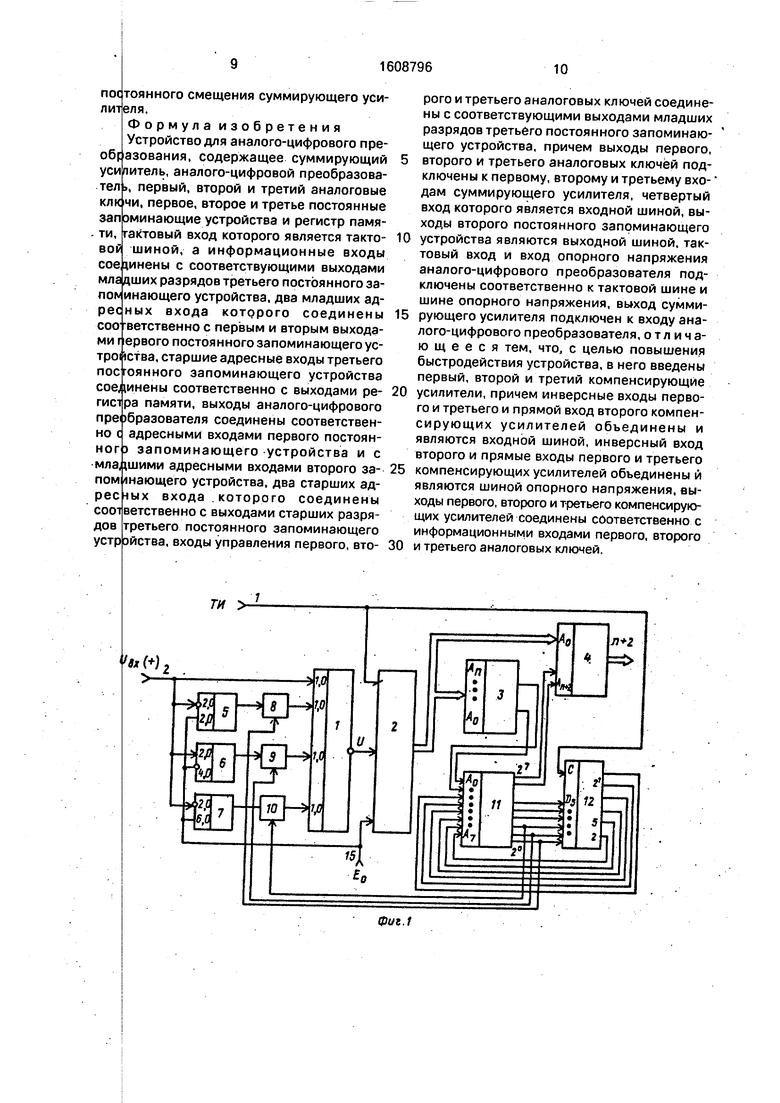

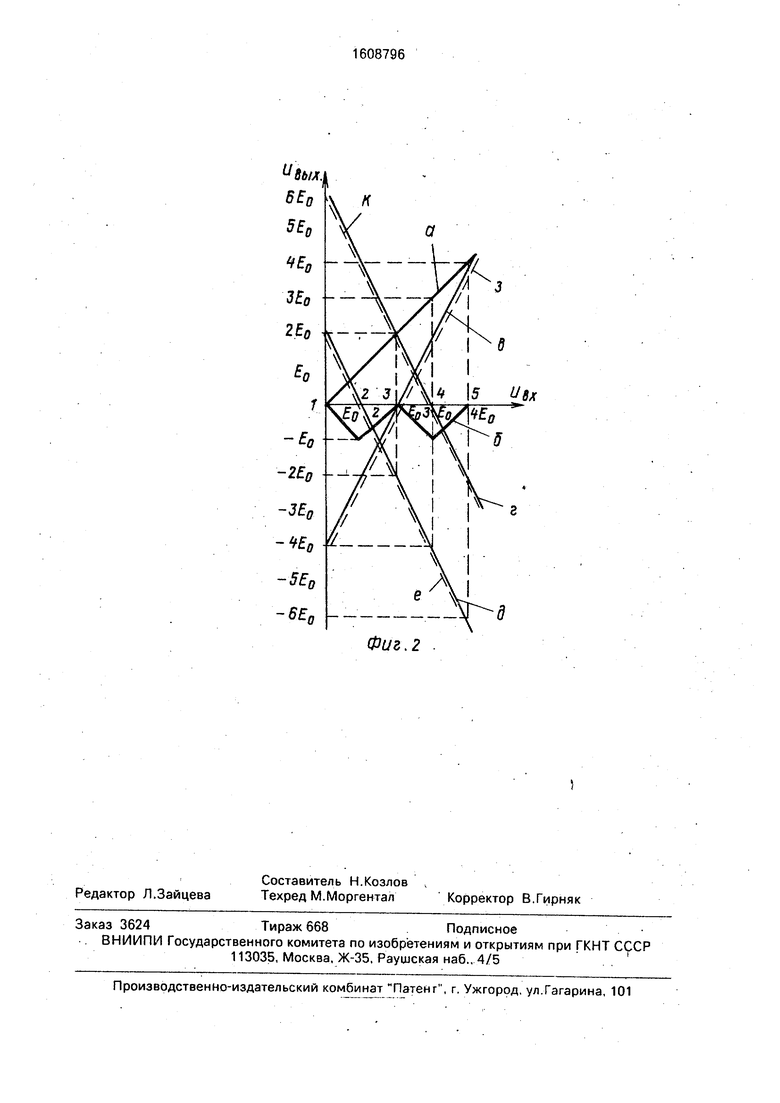

лгоритм работы устройства основан на что его динамический диапазон входных сигналов UBX по сравнению с динамическим входным диапазоном АЦП 2 параллельного типа увеличен в 4 раза и разбит на 4 поддиапазона: 1 поддиапазон - изменение UBX от О до значения Ео; 2 поддиапазон - изменение UBX от Ео до значений 2Ео; 3 поддиапазон - изменение Uex от 2Ео до значений ЗЕо; 4 поддиапазон - изменение Uex от ЗЕо до значений 4Ео.

Каждый поддиапазон кодируется двумя разрядами, которые являются старшими по отношению к разрядам параллельного АЦП 2 по следующему закону: Поддиапазоны 1234 Разряд0101

Разряд0011

При измерении UBX от О до Ео в 1 поддиапазоне старшие два разряда равны нулю, а младшие разряды определяются параллельными АЦП 2, при этом все аналоговые ключи разомкнуты. При U вх Ео (граница поддиапазона) АЦП 2 формирует на выходе код, содержащий единицы во всех разрядах - признак переполнения. По этому признаку

Qs О 00 vl Ю

ON

включается первый аналоговый ключ 8 и на вход суммирующего усилителя 1 поступает сигнал от компенсирующего усилителя 5. Поскольку коэффициент усиления по первому входу усилителя 5 равен двум, а к второ- му входу с коэффициентом (-2) подключен источник опорного напряжения Ео, то при UBX ЕО выходное напряжение усилителя равно нулю (фиг. 2д) и при изменении UBX от ЕО до 2Ео напряжение на выходе усилителя 5 будет изменяться от О до 2Ео. что обеспечивает при суммировании в СУ 3 двух сигна- .лов изменение напряжения на входе АЦП 2 от -ЕО до О (фиг. 26). Значение л младших разрядов определяется АЦП 2. а в п+2 и п+1 разрядах формируется код 01, соответствующий 2 поддиапазону. При UBX 2Ео АЦП 2, формирует на выходе код, содержащий нули во всех разрядах, по которому включается второй аналоговый ключ 9 (первый остается замкнутым), добавляющий сигнал от второго компенсирующего усилителя КУ2 6. Так как коэффициент усиления по первому входу усилителя КУ2 6 равен двум, а по второму входу с коэффициентом (-4) подключен ис- точник опорного напряжения Ео, то при UBX 2ЕО выходное напряжение усилителя равно нулю (фиг, 2в) и при изменении UBX от 2Ео до ЗЕо напряжение на выходе усилителя 5 будет изменяться от О до 2Ео, что обеспе- чивает при суммировании в СУ 1 трех сигналов, изменение напряжения на входе АЦП 2 от О до -ЕО (фиг. 2,6). В этом третьем поддиапазоне в п+2 и п+1 разрядах устройства устанавливается комбинация 10, а младшие

разряды формируют АЦП 2 в зависимости от величины И на его входе.

При достижении UBX ЗЕоАЦП 2 формирует еще раз признак переполнения, по которому включается третий аналоговый ключ 10 (первый и второй остаются замкнутыми); добавляющий еще один сигнал компенсирующего усилителя. Так как коэффициент усиления по первому входу усилителя 7 равен двум, а к второму входу с коэффициентом (-6) подключен источник опорного напряже- ния ЕО, то при UBX ЗЕо выходное напряжение усилителя также равно нулю (фиг. 2г) и при изменении UBX от ЗЕо до 4Ео напряжение на выходе усилителя 7 будет изменяться в диапазоне от О до - 2Ео (фиг. 2г), что обеспечивает при суммировании в СУЗ четырех сигналов изменение напряжения на входе АЦП 2 от -ЕО до О (фиг. 26). В этом 4-м поддиапазоне в h+2 и п+1 разрядах устанав- ливается комбинация 11, а младшие разряды формируются АЦП 2 в зависимости от величины и на его входе.

Рассмотрим теперь обратный ход пере- ключений. Если при изменении UBX в 4 поддиапазоне (третьем и втором процессы аналогичны) достигается значение UBX ЗЕо ЕО или ЕО), на входе АЦП 2 напряжение U ЕО (О или ЕО) и на его выходе формируется единичный код (нулевой код или единичный код) - признак перехода в более низкий поддиапазон. При этом третий аналоговый ключ (второй или первый) 10 отключает одно из трех выходных напряжений компенсирующих усилителей. В результате чего устройство переходит из 4-го в 3 (из 3-го во 2-й или из 2-го в первый) поддиапазон с одновременной сменой кода в п+2 и п+1 разрядах.

Выявление нулевой и единичной комбинаций производится с помощью дешифратора двух кодовых комбинаций, построенном на первом постоянном ЗУ 3.

Управление включением и отключением аналоговых ключей 8 - 10 и формированием значений п+1 и п+2 разрядов производятся логическим управляющим автоматом, построенном на ПЗУ 11 и регистре памяти 12. Необходимо отметить еще следующее : при UBX - ЕО (или кратном ЕО) до включения-первого аналогового ключа (второго или третьего). Этому уровню Uax соответствует кодовая комбинация 00111111. если АЦП 2 имеет 6 разрядов (или 01000000 или 10111111), а после включения ключа этому уровню соответствует кодовая комбинация 0111111 (или 10000000 или 11111111), т.е.- возникает неоднозначность преобразования, что превращает устройство в практически неработоспособное. Для устранения неоднозначности и перекодировки кодов во втором и четвертых поддиапазонах в устройстве содержится преобразователь кодов, построенный на ПЗУ 4.

Учитывая, что при изменении UBX от О до ЕО на выходе компенсирующего усилителя 5 сигнал изменяется в диапазоне от 2Ео до О (фиг. 2д), при изменении UBX от О до 2Ео выходное напряжение усилителя 6 изменяется в диапазоне от - 4ЕО до О (фиг. 2в) и при изменении UBX от О до ЗЕо выходное напряжение усилителя 7 изменяется от 6Ео до О (фиг. 2г). После формирования на выходе АЦП 2 признака переполнения (111111) при UBX ЕО и UBX ЗЕо или (000000) при UBX -2Ео логический автомат подключает соответствующие компенсирующие усилители к входу суммирующего усилителя 3.

Если после подключения ключа 8 UBX (t) продолжает возрастать, то этот ключ остается замкнутым и при помощи АЦП 2 производится обычное аналого-цифровое преобразование. Если после подключения ключа 8 UBX (t) уменьшается, то на выходе АЦП 2 останется признак переполнения

(1нево

HV

вo

Г

111). Это приводит к тому, что ключ 8 не от (лючается и устройство в целом будет не работоспособным, так как его выходной код будет соответствовать входной аналого- величине UexW. Для нормального функ- онирования устройства введено дополнительное смещение (не показано) ипенсирующих усилителей 5-7 так, что- при UBX . Ео (2Ео или ЗЕо) выходное на 1 ряжение усилителей 5-7 отличалось от ювого (фиг. 2е. з, к). Достаточно для норма пьной работы устройства, чтобы сигнал входе АЦП 2 после подключения компенсирующего усилителя изменился на один преобразования по уровню, при этом одной код АЦП 2 в момент UBX Ео (2Ео. )) и подключенных компенсирующих уси- елях 5-7 примет значения 111110 (000001, 111110). Данное смещение можно юлнить баллансом нуля операционных ус1 лителей. на которых реализованы компенсирующие усилители 5 - 7. В исходном состоянии (установка в О не показана) ана- овые ключи 8-10 закрыты. На вход уст- 1ства поступает сигнал UBx(t) (фиг. 2а). 1 помощи тактовых импульсов, поступающих по тактовой шине, задается шаг дискретизации аналого-цифрового преобразования времени. Параллельный АЦП 2 обеспе- преобразование входного сигнала в в динамическом диапазоне от О до -Ео. UBX ЕО входной сигнал достигает гра- ы динамического диапазона АЦП 2 и на выходных шинах формируются сигналы уровня логической 1. Выходной код 2 является адресным кодом для ПЗУ 3. наличии на адресных шинах ПЗУ 3 еди-. 1ОЙ кодовой комбинации производится ывание комбинации 10, которая изме- адресный код ПЗУ 11. На адресных X третьего- ПЗУ 11 устанавливается 00000010 и производится считывамие цанного ПЗУ кодовой комбинации 0000001. Сигнал уровня логической 1, ни лаемый с младшего разряда ПЗУ 11, ывает первый аналоговый ключ 8, при омрщи которого производится подключе- компенсирующего усилителя 5 к входу ум| пирующего усилителя 1. Кроме того, код -и младших разрядов (ПЗУ 11 по за- нег)1у фронту тактового импульса записы- в регистр 12 памяти. Регистр 12 1ТИ введен в схему устройства для усранения гонок, возникающих в ПЗУ 11 :мене адресного кода. Код, записаннь |й истр 12 памяти (000001), поступает на дресные шины третьего ПЗУ 11. На адрес- шинах ПЗУ 11 устанавливается новая одовая комбинация 00000110. Из ПЗУ 11 р01 зводится считывание кодовой комбилоговые

pot

Пр

по

чив|ает ко/1 При

НИ1

все его I

АЦП

Пр1/

ничиой

чи

яег

инах

од

з

нации, соответствующей двоичному коду 00001001. Состояние ключей не изменяется. После подключения компенсирующего усилителя выходной код параллельного АЦП 2 5 через один такт преобразования отличается от единичного кода. Соответственно выходной код ПЗУ 3 становится равным 00. а адресный код ПЗУ 11 - 00100100. По этому адресу из ПЗУ 11 считывается комбинация, 10 соответствующая коду 010100001 в двоичной системе счисления. Полученный код записывается в регистр 12 памяти. На его выходе устанавливается код 010001, а адресных входах ПЗУ 11 - код 01000100. По 15 этому адресу считывается комбинация, соответствующая коду 01010001. Состояние ключей не меняется, так как в младшем paai- ряде кода присутствует 1. Уровень логической 1 в седьмом разряде выходного кода 0 ПЗУ 11 участвует в формировании окончательного выходного кода устройства при помощи ПЗУ 4. ПЗУ 4 введено в схему АЦП для устранения неоднозначности аналого-цифрового преобразования, так как в результа- 5 те преобразования в моменты подключения компенсирующего усилителя на границах поддиапазонов возникают кодовые комбинации 00111111 и 01111111, а также ПЗУ 4 осуществляет перекодировку кодов: параллельного АЦП 2 и двух старших выходных разрядов ПЗУ 11.

0

В промежутке изменения входного напряжения UBX от ЕС до 2Ео сигнал на входе 5 АЦП 2 изменяется в динамическом диапазоне от -ЕС до О, так как входной сигнал компенсируется напряжением, поступающим от компенсирующего усилителя 5 (фиг. 2д), При UBX 2Ео на выходных шинах АЦП 2 устанавливается нулевая кодовая комбинация и на выходе ПЗУ 3 формируется кодовая комбинация 01. Тогда на адресных шинах ПЗУ 11 присутствует кодовая комбинация 01000101, что соответствует определенному адресу. По этому адресу из ПЗУ 11 считывается код 01001011. Сигнал уровня логической 1, снимаемый с второго разряда ПЗУ 11, открывает второй аналоговый ключ 9, при помощи которого производится подключение второго компенсирующего усилителя 6 к входу суммирующего усилителя 1. По заднему фронту тактового импульса код с шести младших разрядов ПЗУ 11 записывается в регистр 12 памяти. Код, записанный в регистре 12 памяти (001011), поступает на адресные шины третьего ПЗУ 11, на адресных шинах ПЗУ 11 устанавливается кодовая комбинация 00101101. По этому адресу считывается кодовая комбинация, соответствующая комбинации 01010011.

Так как во вторим разряде кода уровень логической 1, то состояние второго аналогового ключа 9 не изменяется. После подключения компенсирующего усилителя 6 выходной код параллельного АЦП 2 через один такт преобразования отличается от нулевого. Соответственно выходной код ПЗУ 3 станет равным 00, адресный код ПЗУ 11 - 01001100. По этому адресу из ПЗУ 11 считывается комбинация, соответствующая коду 10011011. Полученный код записывается в регистр 12 памяти. На его выходе устанавливается код 011011, а на адресных входах ПЗУ 11 - код 01101100. Уровень логической Г в восьмом разряде выходного кода ПЗУ

11участвует в формировании окончательного выходного кода устройства при помощи, ПЗУ 4. В диапазоне изменения входного сигнала от 2Ео до ЗЕо напряжение на входе АЦП 2 определяется суммой входного сигнала и напряжений, поступающих от компенсирующих усилителей 5 и 6 (фиг. 2а, б, в, д). В дальнейшем при монотонном увеличении сигнала устройство работает аналогично описанному. Переход через значение ЗЕо вызывает срабатывание третьего ключа 10, что приводит к приведению входного сигнала в требуемый динамический диапазон (фиг. 26), так как на вход суммирующего усилителя 1 поступает сигнал от третьего компенсирующего усилителя 7, и входное напряжение АЦП 2 определяется суммой входного сигнала и напряжений от компенсирующих усилителей 5-7 (фиг. 2а, б, в, г, д), одновременно изменяется значение старших разрядов кодовых комбинаций устройства. При монотонном уменьшении входного сигнала алгоритм работы устройства будет аналогичен рассмотренному, только отключение аналоговых ключей 8-10 производится в обратном порядке. Например, рассмотрим работу преобразователя при изменении входного сигнала от 4Ео до ЗЕо. В промежутке между значениями 4Ео и ЗЕо на выходных шинах ПЗУ 3 присутствует нулевая кодовая комбинация, так как выходной код АЦП 2 отличен и от нулевого, и от единичного. Все ключи замкнуты, так как в трех младших разрядах выходного кода ПЗУ 11 присутствуют сигналы уровня логической 1 и в двух старших его разрядах присутствуют сигналы уровня логической Г. Вследствие этого выходной код ПЗУ 11 имеет вид 11011111. В регистр.

12памяти записывается комбинация 011111. В момент UBX ЗЕо на выходе ПЗУ 3 сформируется кодовая комбинация 10, в силу того что на выходе АЦП 2 в этот момент времени присутствует единичная кодовая комбинация. Тогда на адресных шинах ПЗУ

11 присутствует кодовая комбинация 011111110. По адресу из ПЗУ 11 считывается код, соответствующий комбинации 11100011. Так как в тоетьем младшем раз5 ряде сформировался сигнал логического нуля, то ключ 10 отключает от входа суммирующего усилителя 1 компенсирующий усилитель 7. На следующем такте преобразования код на выходе ПЗУ 3 не

0 изменится, так как АЦП 2 имеет задержку в преобразовании на один такт. В регистр 12 памяти записывается код 100011. Тогда адресным кодом ПЗУ 11 является код 10001110. Из ПЗУ 11 производится считыва5 ние кода, что соответствует комбинации 111010011. На этом такте преобразования состояния ключей и значения двух старших разрядов не изменились. На следующем такте преобразования выходной код ПЗУ 3

0 становится нулевым в силу того, что выходной код АЦП 2 отличен от единичного. В регистр 12 памяти записывается код 101011. Тогда адресным кодом ПЗУ 11 будет код 10101100, и на выходе ПЗУ 11 устанав5 ливается код, соответствующий комбинации 10011011. Седьмой разряд комбинации принимает нулевое значение, а два младших остаются прежними, т.е. состояние ана- логовых ключей не изменилось. В

0 дальнейшем при изменении UBX от ЗЕо до 2Ео производится обычное аналого-цифровое преобразование отсчетов входного сиг- нала при помощи параллельного АЦП 2, так как входной сигнал изменяется в диапазоне.

5 от -Ео до 0. Таким образом, на базе шестиразрядного АЦП. используя предлагаемое изобретение, можно построить восьмиразрядный АЦП за счет расширения динамического диапазона входного сигнала.

0

В предлагаемом устройстве приведение входного сигнала к динамическому диапазону параллельного АЦП происходит за

5 счет компенсации входного сигнала, причем коммутация напряжения производится при его значениях, близких к нулю. Тем самым создаются благоприятные условия для быстрого включения аналоговых ключей. В силу

0 это го н а вхо д сум м и ру ю ще го усил ител я воздействует си гнал типа ступенька амплитудой, близкой к нулю. Поскольку время установившегося значения зависит от амплитуды воздействия, то быстродействие

5 предлагаемого АЦП выше, чем у известного АЦП. При использбвании изобретения можно получить практически любую разрядность аналого-цифрового преобразователя. Возможность обработки разнополярных

игналов может быть достигнута введением

тел. клкчи

ти,

ВОР

соо ми

но с

НОГ)

постоянного смещения суммирующего уси лит|еля.

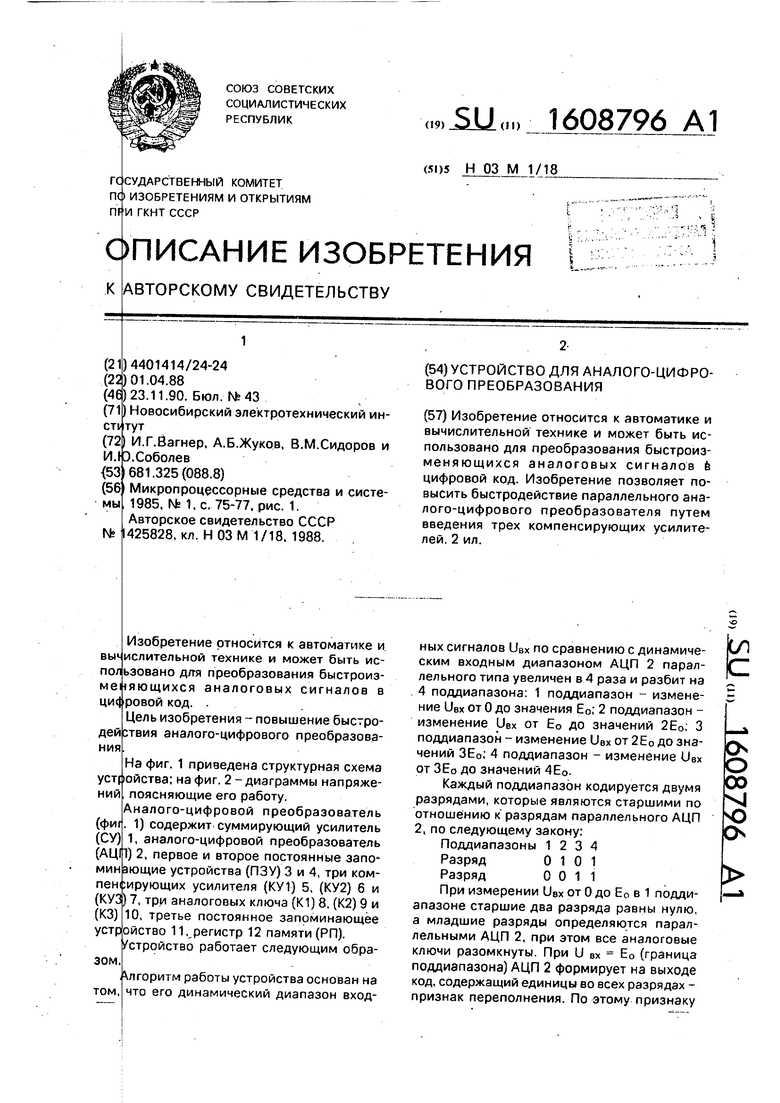

Формула изобретения , Устройство для аналого-цифрового пре- образования, содержащее суммирующий уси|питель, аналого-цифровой преобразова- первый, второй и третий аналоговые первое, второе и третье постоянные запоминающие устройства и регистр памя- гактовый вход которого является такто- шиной, а информационные входы соединены с соответствующими выходами младших разрядов третьего постоянного запоминающего устройства, два младших ад- рес|ных входа которого соединены ветственно с первым и вторым выхода- первого постоянного запоминающего ус- , старшие адресные входы третьего оянного запоминающего устройства соединены соответственно с выходами ре- гист|ра памяти, выходы аналого-цифрового азователя соединены соответствен- адресными входами первого постоян- запоминающего устройства и с младшими адресными входами второго за-

чнающего устройства, два старших ад- входа которого соединены teHHo с выходами старших разря- третьего постоянного запоминающего устр|ойства, входы управления первого, вто-

0

5

0

рого и третьего аналоговых ключей соединены с соответствующими выходами младших разрядов третьего постоянного запоминающего устройства, причем выходы первого, второго и третьего аналоговых ключей подключены к первому, второму и третьему вхо- дам суммирующего усилителя, четвертый вход которого является входной шиной, выходы второго постоянного запоминающего устройства являются выходной шиной, тактовый вход и вход опорного напряжения аналого-цифрового преобразователя подключены соответственно к тактовой шине и шине опорного напряжения, выход суммирующего усилителя подключен к входу аналого-цифрового преобразователя, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены первый, второй и третий компенсирующие усилители, причем инверсные входы первого и третьего и прямой вход второго компенсирующих усилителей объединены и являются входной шиной, инверсный вход второго и прямые входы первого и третьего компенсирующих усилителей объединены и являются шиной опорного напряжения, выходы первого, второго и третьего компенсирующих усилителей соединены соответственно с информационными входами первого, второго и третьего аналоговых ключей.

6Е.

о Га

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для аналого-цифрового преобразования | 1987 |

|

SU1425828A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1522400A1 |

| Аналого-цифровой преобразователь | 2017 |

|

RU2656989C1 |

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

| Устройство для управления преобразователем частоты с непосредственной связью и широтно-импульсным регулированием | 1989 |

|

SU1624629A1 |

| Устройство п-разрядного аналого-цифрового преобразования | 1987 |

|

SU1674367A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1279064A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для преобразования быстроизменяющихся аналоговых сигналов в цифровой код. Изобретение позволяет повысить быстродействие параллельного аналого-цифрового преобразователя путем введения трех компенсирующих усилителей. 2 ил.

Фиг.2 .

Авторы

Даты

1990-11-23—Публикация

1988-04-01—Подача