1

Изобретение относится к области вычислительной техники и может быть использовано для оперативного перестроения сетевых моделей процессов или мероприятий и как информационная система в системе управления детерминированными процессами.

Известно устройство для моделирования сетевых графиков, содержащее матрицу, каждый вертикальный ряд которой содержит по одной шине, горизонтальный ряд по две шины - основную и дополнительную, каждая ячейка одной главной диагонали квадратной матрицы содержит вентиль и диод, а остальные ячейки - диод и три контактных гнезда, одно из которых подключено к основной шине, другое к дополнительной, а третье через диод подключено к шине вертикального ряда, причем основные шины подключены через первую группу вентилей к блоку управления, через вторую группу вентилей - к блоку анализа связей, шины каждого вертикального ряда подключены к входам логических блоков и через третью группу вентилей - к блоку управления, сигнальные входы указанных трех групп вентилей подключены к блоку управления, модели работ, соединенные с выходами логических блоков и с блоком управления, а входы блока индикации соединены с логическими блоками, блоком анализа связей и блоком управления.

2

Недостатком такого устройства является то, что оно позволяет выбирать только последующие операции для выполнения операции в случае сбоя путем снятия ограничения на одновременность, а при устранении причины сбоя вновь накладывает ограничение на выполнение зависимых операций без учета того, закончены эти операции или нет. Кроме того, не обеспечивается запрет на вынолнение тех операций, которые зависят от вышедшего из строя оборудования.

Цель изобретения заключается в расширении области применения устройства для моделирования сетевого графика, т. е. в упрощении составления перечня операцпй процесса не обязательно в их логической последовательности, в получении сетевого графика не в одном варианте, отображающего статичное положение операций процесса, а всех возможных вариантов расположения и взаимосвязей операций выиолняемого процесса и оператнвного выбора возможного варианта при сбоях в ходе выполнения процесса, в обеспечении простого ввода новых илп в псключении пз процесса ненужных операций, в обеспечении проведения анализа логических связей между операциями процесса.

В предлагаемом устройстве для моделирования сетевых графиков эти цели достигнуты

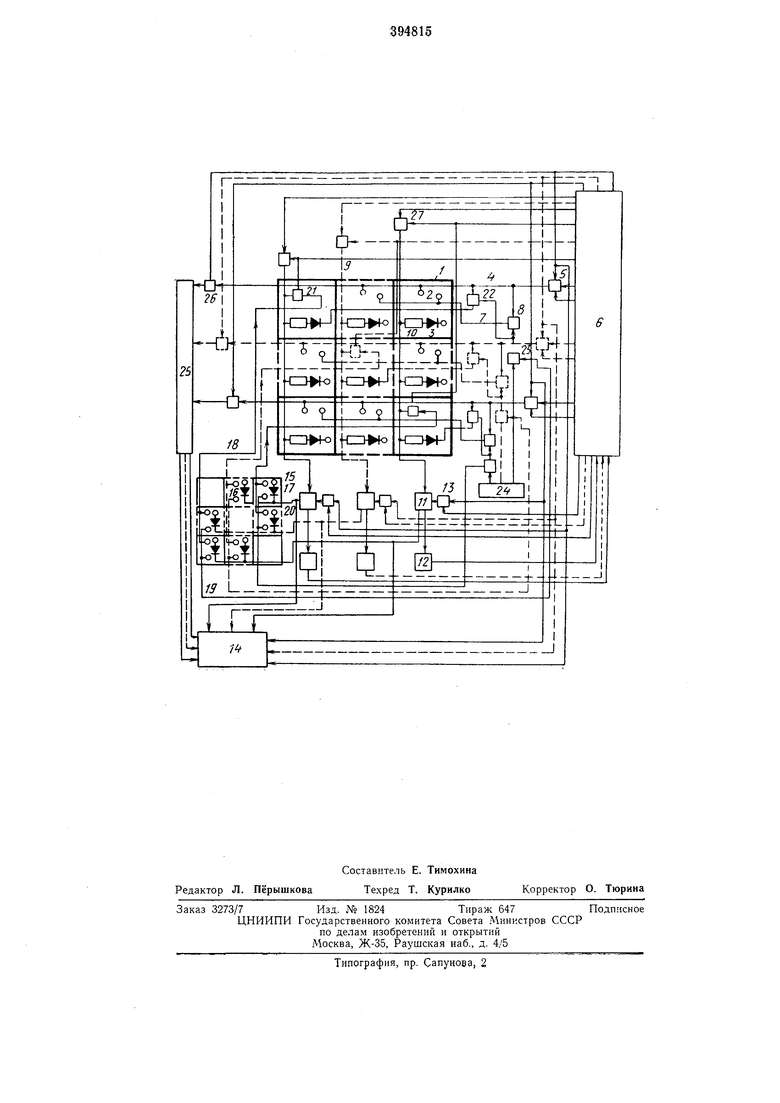

путем применения блока выдачи сбоев, догюлнР1тельных групп вентилей, логических элементов «или и второй матрицы, содержащей в каждом вертикальном ряду по две шины и в каждом горизонтальном ряду - по одной И1ине, а в каждой ячейке, кроме ячеек одиой главной диагонали, - но одному диоду и но три контактных гнезда, одно из которых нодключено к нервой вертикальной шине, другое - ко второй вертикальной шине, а третье через днод - к горизонтальной шипе, причем -первые вертикальные шины второй матрицы подключены через четвертую грунну вентилей к вертикальным шинам одноименных рядов нервой матрицы, вторые вертикальные шины второй матрицы подключены к соотБетствуюш,им логическим элементам горизонтальные шины второй матрицы подключепы к логическим блокам, доиолнитсльные входы которых подключены через пятую грунну вентилей к блоку управления, вертикальные шины первой матрицы через диоды ячеек нервой главной диагонали и шестую грунпу вептилей, а дополнительные шины через седьмую группу вентилей подключены к соответствующим основным шинам первой матрицы; сигнальные входы шестой и седьмой групп вентилей подключены к выходам соответствующих логических элементов «ИЛИ, входы которых подключены к блоку выдачи сбоев, а сигнальные входы четвертой и пятой групП вентилей подключепы к блоку упра.вления. Устройство представлено на чертеже. В ячейках квадратной мат|рицы / расположено по три контактных гнезда 2, кроме ячеек главной диагонали, и по одному диоду 3. Основные шины 4, проложенные в горизонтальных рядах матрицы 1, подключены через вентили 5 к блоку управления 6, совмещенному с блоком событий окончания вынолнеНИН работ, и в ячейках матрицы к контактному гнезду 2. Два сигнальных входа вентилей 5 подключены к блоку унравления 6. Донолнительные щины 7 проложены в горизонтальных рядах матрицы / и подключены через вентили 8 к основным шинам 4 и в ячейках матрицы У ко вторым контактным гнездам 2. В вертикальных рядах матрицы / проложены щины 9, подключенные в ячейках матрицы через резисторы 10 и диоды 3 к третьим контактным гнездам 2. Шины 9 подключены по одной к логическим блокам 11, формирующим сигналы на начало вынолнения работ. Блоки // подключены к моделям работ 12 и через вентили 13 к блоку управления 6. Модели работ 12 и сигнальные входы вентилей 13 нодключены к блоку управления 6. Блок индикации 14 подключен к блоку управления 6 и к логическим блокам //. Вторая матрица 15, в ячейках которой, за исключением ячеек главной диагонали, расположены по три контактных гнезда 16 и по одному диоду 17, содержит в каждом вертикальном ряду по две шины 18 и 19, а в каждом горизонтальном ряду по одной шнне 20. Шины 18 подключены через вентили 21 к шинам РНК одному контактно1му гнезду 16 в ячейках матрицы 15. Сигнальные входы вентилей 21 иодключены к блоку унравления 6. Шины 20 подключены к логическим блокам 11 и через диоды 17 ко вторым контактным нездам 16 ячеек матрицы 15. Шины 9 через диоды 3 и резисторы 10, расноложенные в ячейках главной диаго 1али матрицы /, подключены к основным шинам 4 через вентили 22. Сигнальные входы вентилей 8 Л 22 подключены к логическим элементам «ИЛИ 23. Входы логических элементов «ИЛИ 23 подключены к шинам 19 и к блоку выдачи сбоев 24. Блок выдачи сбоев 24 может быть вынолиен в виде коммутационного матричного поля с вертикальными и горизонтальными шинами в его рядах, а также с диодами и контактными гнездами в его ячейках. Блок англиза связей 25 через вентили 26 подключен к основным шинам 4. Шины 9 подключены через вентили 27 к блоку управления 6. Сигнальные входы вентилей 26 и 27 подключены к блоку унравления 6. Scтpoйcтвo работает следующим образом. Каждому ряду, вертикальному и горизонтальному, матриц /, 15 ставят в соответствие одну онерацию процесса, при этом перечень операций, соответствующий горизоптальным рядам сверху вниз, одинаков с перечнем онераций, соответствующему вертикальным рядам слева направо. В матрицах 1 и 15 перечни операций однозначно соответствуют друг другу. Для нормального функционирования устройства число операции процесса не должно превышать числа вертикальных (горизонтальных) рядов матрицы / или 15. После постановки каждо му ряду матрицы / и 15 в соответствие одной операции вводят путем постановки перемычек в ячейках матрицы / логическую зависимость между операцией, приписанной вертикальному ряду, от онерации, приписанной горизонтальному ряду, при этом ячейка, куда вносится эта зависимость, находится на пересечении указанных рядов. Перемычки ставятся между контактными гнездами 2, нодключенными к диодам 3 и основным шинам 4. Таким образом, заносится логическая связь между всеми онерациями процесса. Для операций, порядок следовапия которых взаимно не ограничен, но ограничено их параллельное выполнение, например, для двух операций используется одно оборудование, также вносится логическая связь, но в этом случае между контактьым гнездом 2, подключенным к диоду 3, и контактным гнездом 2, подключенным к дополнительной шине 7. В этом случае предпочтительное выполнение будет определено для той операции, которой соответствует горизонтальный ряд, содержащий указанную ячейку. В ячейки матрицы 15 вносится зависимость между операциями ироцесса, ограниченными на нараллельное выполнение. Для этого перемычки ставятся между контактнььми гнездами 16, подключенными к диодам /7 и 19, в тех ячейках, которые соответствуют ячейкам первой матрицы.

В практике встречаются операции, длительность выполнения которых посит случайный характер н сравнима с продолжительностью всего процесса, а их выиолнение ведется в основном параллельно со всеми остальными операциями процесса за исключением некоторых. В этом случае для длительной операцнн необходимо сделать паузу иа время выполиения песовместимых с ней операций. Кроме того, такую операцию трудно разбить на ряд этапов ее выполнения, чтобы каждому этапу соответствовало вполне определенное событие. Такое временное ограничение, т. е. запрет на параллельиое выиолнение операций, вносится при помощи перемычек, устапавливаемых в ячейках матрицы 15 между контактными гнездами 16, подключениыми к диодам 17 и шииам 18.

После ввода всей программы в матрицы / и 15 на устройство подается электрическое напряжение.

В исходном состоянии вентили 5, 8, 13, 21, 26 открыты, а вентили 22, 27 закрыты.

С подачей сигналов па шины 4 через вентили 5 с блока управления 6 сигналы через вентили 8 проходят на шины 7 и с шип 4, 7 через перемычки, установлеиные в ячейках матрицы / между контактными гнездами 2, на шины 9 и далее на логические блоки //. Блоки // анализируют логические связи между операциями процесса. Если логической зависимосги между какой-либо операцией и всеми другими нет, т. е. она может быть выполнена первой, то ей соответствуюший логический блок // выдает разрешающий сигнал в модель работ 12 на начало выполнения работы (операции) и сигнал в блок индикации 14, где загорается индикатор, соответствующий этой операции. Сигнал с выхода модели работ 12 подается в )стройство управления 6, которое выдает управляющий сигнал на сигнальные входы вентилей 5, 13, 26, которые закрываются, и иа блок индикации 14. Вентиль 5 отключает шину 4, а вентиль /5-логический блок 11, cooтвeтcтвyюиzиe выполненной операции.

Отключение шины 4 для выполненной операции соответствует устранению логической связи между выполнен-ной операцией и всеми оставшимися или, что то же самое, если шина 4 ие отключается от устройства управле ия 6, изъятию из ячеек этого ряда всех перемычек. Неотключеииые блоки // вновь анализируют логические связи между оставшимися операциями, и процесс повторяется по описанному способу, при этом восироизводится пормальная логическая последовательность операций процесса, т. е. обеспечивается воспроизведение обычного сетевого графика.

Временное ограничение для исиолияемой операции на время вьшолнеция операции, несовместимой с пси, накладывается по шлне /5 матрицы 15. Сигнал с логического блока //, соответствующего несовместимой оиерации, проходит иа шину 20 и с нее через диод

17, перемычку, подключеппую к контактным гнездам 16, на шину 18, с шины 18 через вентиль 21 на шину 9 и далее иа логический блок //, соответствующий операции, выиолняемой в основном параллельно, который выдает запрещающий сигнал в модель работ 12. По исполнению несовместнмой оиерации сигиал с выхода логического блока 11, соответствующего этой операции, снимается, и дается разрещеиие на продолжение операццц, времсппо запрещеииой.

С блока выдачи сбоев 24 можио вводить различпого рода возмущения в нормальный ход моделирования операций ироцееса, тем самым имеется возможность получить все

возможные варианты сетевого графика. Сигиал с блока выдачи сбоев 24 проходит через логический элемент «ИЛИ 23 иа сигнальные входы вентилей 8 и 22. Вентиль 8 закрывается, снимая сигиал, идущий с шины 4 иа

шину 7.

Этим самым снимается ограннчеиие на начало выиолнения операции, иа которую было наложено ограиичение на одновремеиное нсполнение. Вентиль 22 открывается, и сигцал с щипы 4 проходит иа шину 9 через диод 3 и резистор 10, расположенные в ячейке главной диагонали матрицы 1, и далее на логический блок //, тем самым запрещается исполнение операции, которая зависит от внесенного возмущения, например, имитация выхода из строя оборудования.

При снятии возмущения сигнал с выхода блока сбоев 24 пропадает, вентили 8, 22 переходят в первоначальное состояние, а значит устройство переходит в состояп1 е, предшествующее возмущению с учетом того, что за время возмущения независимые от него операции или уже выполнены, или исполняютея. Если же параллельная операция, ограниченная на одновремещюе выполнение, за время возмущения не окончилась, 8 I 22 не переходят в псходное состояние. В этом случае сигнал на логический элемент

«ИЛИ 23 ноступает с шины 19, на которую сигиал проходит с выхода логического блока // через щииу 20, диод /7 и перемычку, установленную в соответствующей ячейке матрицы 15 между контактными гнездами 16.

С исполнением онерацип, ограпиченной иа одновременность, блок логики //, предназначенный для этой операции, отключается, сигиал с шины 20 снимается, а значит с шины 19 и логического элемента «ИЛИ 23,

вентили 8, 22 переходят в исходное состояние.

Такнм образом, при помощи блока выдачи сбоев 24 можио моделировать сетевой график при разных сочетаниях зависимых на

одновременность операций, определяя паиболее оптимальный вариант выполнения процесса.

Для ироведенпя аналпза логических связей между онерациямп процесса, т. е. определения всех тех операций, от которых зависит какая-либо конкретная Операция, достаточно подать иа сигнальный вход вентиля 27 п через него на шину Я соответствуюш,ую выбранной операции, сигналы с выхода блока управления 6. Одновременно сигналы управлен 1Я с выхода блока управления 6 нодаются на все вторые сигнальные входы вентилей 5, которые закрываются, и па вход вентиля 21, соответствующего выбранной операции, который также закрывается. Сигнал с шины 9 ироходит па шипы 4 через перемычки, установлеппые в ячейках матрицы /, и далее через вентили 26 на блок анализа связей 25. С блока анализа связей 25 сигналы поступают на блок индикации 14, где загорается сигнал для тех операций, от которых зависит выбран1ная операция. Если прямой зависимости выбранной операции от некоторых предыдущих ей пет, то такую зависимость можно установить путем последовательного перебора операций процесса. Когда часть операций процесса выполнена, закрыты соответствующие им вентили 26.

Предмет изобретения

Устройство для моделирования сетевых графиков, содержащее матрицу, каждый вертикальный ряд которой содержит по одной шине, торизонтальпый ряд но две шины - осиовную и дополнительную, каждая ячейка одной глаВной диагонали квадратной матрицы содержит вентиль и диод, а остальные ячейки - диод и три контактных гнезда, одно из которых подключено к OCHOBHOII шине, другое к дополнительной, а третье через диод подключено к шине вертикального ряда, причем основные шипы подключепы через первую группу вентилей к блоку управления, через вторую группу вентилей - к блоку анализа связей, шины каждого вертикального ряда подключены к входам логических блоков и через третью группу вентплей - к блоку управления, сигнальные входы указан ных

трех групп вентилей подключены к блоку управления, модели работ, соединенные с выходами логических блоков и с блоком управления, а входы блока индикации соединены с логическими блоками, блоком анализа связей и блоком управления, отличающееся тем, что, с целью расширения области применения устройства, в него введены блок выдачи сбоев, дополнительные группы вентилей, логические элементы «ИЛИ и вторая матрица,

содержащая в каждом вертикальном ряду по две щины и в каждом горизонтальном ряду по одной щине, а в каждой ячейке, кроме ячеек одной главной диагонали, - по одному диоду и по три контактных гнезда, одно

из которых подключено к первой вертикальной щине, другое ко второй вертикальной щине, а третье через диод к горизонтальной щине, причем первые вертикальные шины второй матрицы подключены через четвертую

группу вентилей к вертикальным шинам одноименных рядов первой матрицы, вторые вертикальные щины второй матрицы подключены к соответствующим логическим элементам горизонтальные щины второй

матрицы подключены к логическим блокам, дополнительные входы которых подключены через .пятую группу вентилей к блоку управления, вертикальные щины первой матрицы через диоды ячеек первой главной диагонали

и щестую группу вентилей, а дополнительные щины через седьмую группу вентилей подключены к соответствующим основным щинам первой матрицы; сигнальные входы щестой и седьмой группы вентилей подключены

к выходам соответствующих логических элементов «ИЛИ, входы которых подключены к блоку выдачи сбоев, а сигнальные входы .четвертой и пятой групп вентилей подключены к блоку управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВСЕСОНЭЗНАН | 1973 |

|

SU368602A1 |

| УСТРОЙСТВО для ПОИСКА ПРАДЕРЕВЬЕВ НАПРАВЛЕННОГО ГРАФА | 1968 |

|

SU212633A1 |

| КОММУТИРУЮЩЕЕ УСТРОЙСТВО ДЛЯ ГРУППЫ ДАТЧИКОВ | 1971 |

|

SU310394A1 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ НАБОРНО-ПИШУЩЕГО АВТОМАТА | 1973 |

|

SU407424A1 |

| УСТРОЙСТВО для СЧИТЫВАНИЯ ОСЦИЛЛОГРАММ | 1968 |

|

SU218546A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА СИГНАЛОВ КОМАНДНОЙ МАТРИЦЫ | 2011 |

|

RU2487393C1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| ОПЕРАЦИОННОЕ УСТРОЙСТВО ДЛЯ ПРОЦЕССОРА С АССОЦИАТИВНОЙ МАТРИЦЕЙ ОДНОРОДНОЙ СТРУКТУРЫ | 1984 |

|

RU2087031C1 |

| Ассоциативная ячейка памяти | 1973 |

|

SU513393A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПЕРЕДАЧИ ГРАФА | 1970 |

|

SU259495A1 |

Даты

1973-01-01—Публикация