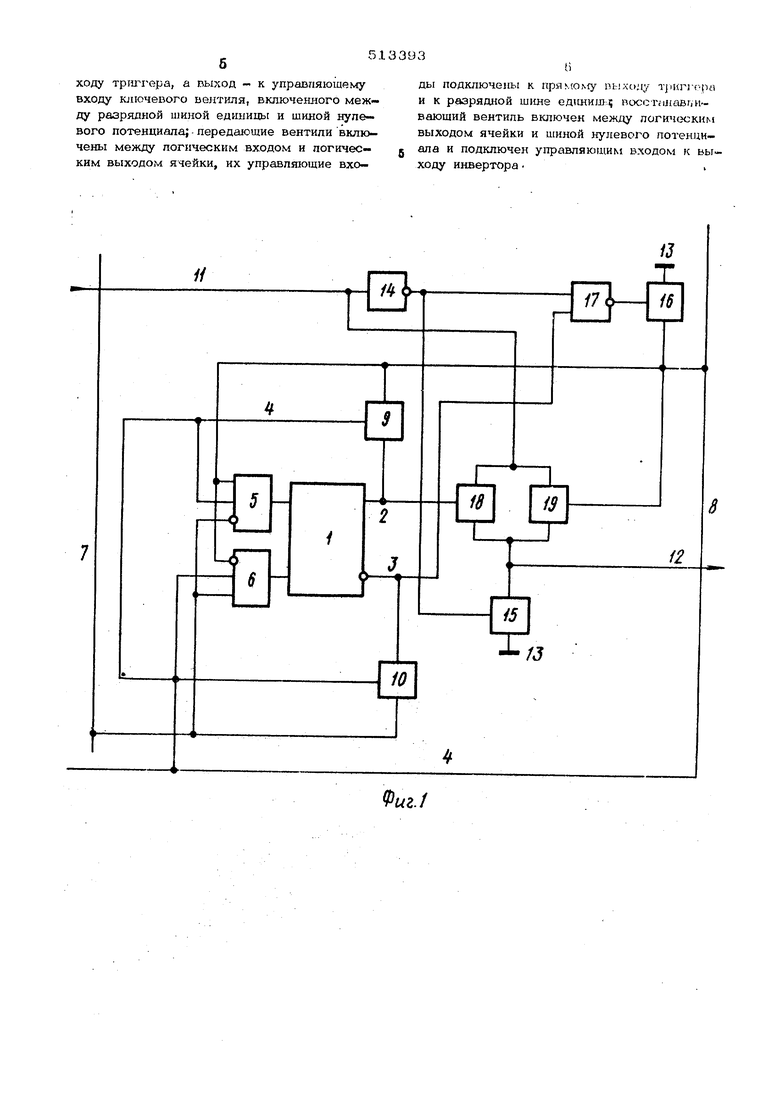

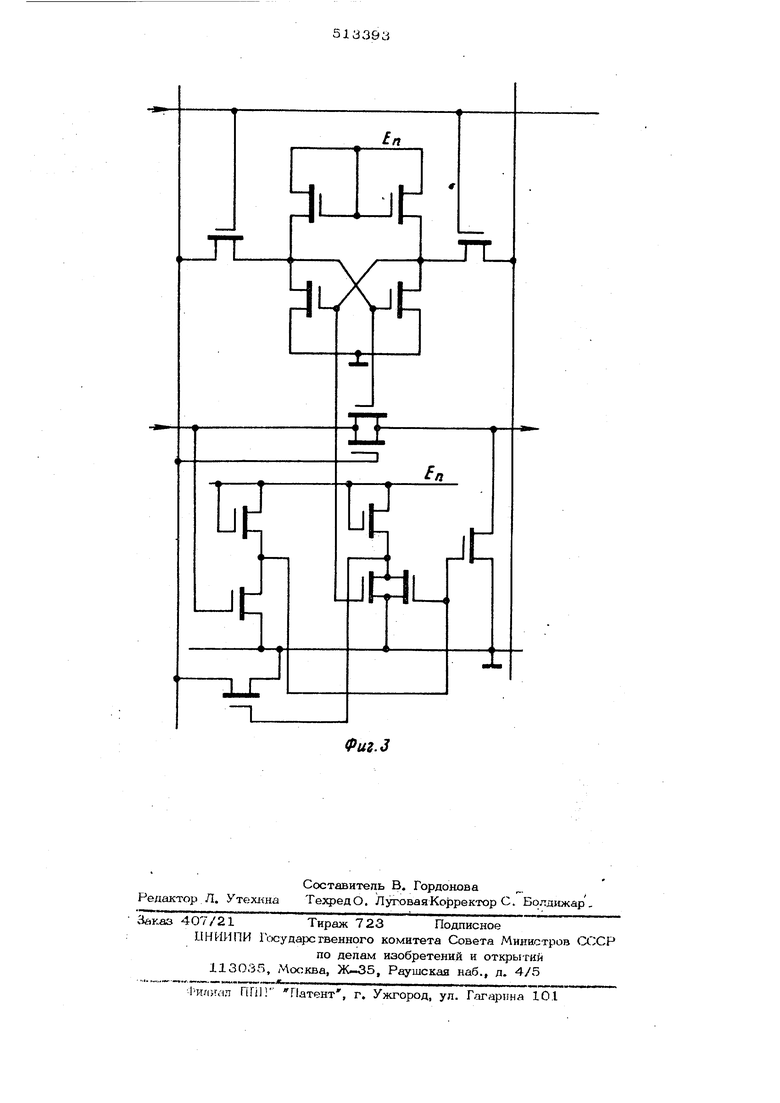

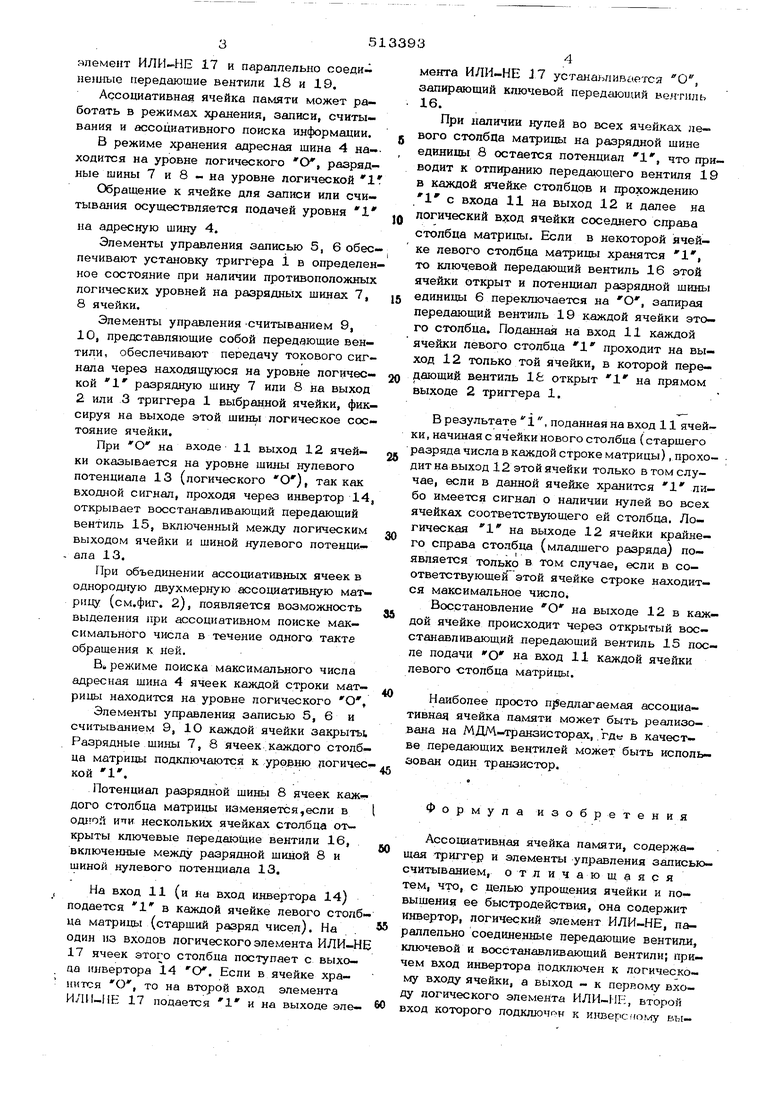

ялемент ИЛИ-НЕ 17 и параллельно соединезшые передающие вентили 18 и 19. Ассоциативная ячейка памяти может работать в режимах хранения, записи, считывания и ассоциативного поиска информации. В режиме хранения адресная шина 4 находится на уровне логического О, разрядные шины 7 и 8 - на уровне логической I Обращение к ячейке для записи или считывания осуществляется подачей уровня на адресную шину 4. Элементы управления записью 5, 6 обеспечивают установку триггера 1 в определен ное состояние при наличии противоположньис логических уровней на разрядных шинах 7, 8 ячейки. Элементы управления Считыванием 9, 10, представляющие собой передающие вентили, обеспечивают передачу токового сигнала через находящуюся на уровне логической 1 разрядную щину 7 или 8 на выход 2 или 3 триггера 1 выбранной ячейки, фиксируя на выходе этой щинь( логическое состояние ячейки. При О на входе 11 выход 12 ячейки оказывается на уровне шины нулевого потенциала 13 (логического О), так как входной сигнал, проходя через инвертор 14 открывает восстанавливающий передающий вентиль 15, включенный между логическим выходом ячейки и шиной нулевого потенци- - ала 13. При объединении ассоциативных ячеек в однородную двухмерную ассоциативную матрицу (см.фиг. 2), появляется возможность выделения при ассоциативном поиске максимального числа в течение одного такте обращения к ней. В режиме поиска максимального числа адресная шина 4 ячеек каждой строки матрицы находится на уровне логического О, Элементы управления записью 5, 6 и считыванием 9, 1О каждой ячейки закрыть Разрядные шины 7, 8 ячеек; каждого столб ца матрицы подключаются к уррэню рогичес кой . Потенциал разрядной шины 8 ячеек каж дого столбца матрицы изменяется,если в оштой ипи нескольких ячейках столбца открыты ключевые предающие вентили 16, включенные между разрядной шиной 8 и шиной нулевого потенциала 13. ,На вход 11 (и На вход инвертора 14) подается в каждой ячейке левого столб ца матрицы (старший разряд чисел). На . один из входов логического элемента ИЛИ-Н 17 ячеек этого столбца поступает с выхоца инвертора 14 О. Если в ячейке хранится О, то на второй вход элемента ИЛИ-ИЕ 17 подается и на выходе элемента ИЛИ-НЕ 17 устанаьливаегся О, запирающий ключевой передгиощий велтиль 16. При наличии нулей во всех ячейках левого столбца матрицы на разрядной шине единицы 8 остается потенциал , что приводит к отпиранию передающего вентиля 19 в каждой ячейке столбцов и прохождению с входа 11 на выход 12 и далее на логический вход ячейки соседнего справа столбца матрицы. Если в некоторой ячейке левого столбца матрицы хранятся , то ключевой передающий вентиль 16 этой ячейки открыт и потенциал разрядной шины единицы 6 перекшочается на О, запирая передающий вентиль 19 каждой ячейки этого столбца. Поданная на вход 11 каждой ячейки левого столбца 1 проходит на выход 12 только той ячейки, в которой пере- дающий вентиль Ife открыт 1 на прямом выходе 2 триггера 1. В результате i., поданная на вход 11 ячейки, начиная с ячейки нового столбца (старшего разряда числа в каждой строке матрицы), прохо- . дит на выход 12 этой ячейки только в том случае, если в данной ячейке хранится I либо имеется сигнал о наличии нулей во всех ячейках соответствующего ей столбца. Логическая I на выходе 12 ячейки крайнего справа столбца (младшего разряда) появляется только в том случае, если в соответствующей этой ячейке строке находится максимальное число. Восстановление О на выходе 12 в каждой ячейке происходит через открытый восстанавливающий передающий вентиль 15 после подачи О на вход 11 каждой ячейки левого столбца матрицы. Наиболее просто п 5едлагаемая ассоциативная ячейка памяти может быть реализована на МДМ-транзисторах, .где в качестве передающих вентилей может быть использован один транзистор. Формула изобретения Ассоциативная ячейка памяти, содержащая триггер и элементы управления записьюсчитыванием, отличающаяся тем, что, с целью упрощения ячейки и повышения ее быстродействия, она содержит инвертор, логический элемент ИЛИ-НЕ, параллельно соединенные передающие вентили, ключевой и восстанавливающий вентили; причем вход инвертора подключен к логическому входу ячейки, а выход - к nepBONiy входу логического элемента , второй вход которого подключен к ИНВерС.-(0(Иу ВЬ ходу трш 1ера, а пыход - к управляющему входу ключевого вентиля, включенного между разрядной шиной единицы и шиной нулевого потенциала; передающие вентили включены между логическим входом и логическим выходом ячейки, их управляющие входы подключены к ПрЯ.ЮМу ПЫХОДу TJiUTlTpn

и к разрядной Ш1ще единиш ; воссг.исавпи- вающий вентиль включен между логич(к:ким выходом ячейки и шиной нулевого потенциала и подключен управляющим входом к выходу инвертора

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативная ячейка памяти | 1973 |

|

SU513392A1 |

| Ассоциативный запоминающийэлЕМЕНТ | 1979 |

|

SU809376A1 |

| Элемент ассоциативной памяти | 1980 |

|

SU875460A1 |

| ОПЕРАЦИОННОЕ УСТРОЙСТВО ДЛЯ ПРОЦЕССОРА С АССОЦИАТИВНОЙ МАТРИЦЕЙ ОДНОРОДНОЙ СТРУКТУРЫ | 1984 |

|

RU2087031C1 |

| Ассоциативный запоминающий элемент | 1980 |

|

SU928415A1 |

| Асооциативная однородная среда | 1978 |

|

SU798803A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МДП-ТРАНЗИСТОРАХ | 1973 |

|

SU408374A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1824650A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Накопитель для оперативного запоминающего устройства | 1986 |

|

SU1376118A1 |

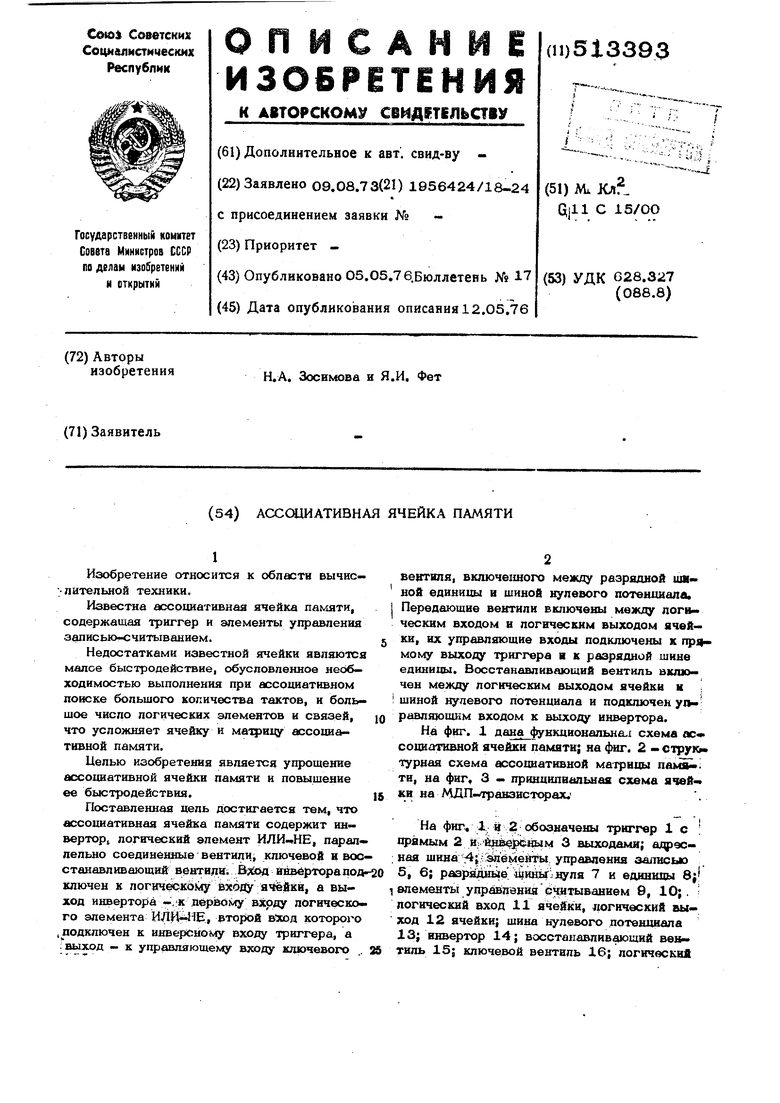

11

13

т

1И

f6

18

13

12

J

о- -

Фиг./

II

Фыг.2

ai-bK

pm

TL

«

IF

E

JC

mu

Фиг.З

Авторы

Даты

1976-05-05—Публикация

1973-08-09—Подача