Предлагаемое изобретение относится к области вычислительной техники и предназначено для применения в вычислительных устройствах, выполняющих вычислительно-логические операции и использующих запоминающее устройство, специально спроектированное для этой цели.

Известны цифровые вычислительно-логические устройства, использующие стандартное магнитное оперативное запоминающее устройство МОЗУ с линейной выборкой для выполнения логических и арифметических операций.

Предлагаемое вычислительно-логическое устройство отличается от известных тем, что в нем выход каждого реверсивного формирователя подсоединен ,к одному концу соответствующей словарной щины, противоположные объединенные концы соседних словарных щин подключены к реверсивным ключам, входы реверсивных формирователей и реверсивных ключей подсоединены к соответствующим выходам блока управления, входы ключей формирователей и вентилей, подсоединенных к выходам соответствующих ступеней разрядных дещифраторов, подсоединены также к соответствующим выходам блока управления.

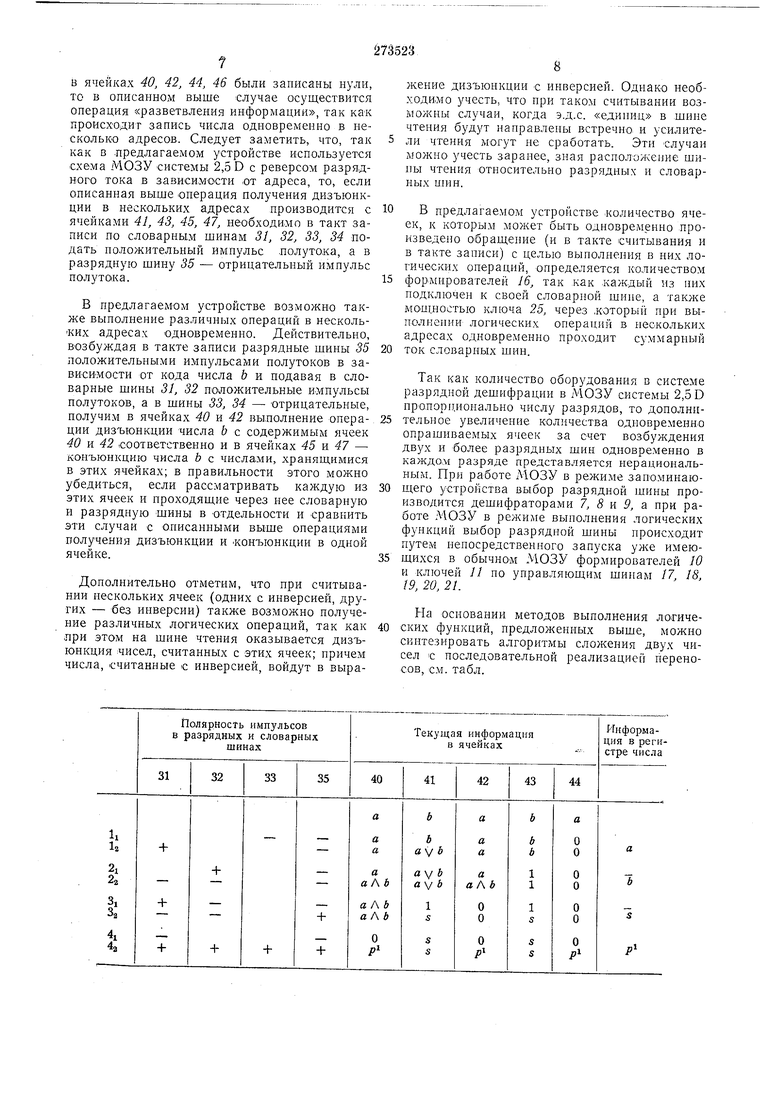

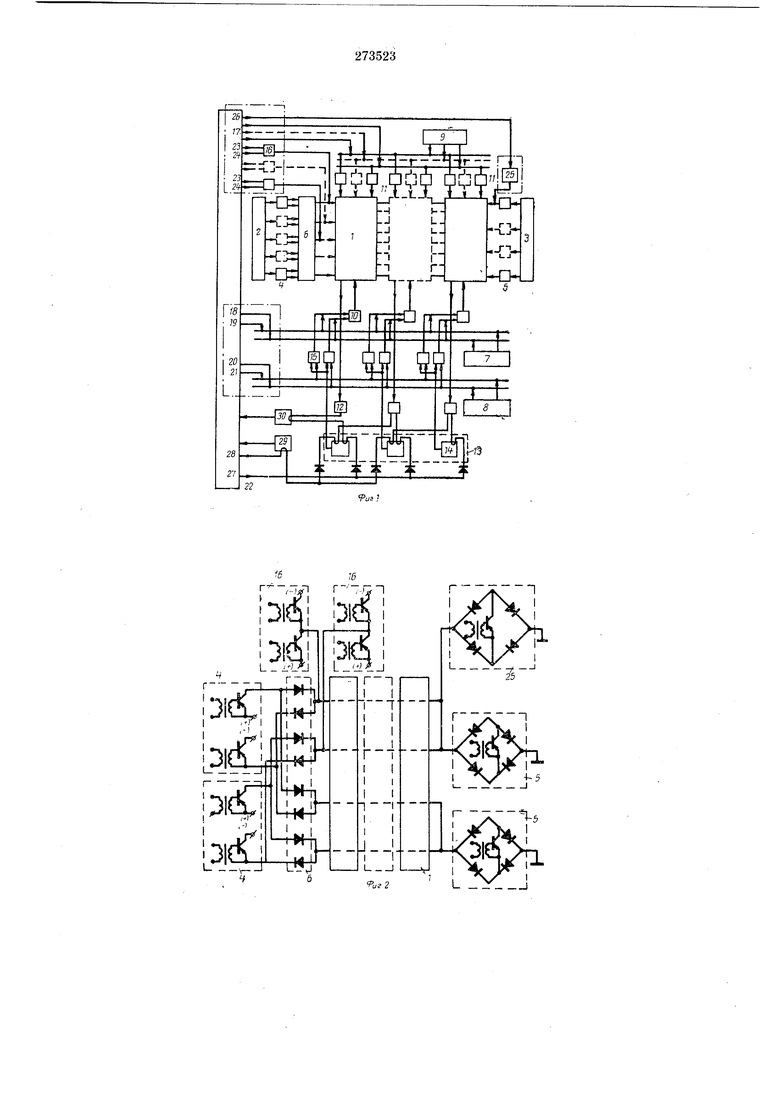

Предлагаемое устройство выполнено на элементах системы 2,5 D, что позволяет повысить быстродействие запоминающего устройства за счет уменьшения числа сердечников, прошиваемых одной щнной, позволяет также увеличить допуски на отклонение амплитуды токов п имеет ряд других преимуществ. Если рассматривать магнитные элементы МОЗУ системы 2,5 D как многофункциональные с настройкой управляющими сигналами в виде импульсов тока, подаваемых в словарные и разрядные шины, то становится возможным при незначительном увеличении количества оборудования выполнять логические и ариф,метические операции непосредственно в матрицах МОЗУ. Для этой цели к нескольким словарным шинам подключаются отдельные формирователи тока, полярность импульсов и момент срабатывания которых задаются управляющим устройством. На пересечении этих словарных шин с К разрядными щинами (К чнсла разрядных шин в одном разряде МОЗУ системы 2,5D) образуется некоторое количество адресов, которые могут быть названы функциональной частью МОЗУ в отличие от остальной части МОЗУ, которую назовем основным массивом МОЗУ. вится возможным получение различных функций. Если слово находится в основном массиве МОЗУ, то его предварительно нужно перевести Б функциональную часть, и в ней, подавая нмлульсы соответствующей полярности в определенной последовательности по слюварным и разрядным шинам, .можно выполнить над словом (или словами) логическую операцию (операции). На фиг. 1 приведена структурная схема предлагаемого цифрового вычислительно-логического устройства, в которОМ арифметические и логические операции выполняются на матрицах МОЗУ системы 2,5 D . Ыа фиг. 2 представлены, в .качестве приме- 15 ра, система дешифрации, схемы формирователей и ключей, используемых в предлагаемом устройстве. На фиг. 3 приведена схема расположения словарных и разрядных, шин для одного разряда матрицы МОЗУ системы 2,5 D. На фиг. 1 .приняты следующие обозначения: разрядные матрицы МОЗУ 1 системы 2,50; словарные дешифраторы 2 и 5 первой и вто- 25 рой ступеней дешифрации соответственно; соответственно реверсивные формирователи и ключи 4 и 5 словариой системы шин; диодная Матрица 6 словарной системы шин (по два диода па шину); разрядный дешифратор 7 30 первой ступени, работающий в такте считывания; разрядный дешифратор 8 первой ступени, работающий в такте записи; разрядный дешифратор 9 второй ступени, работающий в тактах записи и считывания; реверсивные фор- 35 мирователи 10 и ключи // разрядпой системы шин; усилители чтения 12; регистр числа 13; формирователи 14 регистра числа; вентили (схемы совпадения) 15, которые производят запуск разрядных формирователей 10 в зави-40 симости от информации, иоступающей из регистра числа 13 и из дешифратора 8; дополнительные формирователи 16 (см. фиг. 1), необходимые для выполнения логических операций в матрицах МОЗУ; количество формиро-45 вателей 16 равно Л , где п - число еловарных шин; управляющие шины 17-2,1, по которым из управляющего устройства поступают сигналы, определяющие выбор одной из р.азрядных шин с целью выполнения требуе-50 мой логической операции в соответствующем адресе, т. е. эти сигналы производят разрядную дешифрацию в тактах считывания и запи,си лри работе устройства в режиме выполнения логических операций; управляющие шины55 /7 производят выбор соответствующего разрядного ключа (вторая .ступень дешифрации), в .общем случае количество управляющих шин 17 равно т, , где k - число разрядных шин в одном разряде; управляющие шины 18, 5 10 60 19 осуществляют разрядную дешифрацию первой ступени в такт считывания, а управляюпдие шины 20, 2.1 (с учетом инфор,мации из регистра числа) - в такт записи; следует заметить, что здесь рассматривается вариант МОЗУ системы 2,5 D с реверсом разрядного тока в зависимости от адреса (вариант с уменьшенным количеством разрядного оборудования) ; реверс тока осуществляется первой ступенью разрядной дешифрации; управляющее устройство 22; управляющие шины 23, 24, по которым из управляющего устройства 22 подаются сигналы на запуск формирователей 16 для получения от них импульсов лоложительной и отрицательной полярности соответствеппо; специальный ключ 25 в системе слоВарной дешифрации, запускаемый от управляющего устройства 22 одиовременно с формирователями 16; необходимость в этом специальном ключе возникает при выполнении логических функций в нескольких адресах одновременно, когда через пего должен пройти суммарный ток нескольких словарных шин; возможно в некоторых случаях совмещение ключа 25 с существующими в обычном МОЗУ Ключами 5: управляющая шина 26, по которой происходит запуск ключа 25; стробирующий сигнал 27 из управляющего устройства 22, производящий запись информации с усилителей чтения 12 на формирователи 14 регистра числа; стробирующий сигнал 28, производящий запись информации с усилителей чтения 12 на формирователи 14 со сдвигом на разряд влево; усилитель контроля 29, который срабатывает и посылает сигнал в управляющее устройство 22 при наличии хотя бы одной «единицы в .слове на выходах усилителей чтения 72 при подаче строба 28 (контроль наличия «переноса); усилитель контроля 30, который срабатывает при наличии «единицы в старшем разряде (контроль старшего разряНа фиг. 2 в качестве примера приведена система дешифрации, используемая в предлагаемом устройстве, и показаны схемы отдельных формирователей. Словарный дешифратор включает в себя диодную матрицу 6, словарпые формирователи 4 и словарные ключи 5; в выходные цепи дешифратора включены словарные шины .матриц / МОЗУ системы 2,5 D. На фиг. 2 показано также подключение к словарны.м шинам нововведенных реверсивных формирователей 16 и специального ключа 25. Каждый формирователь 16 подключается к с;дному концу своей словарной шины, а ключ 25 подсоединяется к объединению противоположных концов этих словарных шин, таким образом, в функциональной части МОЗУ оказывается р-т адресов. При необходимости увеличения количества адресов в функциональной части МОЗУ возможно использование еще нескольких ключей 25, которые подключаются к .другим объединениям словарных

В системе разрядной дешифрации используются формирователи Ю, схема которых аналогична схеме формирователей 16, и ключи 11, подобные ключам 5.

Остальные узлы предлагаемого цифрового вычислительн10-логического устройства соответствуют обычиому МОЗУ системы 2,50 и ноэтому примерами не сопровождаются. Возможность осуществления нововведенных связей 17-21, 23, 24 для любых схем обычного МОЗУ и возможность построения управляющего устройства, дающего импульсы на определенных управляющих шинах в определенные моменты времени, являются очевидными и подтверждение их в виде примеров - излишним.

Для пояснения возможности получения логических функций на матрицах МОЗУ системы 2,5D рассмотрим работу одного разряда МОЗУ, схема распололсения шин которого представлена на фиг. 3. Здесь взяты для рассмотрения четыре словарные шины 31-34, че1ыре разрядные шины 35-38 и ячейки 55-47, находящиеся на пересечениях этих шин (шина чтения на фиг. 3 не показана).

Рассмотрим выполнение простейших логических операций - отрицания, дизъюнкции и конъюнкции - в одном адресе МОЗУ, например в ячейке 40 (см. фиг. 3), которая находится на пересечении словарной шины 31 и разрядной шины 35. Условимся, что наличие двух отрицательных импульсов полутоков по шинам 31 и 35 переводит ячейку 40 в состояние «нуль, наличие двух положительных импульсоз - в состояние «единица, а также, что усилитель чтения чувствителен к обеим полярностям э.д.с. на шине чтения (последнее совпадает с требованием к усилителям чтения в обычном МОЗУ системы 2,50).

Очевидно, что если в ячейке 40 хранилось чкгло а, то при подаче по шинам 31 и 35 отрицательных импульсов полуто-ков произойдет обычное считывание, и с шин чтения на усилители чтения и в регистр числа поступит прямой код числа. Если же .произвести считывание числа ие отрицательными, а положительными импульсами полутоков (по тем же шинам 31 и 35), то на усилители чтения поступит уже обратный код числа, т. е. осуществится

операция а - инверсия числа а.

Операция дизъюнкции avb (b - слово, подаваемое в разрядные шины 55 при записи) получится, если в ячейку 40, где, допустим, уже записано число а, записать число b (без предварительного считывания числа а), для чего в такте заниси по шинам 3/ и 35 подать положительные импульсы иолутоков; разрядные шины возбуждаются кодом числа Ь, предварительно записанным в регистр числа 13. Действительно, в ячейке 40 «единицы будут записаны в тех разрядах, которые соответствуют «единицам слова а или «единицам слова Ь. Предварительная запись слова 6 в регистр числа производится в такте

считывания, непосредственно предшествовавшем такту записи, в которо:м выполняется операция дизъюнкции, в результате считывания 51чеЙ1 и, в которой хранилось слово b (допустим, ячейки 42). Очевидно, что здесь в такте считывания обращение будет происходить по одному адресу (обращение к ячейке 42), а в такте записи - по другому (обращение к ячейке 40). Это можно осуществить с помощью нововведенных управляющих связей 17-21, 23-24, 26, а именно: с помощью этих связей производится запуск формирователя 16, соответствующего выбираемой словарной шине, специального ключа 25, а также формирователей 10 и ключей 11 для получения в разрядной шине импульсов определенной полярности в такте считывания и в такте записи. Заметим, что одновременно с операцией avb в записи мол-:ет быть осуществлена регеиерация числа b в ячейку 42, для чего в такте записи одновременно со словарной шиной 31 возбуждается и шина 32 (т. е., управляющее устройство запускает одновременно два фор iиpoвaтeля 16. а именно те, которые соответствуют этим словарным шинам).

Логическую операцию конъюнкции в ячейке 40 можно получить, если в такт считыВЭ1ЩЯ считать число b с инверсией, например, па ячейке 42 (где, допустим, оно хранилось)

1 в такт записи подать на шииы 31 и 35 (обращение к ячейке 40, где уже записано число а) не положительные, как это происходит при обычной записи, а отрицательные импульсы полутоков; при этом в тех разрядах, где

6 0 (в этих разрядах усилители чтения при считывании b с инверсией сработают), на число о будет действовать полный ток в сторону нуля, который произведет стирание «единиц числа а в этих разрядах, и, таким образом,

в ячейке 40, где раньше было записано число а, теперь окажется слово , т. е. осуществ1ггся логическая операция конъюнкции. Заметим, что в том же такте записи можно прорегеиерировать число b в ячейке 42, подав

на шину 32 отрицательный импульс полутока, 1ак как в ячейке 42 осуществится конъюнкция числа с «единицами, оставшимися там после считывания ячейки 42 с инверсией; таким образом, здесь в такте записи происходит выполпение логических операций сразу в двух адресах.

Остановимся несколько подробнее на выполнении в предлагаемом устройстве логических функций в нескольких ячейках (адресах)

одновременно. Если в такте считывания считать число b с некоторой ячейки, то, подавая его в такте записи по выбранным разрядным шинам (например, по шинам 35 в каждом разряде) с помощью положительных импульсов

полутоков и подавая положительные импульсы полутоков по выбранным словарным шинам (шины 31, 32, 33, 34), получим выполнение в соответствующих ячейках (ячейках 40, 42, 44, 46) операции дизъюнкции числа b с в ячейках 40, 42, 44, 46 были записаны нули, то в описанном выше случае осуществится операция «разветвления информации, так как происходит запись числа одновременно в несколько адресов. Следует заметить, что, так как в .предлагаемом устройстве используется схема МОЗУ системы 2,5 D с реверсом разрядного тока в зависимости от адреса, то, если описанная выше операция получения дизъюнкции в нескольких адресах производится с ячейками 41, 43, 45, 47, необходимо в такт записи по словарным шинам 31, 32, 33, 34 подать положительный импульс .полутока, а в разрядную шину 35 - отрицательный импульс полутока. В предлагаемом устройстве возможно также выполнение различных операций в нескольких адресах одновременно. Действительно, возбуждая в такте записи разрядные шниы 35 положительными импульсами полутоков в зависимости от кода числа b и подавая в словарные шины 31, 32 положительные импульсы полутоков, а в шины 33, 34 - отрицательные, получим в ячейках 40 и 42 выполнение операции дизъюнкции числа b с содержимым ячеек 40 и 42 ,со ответствен но и в ячейках 45 vi 47 - конъюнкцию числа b с числами, хранящимися в этих ячейках; в правильности этого можно убедиться, если рассматривать каждую из этих ячеек и нроходяшие через нее словарную и разрядную шины в отдельности и сравнить эти случаи с описанными выше операциями получения дизъюнкции и конъюнкции в одной ячейке. Дополнительно отметим, что при считывании иескольких ячеек (одних с инверсией, других - без инверсии) также возможно получение различных логических операций, так как лри этом на шине чтения оказывается дизъюнкция чисел, считанных с этих ячеек; причем числа, считанные с инверсией, войдут в вырасжение дизъюнкции с инверсией. Однако необходимо учесть, что при таком считывании возможны случаи, когда э.д.с. «единиц в шине чтения будут направлены встречно и усилители чтения могут не сработать. Эти случаи можно учесть заранее, зная расположение шины чтения относительно разрядны.х и словарных шин. В предлагаемом устройстве количество ячеек, к которым может одновременно произведено обращение (и в такте считывания и в такте записи) с целью выполнения в них логических операций, определяется количеством формирователей 16, так как .каж.дый из них подключен к своей словарной шине, а также мощностью ключа 25, через .который при выполнении логических операций в нескольких адресах одновременно проходит суммарный ток словарных шин. Так как количество оборудования в системе разрядной дешифрации в МОЗУ системы 2,5 D нропорн.ионально числу разрядов, то дополнительное увеличение количества одновременно опрашиваемых ячеек за счет возбуждения двух и более разрядных шин одновременно в каждом разряде представляется нерациональным. При работе МОЗУ в режиме заноминающего устройства выбор разрядной шины производится дешифраторами 7, 8 и 9, а при работе МОЗУ в режиме выполнения логических функций выбор разрядной шины происходит путем непосредственного запуска уже имеющихся в обычном МОЗУ формирователей 10 и ключей У/ по управляющим шинам 17, 18, 19, 20, 21. На основании методов выполнения логических функций, предлол енных выше, можно синтезировать алгоритмы сложения двух чисел с последовательной реализацией переносов, с.м. табл.

„. I O i-конец:

Контроль p- I YOTb одна 1 переход к та.кту 1.

В таблице обозначены: s-сумма по модулю 2; p - слово переносов; pi () - слово (аДЬ), сдвинутое на разряд влево; в нечетных тактах (/i, 2i)

происходит считывание информации с ячеек на регистр числа 13, в четных тактах ( h,

22) производится зались с регистра числа

в выбранную ячейку (ячейки). Как видно из таблицы, для осуществления данного алгоритма сложения необходимы пять ячеек (ячейки 40-44); в три из них (40, 42, 44) предварительно записывается одно слагаемое-число а и Б две другие ячейки (41 и 43) записывается другое слагаемое - число Ь. В таблице указаны полярности импульсов формирователей, Бозбуждаюидих словарные и разрядные шины в определенные моменты времени (такты), по этим импульсам можно составить .программу управляющему устройству; приведено изменение информации в ячейках, происходящее с каждым тактом, а также приведена информация, поступающая в регистр чисЛа в такте считывания - для облегчения контроля за правильностью получаемых .промежуточных результатов.

Вычисление суммы сводится к нахождению суммы S по модулю 2, определяемой в такте 82, и слова переносов р , определяемого к такте 22; в такте 4i необходимо .произвести сдвиг слова иереносов на один разряд влево, для чего в этом такте подается стробирующий сигнал 28 (см. фиг. 1), при этом ииформация с усилителей чтения 12 данного разряда переписывается иа формирователи 14 соседнего слова разряда регистра числа 13. В такте 4i происходит также контроль слова переносов и при наличии хотя бы одной единицы в слове переносов стробирующий сигнал 28 производит запуск усилителя контроля 29, который посылает сигнал в управляющее устройство 22 для направления алгоритма после такта 42 иа формироваиие такта /i и продолжеиие вычисления суммы; в случае, если слово иереиосов равио нулю, то алгоритм направляется на окончание сложения. Окончательный результат сложения оказывается в ячейках 41 и 43.

Аналогично возможно построение алгоритма сложения со .сквозным переносом, для реализации которого необходимо применить известные соединения в системе усилителе чтения и регистра числа, которые на фиг. 1 не 1оказа 1ы.

Выполнение операций сложения двух чисел и сдвига слова позволяет осуществить выполнение иа матрицах МОЗУ системы 2,50 и других о.пераций - умножения, деления и нр., при этом основную часть оборудования предлагаемого вычислительного устройства составляет однородное оборудование .МОЗУ.

Следующим щагом является распространение и на управляющее устройство требования о реализации его иа однородном оборудовании. Эта задача легко решается с использоьаннем построения управляющего устройства

по одному из известных способов микропрограммирования, когда микрокоманды - слова управляющих сигналов - составляются в микропрограммы, хранимые в ячейках того же МОЗУ. Это дополннтельно позволяет менять

характер и набор операций вычислительного устройства программным иутем.

Предмет изобретения

Цифровое вычислительно-логическое устройство, содержащее магнитное оперативное запоминающее устройство (.МОЗУ), блок сдвига слов, блок управления, дешифраторы, формирователи, усилители, вентили, ключи и регистр числа, отличающееся тем, что, с целью повыпления быстродействия, и надежности устройства, в ием выход каждого реверсивного формирователя подсоединен к одному концу соответствующей словарной ПИ1НЫ, противоположные обьединеииые концы соседиих словарных шин подключены к реверсивным ключам, входы реверсивных формирователей и реверсивных ключей подсоединены к соответствующим выходам блока управления, входы ключей формирователей и вентилей, подсоединенных к выходам соответствующих ступеией разрядных дешифраторов, подсоединены также к соответствующим выходам блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА ПОЛНОТОЧНОМНАКОПИТЕЛЕ | 1971 |

|

SU289514A1 |

| УСТРОЙСТВО для ПАРАЛЛЕЛЬНОГО СУММИРОВАНИЯДВУХ ЧИСЕЛ | 1970 |

|

SU268498A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

| Логическое запоминающее устройство | 1971 |

|

SU443411A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Запоминающее устройство типа 2,5 д | 1981 |

|

SU999105A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО3 :1 Т ВФОН]] Я-И;ф'РТГЩ <" t- J J^^ '^ • i .• f S .„ J i, is i* | 1972 |

|

SU433541A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| Логическое запоминающее устройство | 1976 |

|

SU650103A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368643A1 |

Даты

1970-01-01—Публикация