1

Изобретение относится к области цифровой измерительной техники и может быть использовано в частотомерах и измерителях временных интервалов.

Известна пересчетная декада, состоящая из делителя на пять, каждая ячейка которого включает входной транзистор, триггера и схемы сброса. Однако для устойчивой работы на низких частотах (ниже нескольких мегагерц) необходимо формирование по амплитуде и длительности входных сигналов.

Цель изобретения - повышение устойчи.вости работы на низких частотах.

Указанная цель достигается тем, что коллектор выходного транзистора предыдущей ячейки делителя связан через резистор с коллектором входного транзистора лоследующей ячейки, а база выходного транзистора последней ячейки связана с входом триггера, выход которого подключен к -шине выходных сигналов.

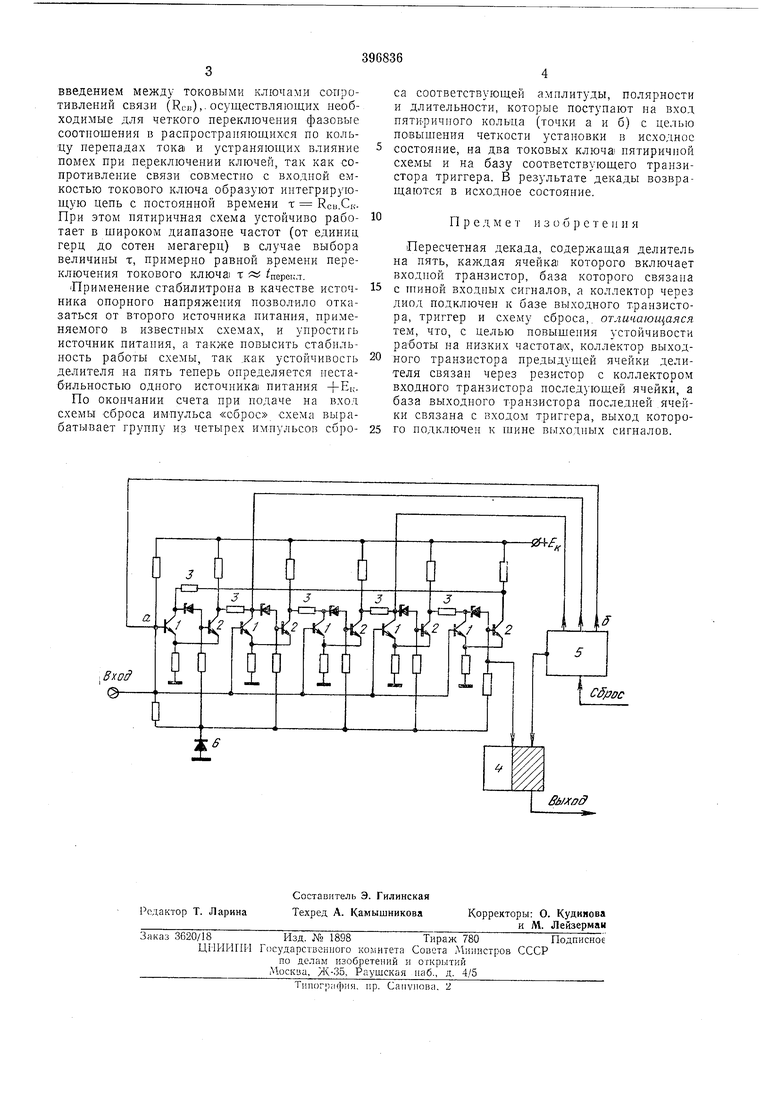

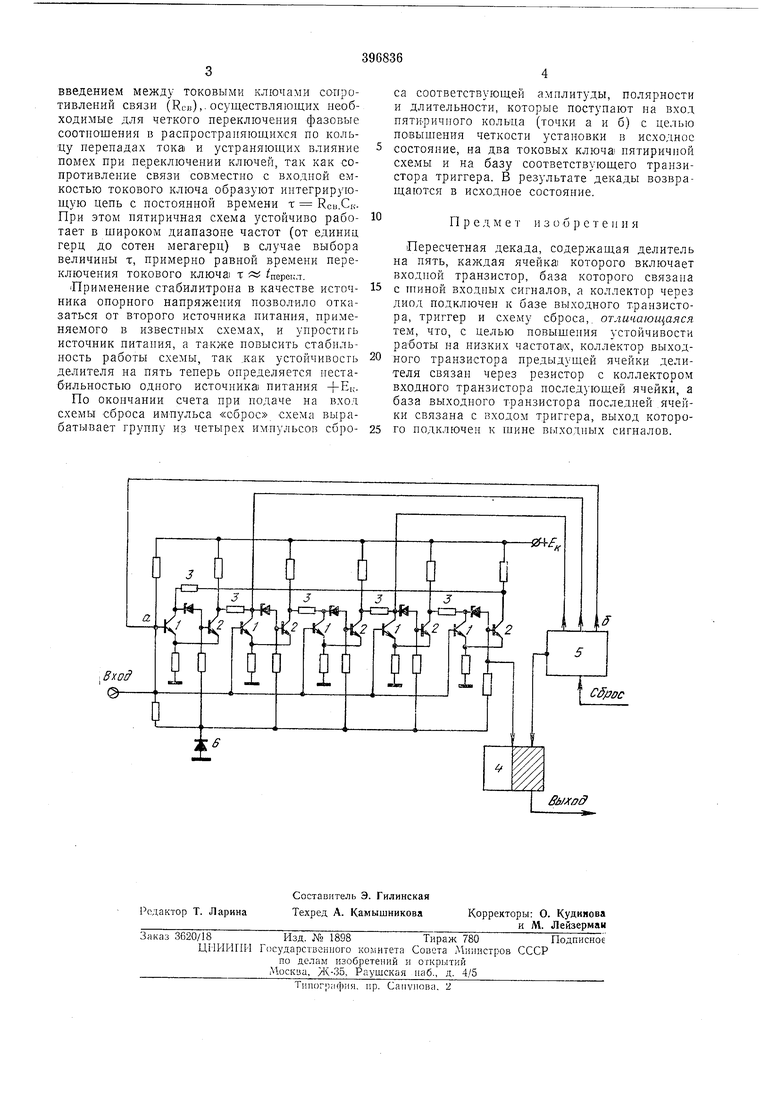

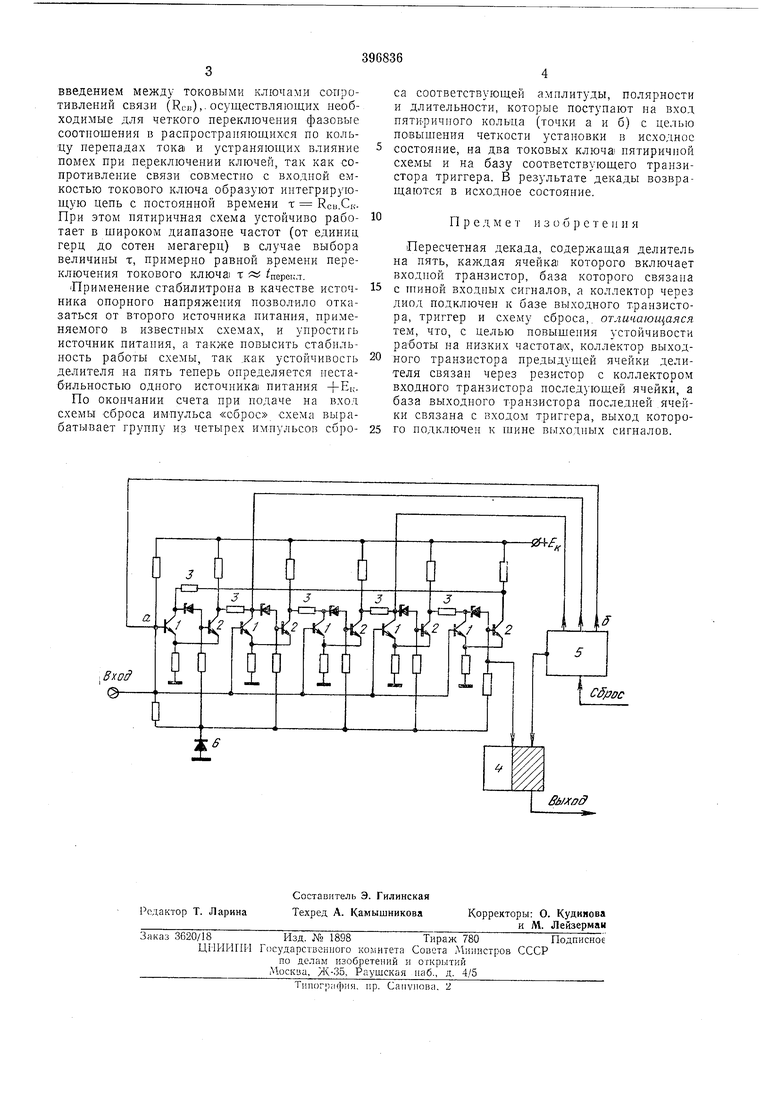

Схема предлагаемой пересчетной декады приведена на чертеже.

Она содержит входные транзисторы / токовых ключей, выходные транзисторы2 токовых ключей, сопротивления связи (RcB.) 3, двоичную ячейку 4, схему сброса 5, стабилитрон б в цепи опорного напряжения.

Делитель на пять выполнен по кольцевой схеме на пяти токовых ключах на транзисгоpax / и 2. Связь выходного транзистора 2 предыдущего ключа с входным транзистором / последующего осуществляется через резисторы связи 3 (RcE.). Выход делителя на пять связан со счетным входом триггера 4.

Схема сброса 5 соединена со входом делителя (точки а и б) с двумя токовыми ключами пятиричного делителя и со входом сброса триггера 4.

Стабилитрон 6 включен между шиной, к которой подключены через резисторы базы выходных транзисторов 2, токовых ключей, и корпусом прибора.

Входной сигнал синусоидальной или импзльсной формы любой полярности поступает на базы всех входных тринзисторов токовых ключей пятиричного делителя. В исходном состоянии три ключа за:крыты, а два других открыты. С поступлением входного сигнала такое состояние начинает последовательно перемещаться от одних ключей к другим, в результате чего при поступлении пятого входного сигнала на выходе пятиричного устройства появляется сигнал, опрокидывающий двоичную ячейку. После десятого входного сигнала вся схема занимает первоначальное положение.

При работе на низких частотах (в диапазоне от единиц герц до нескольких мегагерЦ) устойчивость пятиричной схемы достигается

введением между токовыми ключами coTipoтивлений связи (RCB),. осуществляющих необходимые для четкого переключения фазовые соотношения в распространяющихся по кольцу перепадах тока и устраняющих влияние помех при переключении ключей, так как сопротивление связи совместно с входной емкостью токового ключа образуют интегрирующую цепь с постоянной времени т ROU.CKПри этом пятиричная схема устойчиво работает в щироком диапазоне частот (от единиц герц до сотен мегагерц) в случае выбора величины т, примерно равной времени переключения токового ключа т Я:; /перекл.

Применение стабилитрона в качестве источника опорного напряжения позволило отказаться от второго источника питания, применяемого в известных схемах, и упростить источник питания, а также повысить стабильность работы схемы, так .как устойчивость делителя на пять теперь определяется нестабильностью одного источника) питания +Ei;.

По окончании счета при подаче на вход схемы сброса импульса «сброс схема вырабатывает группу из четырех импульсов сброса соответствующей амплитуды, полярности и длительности, которые поступают на вход пятиричного кольца (точки а и б) с целью повышения четкости установки в исходное состояние, на два токовых ключа нятиричной схемы и на базу соответствующего транзистора триггера. В результате декады возвращаются в исходное состояние.

П р е д м е т изо б р с т е и п я

Пересчетная декада, содержащая делитель на пять, каждая ячейка которого включает входной транзистор, база которого связана

с П1ИНОЙ входных сигналов, а коллектор через диод подключен к базе выходного транзистора, триггер и схему сброса,, отличающаяся тем, что, с целью повыщеиия устойчивости работы на низких частотам, коллектор выходного транзистора предыдущей ячейки делителя связан через резистор с коллектором входного транзистора последующей ячейки, а база выходного транзистора последней ячейки связана с входом триггера, выход которого подклЕОчен к щине выходных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Кольцевой делитель частоты с четным коэффициентом деления | 1972 |

|

SU437228A1 |

| Пересчетная декада | 1983 |

|

SU1112574A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| МНОГОСТАБИЛЬНЫЙ ТРИГГЕР | 1973 |

|

SU453804A1 |

| Стабилизированный конвертор | 1979 |

|

SU892425A1 |

| КОЛЬЦЕВАЯ ПЕРЕСЧЕТНАЯ СХВЛ\А | 1973 |

|

SU365844A1 |

| Транзисторный ключ | 1987 |

|

SU1422393A1 |

| ВАТТМЕТР | 1971 |

|

SU432403A1 |

| Источник питания с комплексной защитой | 1986 |

|

SU1325444A1 |

| РЕЛЕ ВРЕМЕНИ | 2002 |

|

RU2208259C1 |

г}4-н-|

Авторы

Даты

1973-01-01—Публикация