1

Известные ватт1мет1ры, содержащее преобразователь постоянного напряжения .в частоту следаваиия имтаульсав, генератор стабильного тока с интегрирующи1м конденсатором, пороговое устройство, входной усилитель, генератор тактовых им-пульсов, триггер, ключ «сб.роса, цифровые декады и источники стабилизированного наиряжания, хара ктеризуются сравнительно высо.кой погрешностью диowpeTHOCTH, сложностью схемы « низкой надежностью.

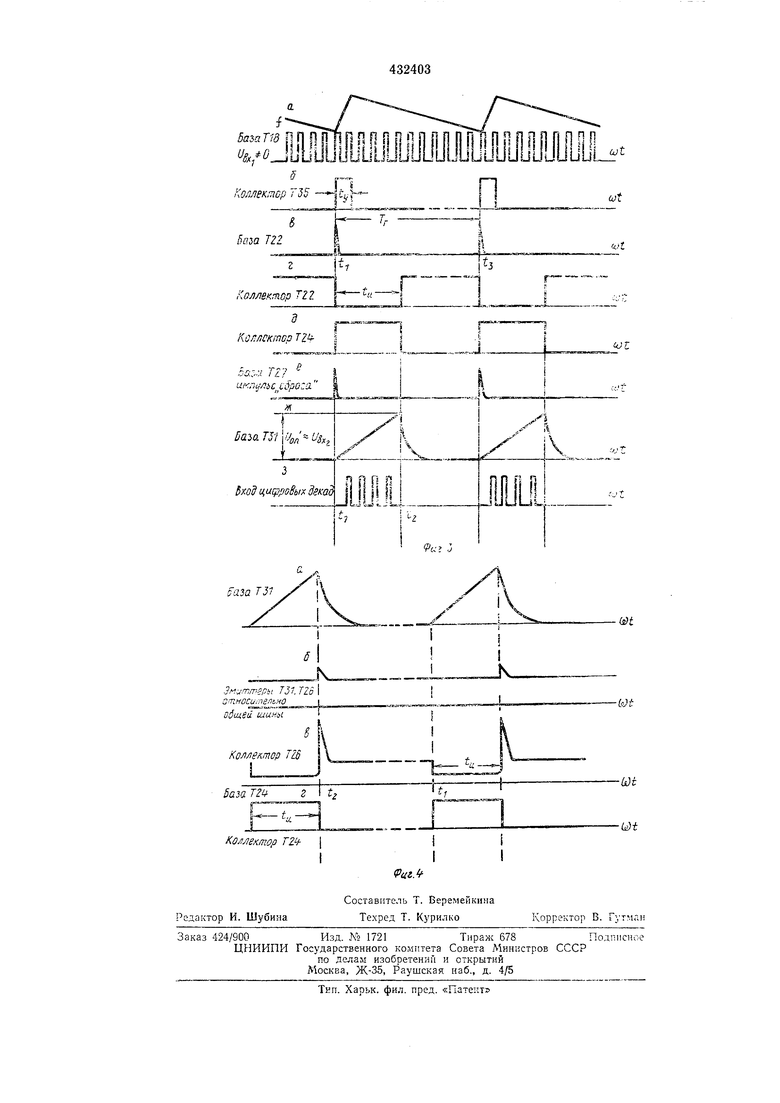

Для уменьшения л отреши ост и диокретност и, у1Прош,ения схемы и повышения ее нааежности в пре:длагаемом ваттметре выход преобразователя напряжения через диод подключен к входу «очет цифровых дакад, а через резистор - к управляюшей базе тран31истора генератора та(ктовых импульсов, которая через стабилитрон -присоеаинена к выходу упомянутого генератора, соединенного через конденсатор с базой одиого из транзисторов триггера, коллектрр которого подключен « входу «счет декад, причем база второго транзистора три ггера цриооединена к коллектору TpaiH3wcTOpa входного усилителя, а коллектор его через конденсатор сое,дииен с базой транзистора ключа «сброса цифровых декаа, че(рез диод и резистор - с мин тсо-м источника питания и через диады - с коллектором транзистора генератора тока, эмиттер и

2

база которого присоединены к плюсу соотеетствующнх источников питания, а коллектор - к одной из интегрирующего «ондеисатора и к базе транзистора порогового устройства.,

Кроме того, для уменьшвн1ия зоны нечувстБительности канала на1пряжения, эмиттер и коллектор траизистора порогового устройства соединены соответственно с эмиттером и (Коллектором входного транзистора и подклю4eiHbi: эмиттеры - к магаусу источника нитания, а коллекторы - к плюсу, причем канал напряжения ваттметра (динен к базе вхадного транзистора, соединенного через резистор с обш,ей шиной, куда та.кже присоединена вторая обкладка интегрирующего конденсатора.

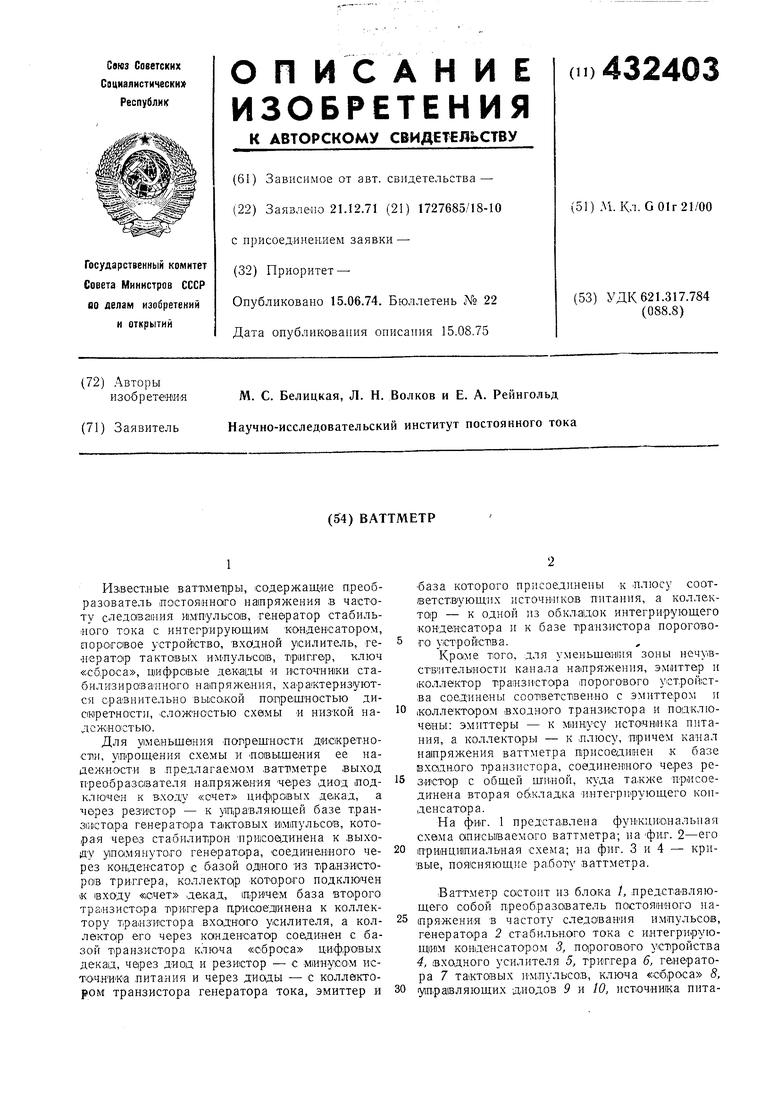

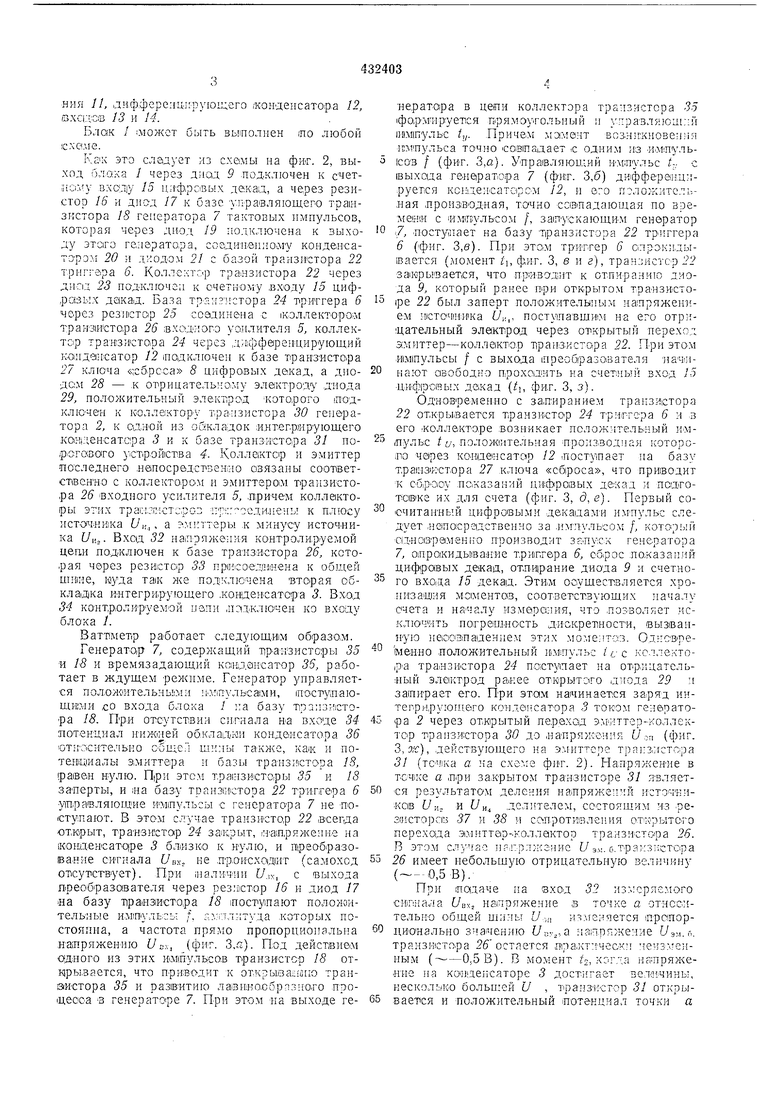

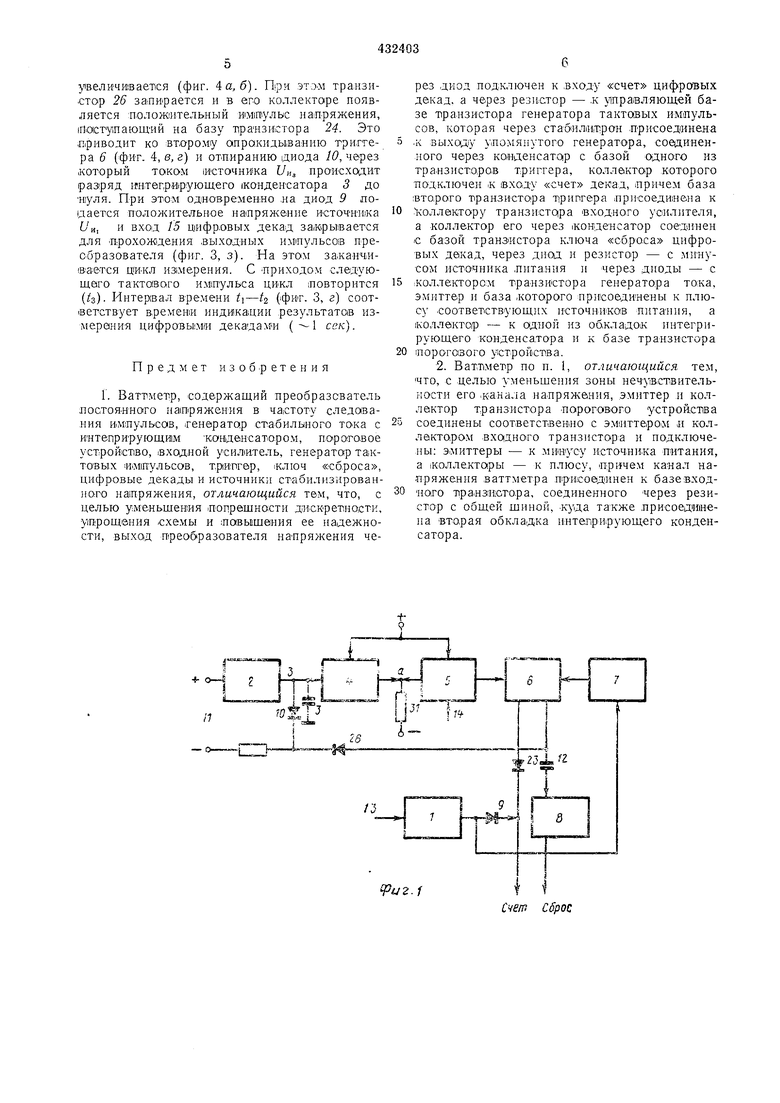

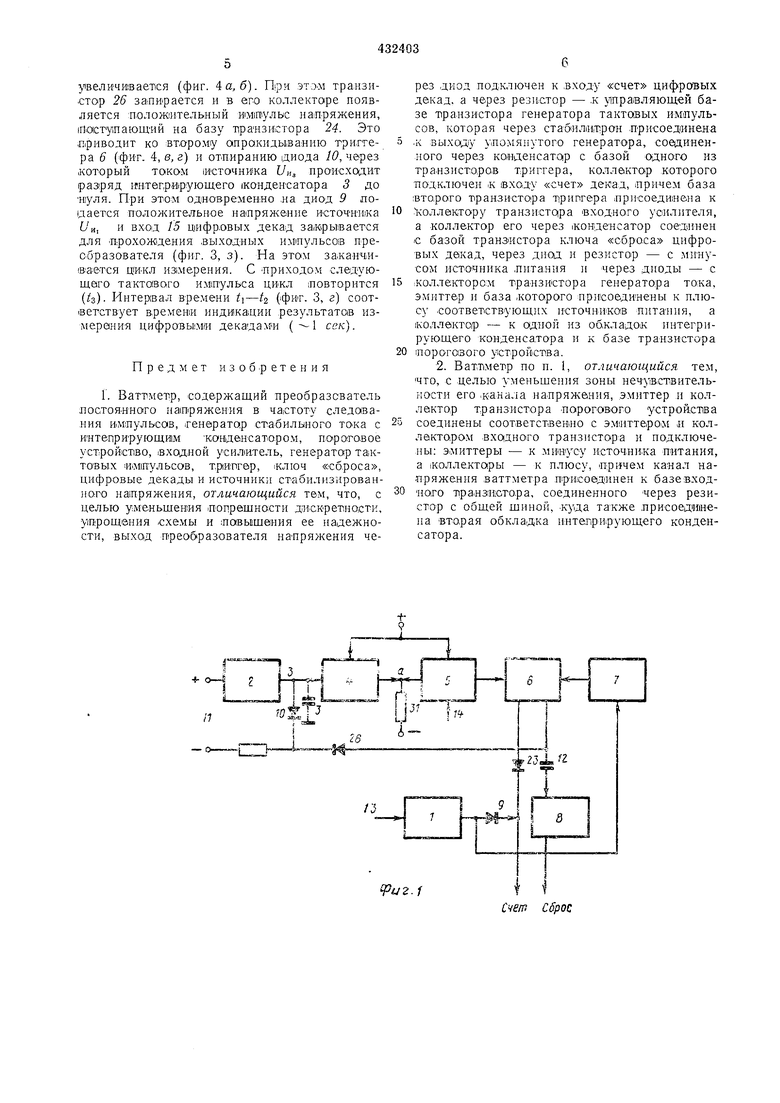

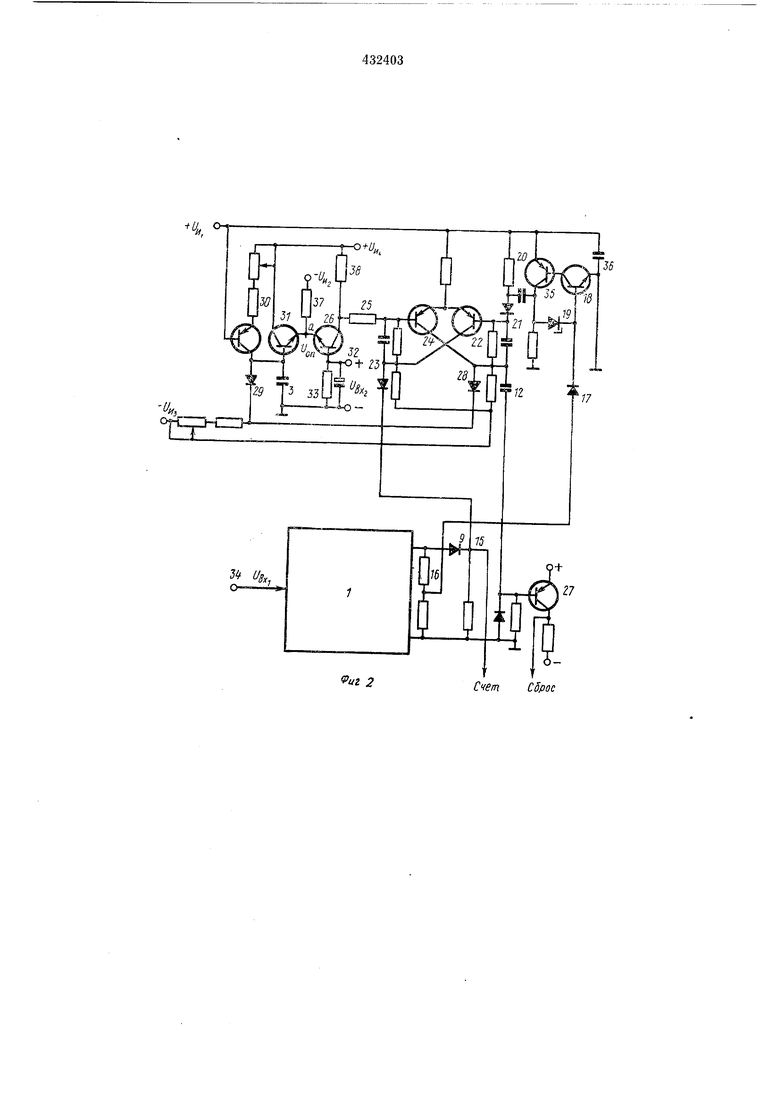

На фиг. 1 представлена функциональная схема описываемого ваттметра; на фиг. 2-его принципиальная схема; на фиг. 3 и 4 - кривые, поясняющ е работу ваттметра.

Ваттметр состоит из блока /, представляющего собой преобразователь постоянного иапряжения в частоту следования импульсов, генератора 2 стабильного тока с интегрирующий конаенсатором 3, порогового устройства 4, входного усилителя 5, триггера 6, генератора 7 TaiKTOBbix идшульсов, ключа «сброса 8,

(управляющих аиодов 9 и W, источника niiTaния и, анф.фереицПрующего жонденсаторл 12, Bxci;(:c.B 13 и 14.

Блок / iMOKCT быть вьшолиен по любой

ICXCIMG.

Ка-х это сладует из схемы на фиг. 2, выход бло:ха / через диад 9 лодкл очен к счетjiCL.y Bxc.iiy 15 ц;|ф, декад, а через резистор 16 и ди&д 17 к базе управляющего тра1изистора /S генератора 7 тактовых импульсов, которая через диод 19 подключена к выходу ЭТС1ГО генератора, соадинепиолгу конденсатором 20 и диодом 21 с базой транзистора 22 rpHrreipa 6. Коллехтс.р транзистора 22 через ДИС1Д 23 нодключеи к счетному входу 15 циф,разь:х дакад. База трдлзистора 24 Третгера 6 через (р 25 соэдиие-на с коллектором траи31нсто.ра 26 входного усилителя 5, коллекTCip транзистора 24 через „ч иффереищирующий ко1:1де1исатор 12 подключен к базе транзисто.ра 27 ключа «сброса 8 нифровых декад, а диодам 28 - ,к отрнцательно1му электроду диода 29, ноложительный электрод кото.рого подклю-чен к коллегктору транзистора 30 генератора 2, к одной из обкладок :интегр ирующего KOHineHcaTcipa 3 и к базе транзистора 31 но.pioroBoro }|СТ|роЙ1ет ва 4. Коллектор и эмиттер последнего напосрвдствеино связаны соот1ветCTiBQHHO е коллектором и эмиттеро м транзистора 26 входного усилителя 5, .причем коллакторы этих тра1нзмстс,роз т р:::: оеди. к плюсу Vк,,, а ,миттеры ,к минусу источника /„,. Вход 32 на1ирлже;1ия контролируемой цепи подключен к базе транзистора 26, которая через резистор 33 прксоедакнена к общей шн(ие, иуда та1К же подключена вторая обкладка интегрирующего .кондеисатора 3. Вход 34 контролируемОЙ пани ,ппл,.ключен ко входу блока 1.

Ватт мет|р работает следующ.им образо,м.

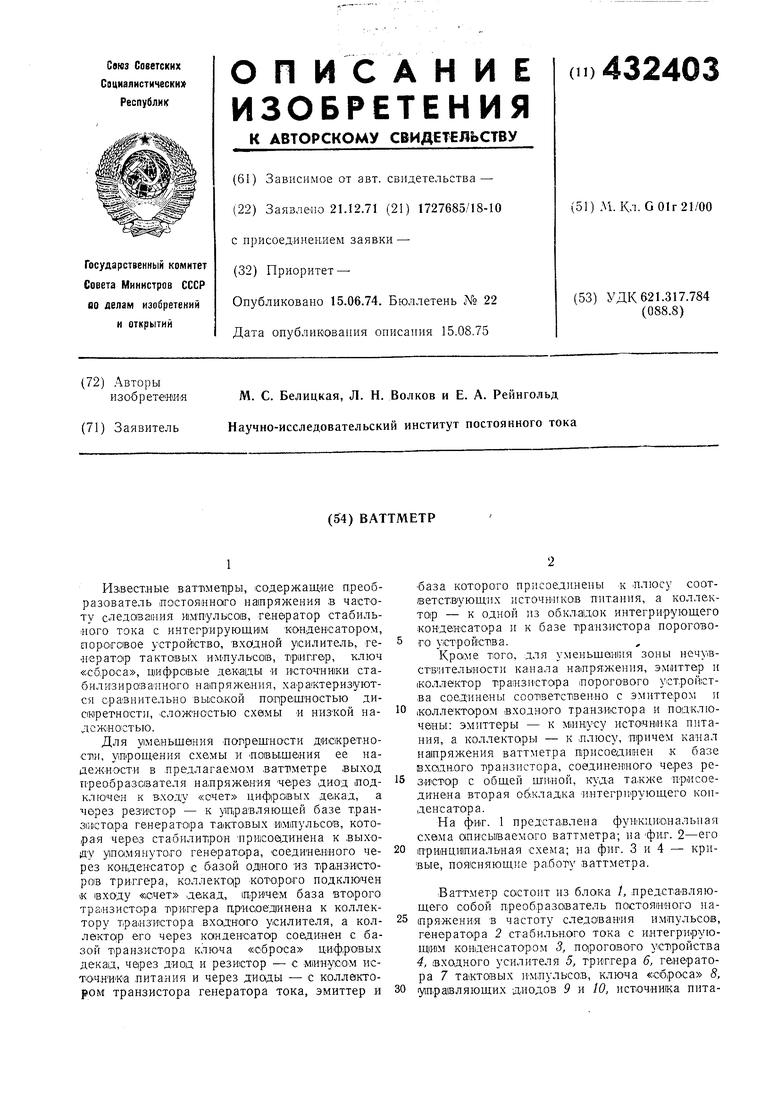

Генератор 7, содержащий тра нзисторы 35 и /5 и времязадающий конр.ансатор 36, работает в ждущем режнме. Генератор управляется нолож1ительнь 1ми 1М|Пульса1ми, поступающими со входа блока / на базу транзистора 18. Прн отсутствии сигнала ва входе 34 потенциал ниж1ней обкладми конденсатора 36 oтн эcитeльнo общел шины также, как н нотен1Ц1иалы амиттара и базы транзистора 18, (равен нулю. П|ри этом тра1нзисторы 35 и /5 зачтерты, и 1на базу транз1И1Стора 22 трнпгера 6 управляющие импульсы с генератора 7 не ностунают. В этом случ ае транзистор 22 всегда OTKipbiT, транзистор 24 за1Крыт, Напряжеане на iKOHaencaTqpe 3 бл1изко к нулю, и преобразование сигнала Uт, не ,прОИСход1ит (самоход отсутствует). При наличии /зх, с выхода преобразователя через резистор 16 и диод 17 «а базу Т1ранзистора 18 поступают нолож1Ительные имп ль:сы f, :,;плитуда .которых постоянна, а частота прямо пропорциональна НапряжеНИЮ t/si, (фиг. З.я). Под действием о|дпого из этих илкпульсо.в транзистор 18 открывается, что приводит к oTKpbiBai-iiiiiO транiSiHCTOpa 35 и развитию лавинообрпзпото нрощесоа в renepaTOipe 7. При этом iia выходе генератора в цепи коллектора транзистора 35 (формируется прямоугольный и уг1равля}от;;й п-вмпульс /у. Причем мэмент воз.никновеи 1я П1пульса точно совпадает с одним из .иляпульIC03 / (фиГ. 3,а). Управляюодий импульс tr/ с выхада генератора 7 (фит. 3,6) ди|ффере1нди.руется конленсатар.ом 2, и его псложитсль ная лроиз водная, точно сов падаюидая по времени с 1ИМ1ГЕульсом /, запускающим генератор ,7, .поступает на базу транзистора 22 триггера 6 (фиг. 3,в). При этом трнпгер 6 опроки.дывается (момент /ьфиг. 3, е и г), тран;; 1стср за крывается, что ир;ивод;ит к отпиранию диода 9, который ранее при открытом транзисто|ре 22 был заперт положительным напряжением асточптрка L/,,,, поступавшем на его отрицательный элвктрад через открытый переход амиттер-коллектор транзистора 22. При этом .импульсы / с выхода преобразователя начИнают оБободно прохо дить на очетнгый вход 15 ц.иф|р01ных декад (/ь фиг. 3, з).

Одновременно с запиранием транзистора 22 открывается транзистор 24 триггера 6 и в его коллекто.ре .возникает ноложительный им(Пульс / у, положительная произ.водная котороino через конценсатар 12 поступает на базу TpaiH.3iKCTopa 27 ключа «сброса, что приводит к c6ip0ioy наказаний цифровых декад и подготовке их для счета (фиг. 3, д,е. Первый со«считанный цифровыми .декадами импульс следует .не по;сре|дственно за .1 Мнульсом /, кото-рый С1ДН01Врамен|;о производит запуск генератора 7, опрокидьЕванне триггера 6, сброс .но.казаиий цифровых декад, отл.и1рание диода 9 и счетного входа 15 декад. Этим осуществляется хронизащия м.С1ментав, соответствующих началу счета и началу измарсоия, что позволяет исключить HOirpenjHOCTb дискретноети, вызваиную 1 бС10В1па1лением этих момеитогз. Од-ЮВременно .положительный импульс i с с коллектоipa транзистора 24 поступает на отр.ицатсль:ный электрод ранее открытого диода 29 и запирает его. При этом начинается заряд интегрирующего конде нсатора 3 током гене1ратора 2 через открытый переход э.МИттер-Коллектор тра гзи1стора 30 до напряжения (7оп (фиг. 3, a-i:), .действуюидего на эмиттере транзигстсра 31 ( а на фиг. 2). На.пряжение в тсч1ке а при за.крытом транзисторе 31 являет.ся результатом деления напряжений источников UK, и и .дел гтелем, состоящим из .резсиеторспз 37 и 38 и сопроти1вления oT vvphiToro перехода эмиттар-.коллактор транзистора 26. В этом случае пр:Прлжз:ние /эм. G.транзистора

26 имеет небольщую отрицательную величину

(0,5В).

При псааче на вход 32 из:-;срясмого свпнала Ue-i, напряжение s точке а относительно Общей шииы У-;,, изменяется пропордионально зна1чению f/,v,,a иа|прпжение L/эм.п. транзистора 26остается пра.ктичеок неизл-енным (-0,5В). В .момент /2, когда напряжение на ко-1Н|денсаторе 3 дост1 гает вел.;н-чины, несколько большей U , транзистор 31 открывается и положительный потенциал точки а

увеличивается (фиг. 4 а, б). При эт,м транзистор 26 заливается и в его коллекторе появляется положительный имтульс напряжения, |Пасту1иающИЙ иа базу транзистора 24. Это Л(риводит ко второму оиракидыванию триггера 6 (фиг. 4, е, г) и отпиранию диода /О, через который токОМ 1источни ка U,,., про-исхоаит интегрирующего 1кондеисато.ра 3 до н|уля. При этом одновременно ла диод 9 поцается положительное на1прял ение источнн/ка 6и, и вход 15 щифр.овых декад закрывается для прохождения выходных им1иульсо)з преобразователя (фиг. 3, з). На этом за1канчив ается цикл измерения. С Приходом следующего тактавого импульса цикл повторится (/з). Интервал времени ti-/2 (фиг. 3, г) соответствует в,ремен1И инди1кации .результатов измерения цифровыми декадами ( сек).

Предмет изобретения

Г. Ваттметр, содержащий преобразователь лостоЯНного наеряжения в частоту следавания имшульсов, генератор стабильного тока с Интеприрующи1м конденсатором, пороговое устройство, входной усилитель, генератор тактовых ;ИМ1пульсов, триггер, «люч «сброса, цифровые декады и источники стабилизированного напряжения, отличающийся тем, что, с целью уменьщевия полрещности дискретности, упрощения схемы и лавышения ее надежности, выход преобразователя напряжения через диод подключен к входу «счет цифровых декад, а через резистор - .к управляющей базе транзистора генератора тактовых импульсов, которая через стабИЛ1И|Трон присоединена а выходу упомянутого генератора, соединенного через коиденсатор с базой одного из транзисторов триггера, коллектор которого подключен .к 1ВХ01ду «счет декад, причем база второго транзистора триггера лрисоедииена к коллектору транзистрра входного усилителя, а коллектор его через «онденсатор соединен с базой транЗИстора ключа «сброса цифровых декад, через диод и резистор - с минусом источника литания и через диоды - с :КоллекторО:М транзистора генератора тока, эмиттер и база .которого присоединены к плюсу соответствующих источни1КО В питания, а коллектор - к одной из обкладок интегрирующего конденсатора и к базе транзистора

порого1вого устройства.

2. Ваттметр по н. 1, отличающийся тем, ЧТО, с целью уменьщения зоны нечуВ|Ствительности его -канала напряжения, эмиттер и коллектор транзистора лорогового устройства

соединены соответственно с эм1итте1ро.м ,и коллекторо.м входного транзистора и подключены: э.миттеры - к мииусу источника питания, а (Коллекторы - к плюсу, лричем канал напряжения ваттметра присоединен к базевходиого транзистора, соединенного через резистор с общей щиной, Куда также .присоединена вторая обкладка интегрирующего конденсатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| Преобразователь напряжения в длительность импульсов | 1990 |

|

SU1785071A1 |

| РЕЛЕ ВРЕМЕНИ (С ВЫХОДОМ НА СИМИСТОРЕ) | 1992 |

|

RU2130213C1 |

| Устройство для фазового управления тиристорным преобразователем | 1982 |

|

SU1035772A1 |

| Устройство дистанционного управления угольным комбайном с пневмоприводом | 1984 |

|

SU1190029A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| СИСТЕМА ЗАЖИГАНИЯ | 1996 |

|

RU2129663C1 |

| Преобразователь напряжения в частоту следвания импульсов | 1973 |

|

SU454685A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2012 |

|

RU2506598C1 |

, L I ю

U2.1

Сче1г, Сброс

иг 2

Счет СЗрос

Авторы

Даты

1974-06-15—Публикация

1971-12-21—Подача