1

Настоящее изобретение относится к области автоматического регулирования и колтроля и может быть использовано, например, в устройствах автоматического удравлен-ия угловым .положением гироприборов, рулевых органов и антенн летательных аппаратов и судов.

Известны цифровые следящие системы, содержащие последовательно соединенные ци-фровую вычислительную машину н регистрсчетЧИк, выход которого соединен с перБьгм входом сравнивающего устройства, второй вход которого через -последовательно соединенные формирователь ф.азовых -имлульсов и фазовращатель подключен к выходу объекта релулирования, первый н второй выходы сравнивающего устройства подключены к соответствуюидам входа1м преобразователя «код- напряжение, выход которого через последовательно соединенные усилитель и исполнительный орган подключе} ко входу объекта регулирования, и последовательно соэдиленпые генератор тактовых имлульсов и преобразователь «времешюй интервал-код.

Однако известные системы сложны и требуют значительных затрат времени для преобразования сигналов и вычисления раосогласавания, что вносит запаздывание в передачу информации в системе, ухудщает ее дина мические свойства.

С целью упрощения системы и повышения ее быстродействия система содержит триггер, схему «И и формирователь импульсов начальной установки, вход которого подключен

к обмотке возбуисдения фазовращателя, выход формирователя и;м1пульсав начальной установки соединен с лервьгм входом триггера, с другим входом преобразователя «временной интервал-код и с третьим входо м сравниваюи;его устройства, третий и четвертый выходы которого соадинены соответственно с третыим и четвертым вхадами преобразователя «временной интервал-код, выходы которого подключены к соответствующи м вхс«да м

преобразователя «код-налряжеьгие, второй вход триггера подключен к выходу регистрасчетчика, другой вход которого соединен с выходом схемы «И, входы которой подключены к выходам соответственно триггера и генератора тактовых импульсов; сравнивающее устройство содержит четыре схемы «И, два триггера и схему «ИЛИ, и второй входы которой соединены соответственно с первыми и вторыми вхада ми первого триггера и сравнивающего устройства, выход схемы «ИЛИ соединен с первыми входами первой и второй схем «И, второй вход первой схемы «И подключен к первому выходу второго триггера, второй выход которого соединен со

вторым входом второй схемы «И и с третьим выходом сравнивающего устройства, с четвертым выходом которого соединен выход второй схемы «И, выход первой схемы «И подключен к .первым входам третьей и четвертой схем «И и второго триггера, второй вход которого соединен с третшм входом сравнивающего устройства, первый и второй выходы первого триггера соединены со вторыми входамд соответственно третьей и четвертой схем «И, выходы которых подключены соответственно к первому и второму выходам сравнивающего устройства, а преобразователь «временной интервал-код содержит схему «ИЛИ, последовательно соединенные ячейки пересчетной схемы и схемы «И, три входа первой из которых соединены соответственно с первым и третьим входами иреобразователк «временной интервал-код и с первым выходом последней ячеьки пересчетпой схемы, другой вход которой подключен к первому входу схемы «ИЛИ и к другому входу преобразователя «временной интервал-код, выход ле-рвой схемы «И соодинеи с первым входом первой ячейки пересчетной , выход схемы «ИЛИ подключен к другим входам всех, KpOiMe последней, ячеек пересчетной схемы, другой вход схемы «ИЛИ соединен с выходол предпоследней ячейки пересчетной схемы, второй выход последней ячейки пересчетиой схемы и выходы остальных ячеек пересчетной схемы соединены с первы-ми входами соответствующих схем «И, вторые -входы которых подключепы к четверто му входу преобразователя «временной интервал-код, а выходы - к его соответстБующ1Им выхода м.

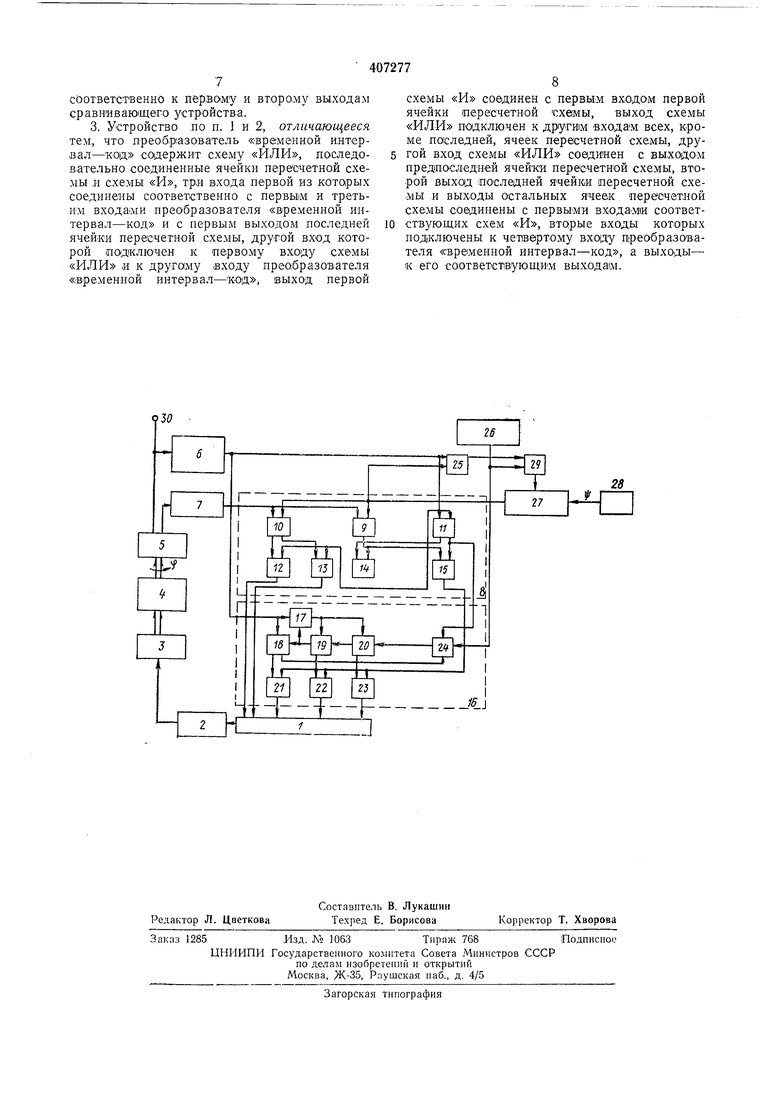

На чертеже приведена блок-схема предлагаемой системы, содержащей: преобразсеатель «код-напряжен ие 1, усилитель 2, И1ггшлнительный орган 3, объект регулирования 4, фазовращатель 5, формирователь импульсов начальной установки 6, фор мирователь фазовых импульсов 7, сравнивающее устройство S, содержащее схему «ИЛИ 9, триггеры 10, 11 1 схемы «И 12, 13, 14 и 75, преобразователь «временной интервал-код 6, содержащий схему «ИЛР 77, ячейки пересчетной схемы 18, 19 и 20 и схемы «И 21, 22, 23 и 24, триггер 25, генератор тактовых импульсов 26, регистр-счстчпк 27, цифровую вычислительную маш-ину (ЦВМ) 28, схему «И 29 и вход системы 30.

Работает система следующим образом. Через вход системы 30 па обмотку возбуждения фазоврап1.ателя 5 и на вход фор1миропателя 6 поступает .синусоидальное напряжение. Фор,1прователь 6 вырабатывает узкие импульсы начальной установки в моменты перехода через ПОЛЬ этого напря.жеиия. Импульсы начальной установки с выхода формирователя 6 поступают на обнуляю дие входыячеек 18, 19, 20 пересчетной схемы преобразователя 16, па входы триггеров 11 и 25 и устанавливают их в исходное состояние. Выходной спгиал триггера 11 при это.м поступает на вход схемы «И 14, а Иа входах cxeiM

«И 15 п 24 сигнал этого триггера отсутствует и схема 24 не пропускает тактовые импульсы генератора 26 на вход пересчетной схемы нреобразователя 16. Преобразователь 16 иа5 ходится в исходном состоян-ии.

Выходной сигнал триггера 25 поступает на вход схемы «И 29, которая начинает пропускать импульсы генератора 26 на вход регистра-счетчика 27, в котором записан обратный код задающего сигнала Ч из ЦВМ. Импульс конца заполнения регистра-счетчика является фазовым импульсом задающего сигнала Ч , а интервал времени Д/i между импульсом начальной з-становки и имп -льсам ко.ица

15 заполнения регистра-счетчика 27 пропорционален величине задающего сигнала Т

Фазовый импульс о-ггнала Ч с выхода репистра-счетчика 27 поступает на второй вход триггера 25, устанавливает его в состояние,

при котором его выходной сигнал на входе схемы 29 отсутствует п импульсы генератора 26 не проходят на вход регистра-счетчика 27.

Этот же и.мпульс поступает на входы триггера 10 и схемы «ИЛИ 9 сравнивающего устройства 8, на вторые входы которых через интервал времени А/2 после импульса начальной уста1ювли постЗпает фазовый импульс с формирователя фазовых импульсов 7, вырабатывающего узкие ямпульсы в моменты перехода через ноль выходного синусоидального напряжения фазовращателя 5, поступаюп,его на его вход.

Цри я|)ср и фазовый и.мпульс сигнала ф будет опережающим, а фазовый и.м5 пульс сигнала ф - отстающим друг относительио друга. Опережающий фазовый и.мпульс сигнала ср обратной связи устанавливает триггер 10 в состояние, при .котором его выходной сигнал поступает на в.ход схемы 12

и отсутствует иа входе схемы 13. С выхода схе.мы 9 этот опережающий импульс поступает на входы с.хем 14 и 15 и совпадает с сигналом триггера 11 на входах схемы 14. Схема 14 формирует импульс, который, .поступая иа

5 входы схем 12 ,и 13, совпадает с сигналам триггера 10 иа входах, схемы 12. Схема 12 формирует импульс зпака временного интервала рассогласования меж.ду фазовы.м;и импульсами при . Одновремеино импульс с

0 выхода схамы 14 поступает иа в.х:о.д триггера 11 }1 устанавливает его в состояипе, при которо.м его выходной сигнал поступает иа входы схем 15 и 24 и отсутствует иа входе схе.лгы 14. Через схему 24 и а вход пересчетпой

5 схемы преобразователя 16 начинают поступать .импульсы генератора 26, образуя па промежуточных выхо.дах пересчетной схемы двоИчно-кодовую «омбииацию сигналов.

Через время т А/1-Д г, пропорщюваль0 иое разности .между задающим сигналом и сигналом о братной связи ф, с выхода регистра-счетчика 27 через схему 9 на входы схем 14 и 15 поступает фазовый импульс задающего сигнала и совпа.дает с тригге5 ра 11 на входе схемы 15. Схема 15 нр.и этом

формирует иМПульс, который поступает на входы схем 21, 22, 23, на выходах которых будет сформирован код сигнала рассогласования системы в соотвеТСтвии с состояялем ячеек пересчетной схемы.

О-ПИсанный цикл рЯботы элементов систе:мы повторяется с частотой следования Нмпульсов начальной установки, равной частоте апорнаго на-пряжения фазовращателя 5.

При , работа системы аналогична описанной с той лишь разницей, что импульс знака рассогласования системы будет сформирован не на схеме 12, а на схеме 13.

Как известно, ,в системах а-втоматического регулирования диапазон пропорциональной зависимости сигнала управления от разности задающего сигнала и сигнала обратной связи ограничнвается некоторой величиной С.

В данной системе такое ограничение обеспечивается включением схемы «ИЛИ 17 между выходом предпоследней ячейки 19 пересчетной схемы преобразователя 16 и обнуляющими входами ячеек 19, 20 этой схемы и введениеМ соединения между «нулевым выходом ячейки 18 пересчетной схемы и одним из входов схемы 24. Причем заданное значение величины С определяется включением соответствующего количества ячеек нересчетной схемы.

Так, при (-ф-ср) С количество ячеек пересчетной схемы должно быть таким, чтобы в течение интервала времени тгА/- iy.. происходило заполнение соответстгзующего количества ячеек нересчетной схемы, исключая заполнения ее последней ячейки.

С в течение интервала времеПри :фни Т2 произойдет заполнение и последней ячейки 18. Импульс с выхода предпоследней ячейки 19 через схему 17 поступает на обнуляющие входы ячеек 19, 20 пересчетной схемы, устанавливает их в «нулевое, а ячейку 18 - в «единичное состояние. При этом выходной сигнал ячейки 18 поступает на один из входов схемы 24, который прекратит пропускание импульсов с генератора 26 на вход пересчетной схемы. Такое состояние преобразователя 16 будет сохраняться до момента поступлення фазового стоп-жмпульса большей из ср авниваемых величин на входы схем 21, 22, 23, с приходом которого произойдет считывание кода на схеме 21. ..

Код рассогласования поступает в преобразователь «код-напряжение, с выхода которого сигнал зшравления в форме постоянного илл переменного напряжения соответственно полярности фазы, опрэделяемой знаком временного интервала рассогласования системы, поступает через усилитель 2 иа исполнительный орган 3, приводящий объект 4 регулирования в положение, при котором сигнал фазовращателя 5 будет равен задающе му сигналу ЦВМ. При этом фазовые импульсы задающего сигнала н сигнала обратной связн будут совпадать во времени, а временной интервал разности т, код рассогласовання и напряжение управления исполнительным органом будут равны нулю. Система находится в согласованном состоянии.

Предмет изобретения

1. Цифровая следящая система, содерлсащая последовательно соединенные цифровую

вычислительную машину и регистр-счетчик, выход которого соединен с первым входом сравнивающего устройства, второй вход которого через последовательно соединенные формирователь фазовых импульсов и фазовращатель подключен к выходу объекта регулирования, первый и второй выходы сравнивающего устройства подключены к соответствующим входам преобразователя «код-напряжение, выход которого через последовательно соединенные усилитель и исполнительный орган подключен ко входу объекта регулирования, и последовательно соединенные генератор тактовых и.лшульсов и преобразователь «временной интервал-код, отличающаяся тем,

что, с целью упрощения системы н повышения ее быстродействия, она содержит триггер, схему «И и формирователь импульсов начальной установкн, вход которого подключен к обмотке возбуждения фазовращателя, выход

формирователя импульсов начальной установки соединен с первььм входом триггера, с другим входом преобразователя «временной интервал-1кад и с третьим входом сравнивающего зстройства, третий и четвертый выходы

которого соединены соответственно с третьи. и четвертым входами преобразователя «временной интервал-код, выходы которого подключены к соответствующим входам преобразователя «код-напряжение, второй вход

триггера подключен к выходу регистра-счетчика, другой вход которого соединен с выходом схемы «И, входы которой нодключены к выходам соответственно триггера и генератора тактовых импульсов.

2. Система по п. I, отличающаяся тем, что сравнивающее устройство содержит четыре схе.мы «И, два триггера и схему «ИЛИ, первый и второй входы которой соединены соотестственно с первыми и вторыми входами первого триггера и сравнивающего зстройства, выход схе.мы «ИЛИ соединен с первыми входами первой п второй схем «И, второй вход первой схемы «И подключе к первому выходу второго триггера, второй выход которого

соединен со вторым входом второй схемы «И и с третьим выходом сравнивающего устройства, с четвертым выходом которого соединен выход второй схемы «И, выход первой схе:iibi «И подключен к первым входам третьей

н четвертой схем «И н второго триггера, второй вход которого соединен с третьим входом сравнивающего устройства, первый н второй выходы первого триггера соединены со вторыми входами соответственно третьей и четвертой схем «И, выходы которых подключены

7

соответственно к первому и второ.му выходам сравнивающего устройства.

3. Устройство по п. 1 и 2, отличающееся тем, что преобр азователь «временной интервал-код содержит схему «ИЛИ, посутедовательно соединенные ячейки пересчетной схемы л схемы «И, тр.и входа первой из которых соедине ы соогветственно с первы1М и третьим входа1ми преобразователя «временной интервал-код и с первым выходом последней ячейки пересчетной схемы, другой вход которой подключен к первому входу схемы «ИЛИ и к другому :входу преобразователя «временной интервал-код, выход первой

схемы «И соединен с первым входом первой ячейки пересчетной схемы, выход схемы «ИЛИ подключен к другим входаМ всех, кроме последней, ячеек пересчетной схемы, другой вход схемы «ИЛИ соеди нен с выходом предпоследней ячейки пересчетной схемы, второй выход последней ячейки пересчетной схемы ,и выходы остальных ячеек пересчетной схемы соединены с первыми входа М1И соответствующих схем «И, вторые входы которых подключены к чет1ввртому входу преобразователя «временной интервал-код, а выходы- к его соответствующий выхода1м.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь код-угол | 1980 |

|

SU858053A1 |

| МНОГОКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU384115A1 |

| Калибратор фазовых сдвигов | 1982 |

|

SU1081564A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОД-УГОЛ | 1973 |

|

SU386476A1 |

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ СИГНАЛОВ НАДВОДНОЙ ЦЕЛИ В МОНОИМПУЛЬСНОЙ РЛС | 2004 |

|

RU2278397C2 |

| Двухотсчетный преобразователь кода в угол | 1975 |

|

SU549826A1 |

| Цифровая следящая система | 1977 |

|

SU682872A1 |

| Способ измерения амплитудного значения электрического сигнала | 1986 |

|

SU1441320A1 |

| Преобразователь код-угол | 1976 |

|

SU693416A1 |

Авторы

Даты

1973-01-01—Публикация