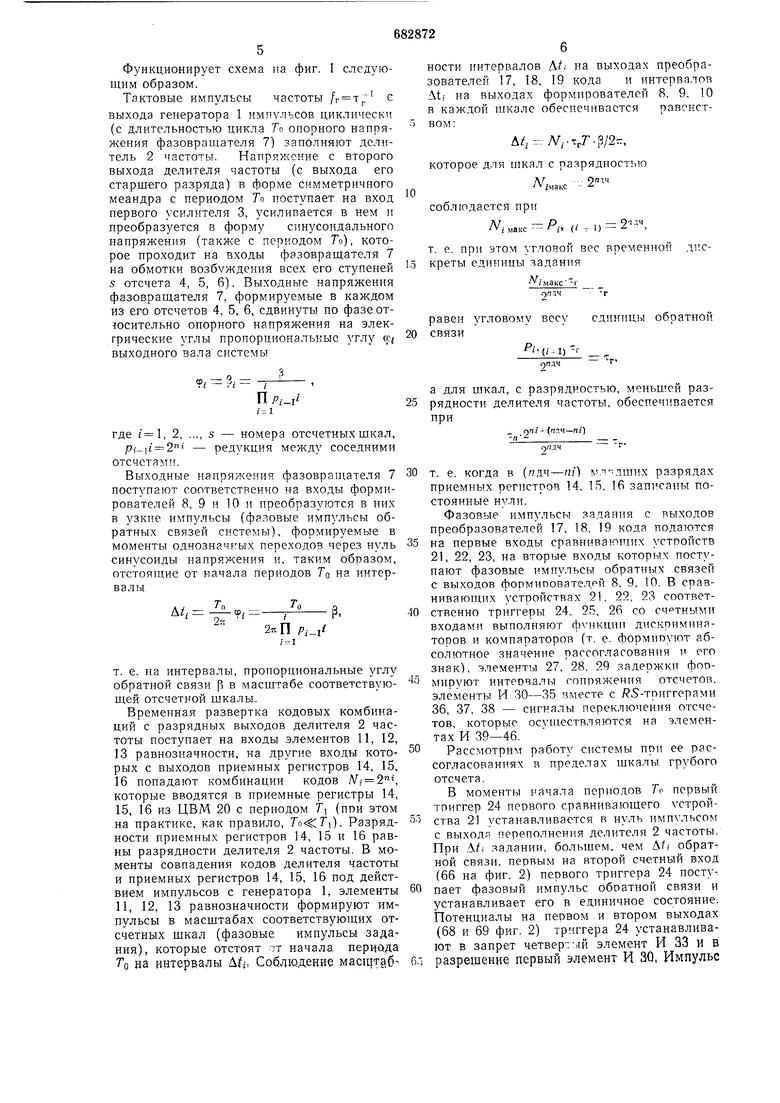

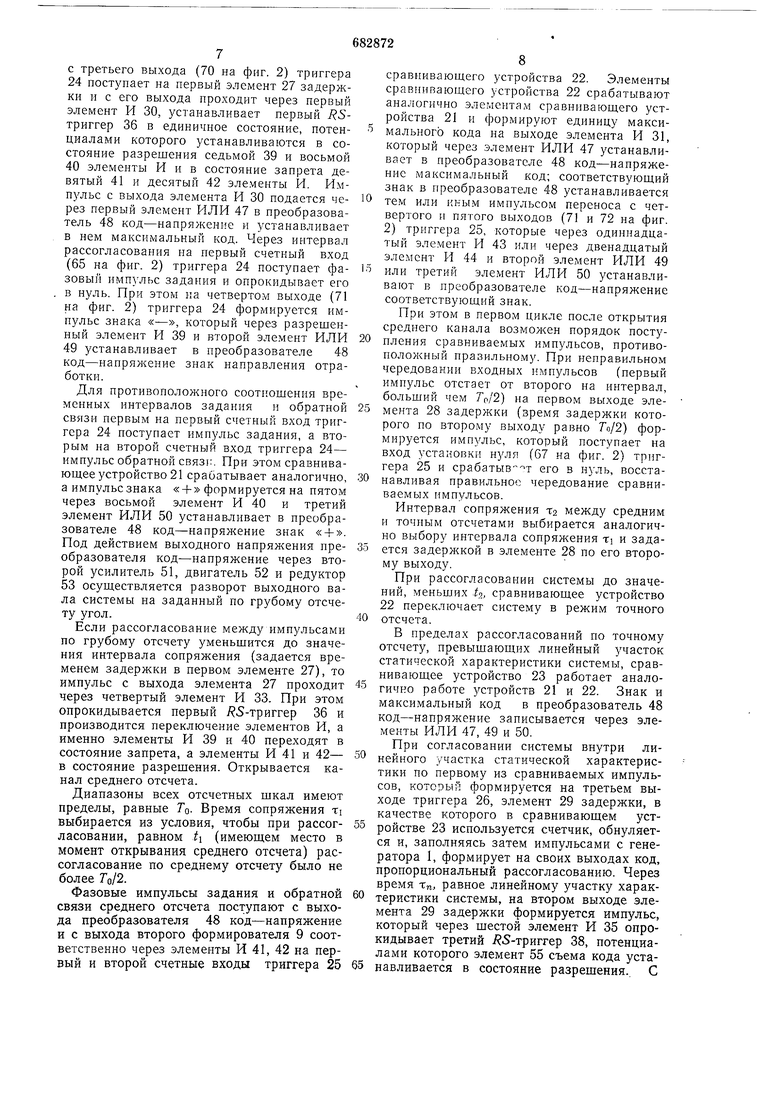

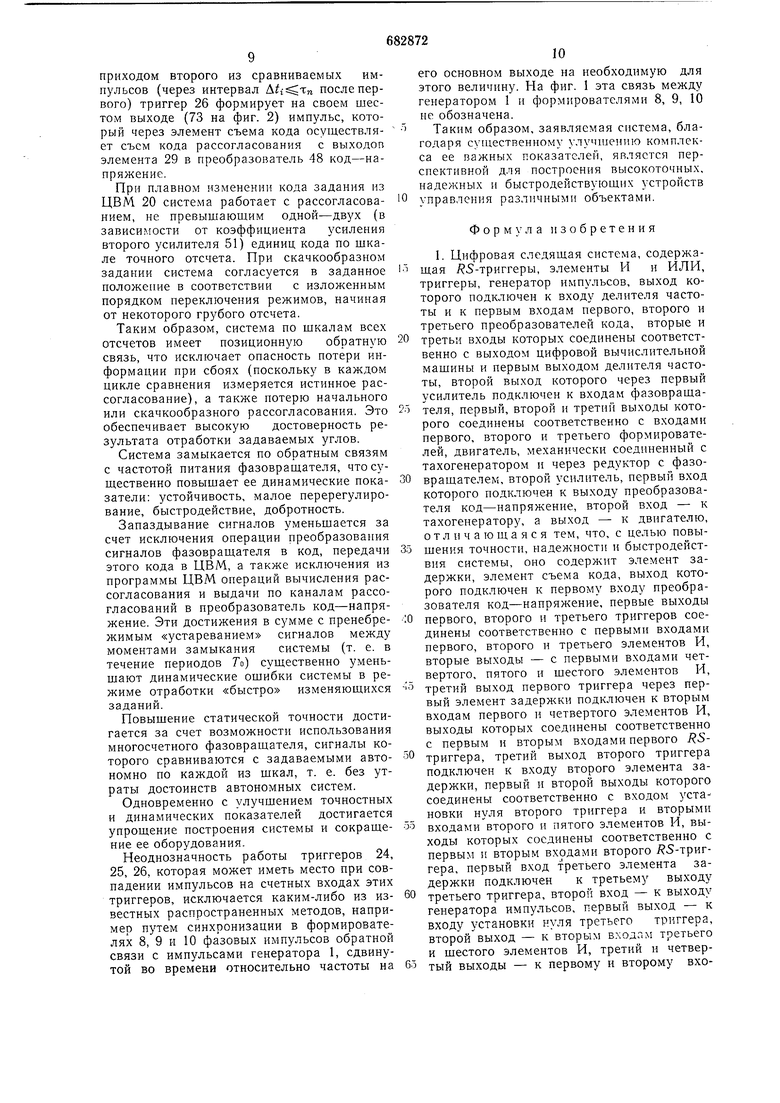

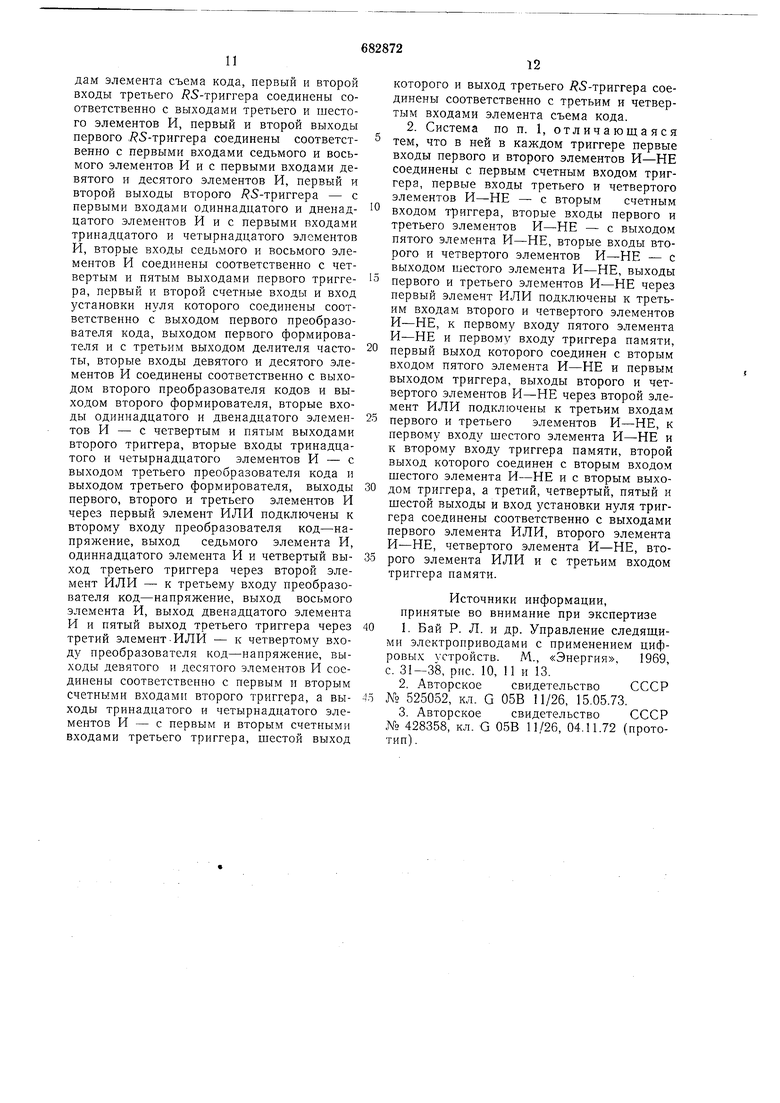

генератора импульсов, первый выход - к входу установки нуля третьего триггера, второй выход - к вторым входам третьего и шестого элементов И, третий и четвертый выходы - к первому входу и второму входу элемента съема кода. Первый и второй входы третьего / 5-триггера соединены соответственно с выходами третьего и шестого элементов И, первый и второй выходы первого / « -триггера - соответственно с первыми входами седьмого и восьмого элементов И и с первыми входами девятого н десятого элементов И, первый и второй выходы второго S-триггера - с первыми входами одиннадцатого и двенадцатого г элементов И и с первыми входами тринадцатого и четырнадцатого элементов И. Вторые входы седьмого и восьмого элементов И соединены соответственно с четвертым и пятым выходами первого триггера, первый и второй счетные входы и вход установки нуля которого соединены соответственно с выходом первого преобразователя кода, выходом первого формирователя и с третьим выходом делителя частоты, вторые вхо- 25 ды девятого и десятого элементов И связаны соответственно с выходом второго преобразователя кодов и выходом второго формирователя, вторые входы одиннадцатого и двенадцатого элементов И - с чет- 30 вертым и пятым выходами второго триггера, вторые входы тринадцатого и четырнадцатого элементов И - с выходом третьего преобразователя кода и выходом третьего формирователя. Выходы первого, второго и 35 третьего элементов И через первый элемент ИЛИ подключены к второму входу преобразователя код-напряжение, выход седьмого элемента И, выход одиннадцатого элемента И и четвертый выход третье- 40 го триггера через второй элемент ИЛИ - к третьему входу преобразователя код- напряжение, выход восьмого элемента И, выход двенадцатого элемента И и пятый выход третьего триггера через третий эле- мент ИЛИ - к четвертому входу преобразователя код-напряжение. Выходы девятого и десятого элементов И соединены соответственно с первым и вторым счетными входами второго триггера, а выходы три- лО надцатого и четырнадцатого элементов И- с первым и вторым счетными входами третьего триггера, шестой выход которого и выход третьего / 5-триггера соединены соответственно с третьим и четвертьш входами элемента съема кода. В каждом триггере первые входы первого и второго элементов И-НЕ соединены с первым счетным входом триггера, первые входы третьего и четвертогоэлементовИ- 60 НЕ - с вторым счетным входом триггера, вторые входы первого и третьего элементов И-НЕ - с выходом пятого элемента И - НЕ, вторые входы второго и четвертого элементов И-НЕ с выходом шестого 65 5 элемента И-НЕ. Выходы первого и третьего элементов И-НЕ через первый элемент ИЛИ подключены к третьим входам второго и четвертого элементов И-НЕ, к первому входу пятого элемента И-НЕ и первому входу триггера памяти, первый выход которого соединен с вторым входом пятого элемента И-НЕ и первым выходом триггера. Выходы второго и четвертого элементов И-НЕ через второй элемент ИЛИ подключены к третьим входам первого и третьего элементов И-НЕ, к первому входу шестого элемента И-НЕ и к второму входу триггера памяти, второй выход которого соединен с вторым входом шестого элемента И-НЕ и с вторым выходом триггера. Третий, четвертый, пятый и шестой выходы и вход установки нуля триггера соединены соответственно с выходами первого элемента ИЛИ, второго элемента И-НЕ, четвертого элемента И-НЕ, второго элемента ИЛИ и с третьим входом триггера памяти. На фиг. 1 представлена структурная схема цифровой следяшей системы; на фиг. 2 - функциональная схема триггера. Схема на фиг. 1 содержит генератор 1 импзльсов, делитель 2 частоты, первый усилитель 3, грубый 4, средний 5 и точный 6 отсчеты фазовращателя 7, первый 8, втоРОЙ 9 и третий 10 формирователи, первый II, второй 12 и третий 13 элементы равнозначности кодов и первый 14, второй 15 и третий 16 приемные регистры, входящие в первый 17, второй 18 и третий 19 преобразователи кода, соединенные с выходом цифровой вычислительной машины (ЦВМ) 20, первое 21, второе 22 и третье 23 сравнивающие устройства, первый 24, второй 25 и третий 26 триггеры сравнивающих устройств, первый 27, второй 28 и третий 29 элементы задержки, первый 30, второй 31, третий 32, четвертый 33, пятый 34 и шестой 35 элементы И, первый 36, второй 37 и третий 38 КЗ-триггеры, седьмой 39, восьмой 40, девятый 41, десятый 42, одиннадцатый 43, двенадцатый 44, тринадцатый 45 и четырнадцатый 46 элементы И, первый элемент ИЛИ 47, преобразователь 48 коднапряжение, второй 49 и третий 50 элементы ИЛИ, второй усилитель 51, двигатель 52, редуктор 53, тахогенератор 54 и элемент 55 съема кода. Схема на фиг. 2 содержит первый 56, второй 57, третий 58, четвертый 59, пятый 60 и шестой 61 элементы И-НЕ, первый 62 и второй 63 элементы ИЛИ, триггер 64 памяти. На фиг. 2 обозначены 65 - первый счетный вход триггера, 66 - второй счетный вход триггера, 67 - вход установки , 68 - первый выход триггера, 69 - второй выход, 70 - третий выход, 71 - четвертый выход, 72 - пятый выход, 73 - шестой выход.

Функционирует схема иа фиг. 1 следующим образом.

Тактовые импульсы частоты с выхода генератора 1 импульсов циклически (с длительностью цикла 7о опорного напряжения фазовращателя 7) заполняют делнтель 2 частоты. Напряжение с второго выхода делителя частоты (с выхода его старщего разряда) в форме симметричного меандра с периодом Го поступает на вход первого усилителя 3, усиливается в нем и преобразуется в форму синусоидального напряжения (также с периодом То), которое проходит на входы фазовращателя 7 на обмотки возбуждения всех его ступеней S отсчета 4, 5, б). Выходные напряжения фазовращателя 7, формируемые в каждом из его отсчетов 4, 5, 6, сдвинуты по фазе относительно опорного напряжения на электрические углы пропорциональные углу сс; выходного вала системы

П л-1

где , 2, ..., S - номера отсчетных шкал, p,--it 2 - редукция между соседними отсчетам.

Выходные напряжения фазовран1ателя 7 поступают соответственно на входы формирователей 8, 9 и 10 и преобразуются в них в узкие импульсы (фазовые импульсы обратных связей системы), формируемые в моменты однозначных переходов через нуль синусоиды напряжения и, таким образом, отстоящие от начала периодов Го на интервалы

.,

М,.

Р9-t

2.П P,,i

---1

Т. е. на интервалы, пропорциональные углу обратной связи р в масштабе соответствующей отсчетной шкалы.

Временная развертка кодовых комбинаций е разрядных выходов делителя 2 частоты поступает на входы элементов 11, 12, 13 равнозначности, на другие входы которых с выходов приемных регистров 14, 15, 16 попадают комбинации кодов /V,- , которые вводятся в приемные регистры 14, 15, 16 из ЦВМ 20 с периодом Г; (ппи этом на практике, как правило, . Разрядности приемных регистров 14, 15 и 16 равны разрядности делителя 2 частоты. В моменты совпадения кодов делителя частоты и приемных регистров 14, 15, 16 под действием импульсов с генератора 1, элементы 11, 12, 13 равнозначности формируют импульсы в масштабах соответствующих отсчетных шкал (фазовые импульсы задания), которые отстоят от начала периода Го на интервалы Д,-, Соблюдение масшта.бности интервалов на выходах преобразователей 17, 18, 19 кода и интервалов At; на выходах формирователей 8, 9, 10 в каждой шкале обеспечивается равонством:

A,--yV,.T,7-p/2,

которое для Н1кал с разрядностью

f--- Оптч

/макС соблюдается при

/V,-макс -Л:. «.1)

Т. е. при этом угловой вес временной дискреты единицы задания

/макс г 9ГИЧ г

равен угловому весу обратной связи

() ча для шкал, с разрядностью, меньшей разрядности делителя частоты, обеспечивается при

оп/(г:лч-п/)

-п- -

9 дчf

т. е. когда в (пдч-п1} vлдшиx разрядах приемных регистров 14, 15, 16 записаны постоянные нули.

Фазовые импульсы задания с выходов преобразователей 17, 18. 19 кода

на первые входы сравнивающих устройств 21, 22, 23, на вторые входы которых поступают фазовые импульсы обратных связей с выходов формиповател.рй 8, 9, 10. В сравниваюп1их устройствах 21, 22, 23 соответственно триггеры 24, 25, 26 со счетными входами выполня от ФУНКЦИИ дискриминаторов и компараторов (т. е. формиоу от абсолютное значение рассогласования и его знак), элементы 27, 28. 29 задержки фоомируют интеовалт сопряжения отсчетов, элементы И 30-35 вместе с / 5-триггерами 36, 37, 38 - сигналы переключения отсчетов, которые осуи1ествляются на э,чементах И 39-46.

Рассмотрим работу системы ее рассогласованиях в пределах шкалы грубого отсчета.

В моменты начала периодов Го первый триггер 24 первого сравнивающего устройства 21 устанавливается в нуль ИМПУЛЬСОМ с выходя переполнения делителя 2 частоты. При задании, большем, чем At; обрат ной связи, первым на второй счетный вход (66 на фиг. 2) первого триггера 24 поступает фазовый импульс обратной связи и устанавливает его в единичное состояние. Потенциалы на первом - и втором выходах (68 и 69 фиг. 2) триггера 24 устанавливают в запрет четвертлй элемент И 33 и В

разрешение первый элемент И 30, Импульс с третьего выхода (70 на фнг. 2) триггера 24 поступает па первый элемент 27 задержки п е его выхода проходит через первый элемент И 30, устанавливает первый Sтриггер 36 в единичное состояние, потенциалами которого устанавливаются в состояние разрешения седьмой 39 и восьмой 40 элементы И и в состояние запрета девятый 41 и десятый 42 элементы И. Импульс с выхода элемента И 30 подается через первый элемент ИЛИ 47 в преобразователь 48 код-напряжение и Зстанавливает в нем максимальный код. Через интервал рассогласования на первый счетный вход (65 на фиг. 2) триггера 24 поступает фазовый импульс задания и опрокидывает его в нуль. При этом на четвертом выходе (71 на фиг. 2) триггера 24 формируется импульс знака «-, который через разрешенный элемент И 39 и второй элемепт ИЛИ 49 устанавливает в преобразователе 48 код-напряжение знак направления отработки. Для противоположного соотношения временных интервалов задания п обратной связи первым на первый счетный вход триггера 24 поступает импульс задания, а вторым на второй счетный вход триггера 24- импульс обратной . При этом сравнивающее устройство 21 срабатывает аналогично, а импульс знака « + формируется на пятом через восьмой элемент И 40 и третий элемент ИЛИ 50 устанавливает в преобразователе 48 код-напряжение знак « + . Под действием выходного напряжения преобразователя код-напряжение через второй усилитель 51, двигатель 52 и редуктор 53 осуществляется разворот выходного вала системы на заданный по грубому отсчету угол. Если рассогласование между импульсами по грубому отсчету уменьшится до значения интервала сопряжения (задается временем задержки в первом элементе 27), то импульс с выхода элемента 27 проходит через четвертый элемент И 33. При этом опрокидывается первый У 5-триггер 36 и производится переключение элементов И, а именно элементы И 39 и 40 переходят в состояние запрета, а элементы И 41 и 42- в состояние разрешения. Открывается канал среднего отсчета. Диапазоны всех отсчетных щкал имеют пределы, равные Го. Время сопряжения TI выбирается из условия, чтобы при рассогласовании, равном А (имеющем место в момент открывания среднего отсчет а) рассогласование по среднему отсчету было не более 7о/2. Фазовые импульсы задания и обратной связи среднего отсчета поступают с выхода преобразователя 48 код-напряжение и с выхода второго формирователя 9 соответственно через элементы И 41, 42 на первыи и второй счетные входы триггера 25 сравнивающего устройства 22. Элементы сравнипаюшего устройства 22 срабатывают аналогично элементам сравнивающего устройства 21 и формируют единицу максимального кода на выходе элемента И 31, который через элемент ИЛИ 47 устанавливает в преобразователе 48 код-напряжение максимальный код; соответствующий знак в преобразователе 48 устанавливается тем или ины.м импульсом переноса с четвертого и пятого выходов (71 и 72 на фиг. 2) триггера 25, которые через одиннадцатый элемент И 43 или через двенадцатый элемент И 44 и второй эле.мент ИЛИ 49 или третий элемент ИЛИ 50 устанавливают в преобразователе код-напряжение соответствующий знак. При этом в первом цикле после открытия среднего канала возможен порядок поступления сравниваемых импульсов, противоположный празильно.му. При неправильном чередовании входных импульсов (первый импульс отстает от второго на интервал, больший чем 7р/2) на первом выходе элемента 28 задержки (время задержки которого по второму выходу равно 70/2) формируется импульс, который поступает на вход установки нуля (67 на фиг. 2) триггера 25 и срабатыв- т его в нуль, восстанавливая правильное чередование сравниваемых импульсов. Интервал сопряжения Т2 между средним и точным отсчетами выбирается аналогично выбору интервала сопряжения Т и задается задерл кой в элементе 28 по его второму выходу. При рассогласовании системы до значений, меньших ,9, сравнивающее устройство 22 переключает систему в режим точного отсчета. В пределах рассогласований по точному отсчету, превышающих линейный Зчасток статической характеристики системы, сравнивающее устройство 23 работает аналогично работе з стройств 21 и 22. Знак и максимальный код в преобразователь 48 код-напряжение записывается через элементы ИЛИ 47, 49 и 50. При согласовании системы внутри линейного участка статической характеристики по первому из сравниваемых импульсов, который формируется на третьем выходе триггера 26, элемент 29 задержки, в качестве которого в сравнивающем устройстве 23 используется счетчик, обнуляется и, заполняясь затем импульсами с генератора 1, формирует на своих выходах код, пропорциональный рассогласованию. Через время Тте, равное линейному участку характеристики системы, на втором выходе элемента 29 задержки формируется импульс, который через шестой элемент И 35 опрокидывает третий / 5-триггер 38, потенциалами которого элемент 55 съема кода устанавливается в состояние разрешения. С

приходом второго из сравниваемых импульсов (через интервал после первого) триггер 26 формирует на своем шестом выходе (73 на фиг. 2) импульс, который через элемент съема кода осуществляет съем кода рассогласования с выходоп элемента 29 в преобразователь 48 код-напряжение.

При плавном изменении кода задания из ЦВМ 20 система работает с рассогласованием, не превышаюидим одной-двух (в зависимости от коэффициента усиления второго усилителя 51) единиц кода по шкале точного отсчета. При скачкообразном задании система согласуется в заданное положение в соответствии с изложенным порядком переключения режимов, начиная от некоторого грубого отсчета.

Таким образом, система по шкалам всех отсчетов имеет позиционную обратную связь, что исключает опасность потери информации при сбоях (поскольку в каждом цикле сравнения измеряется истинное рассогласование), а также потерю начального или скачкообразного рассогласования. Это обеспечивает высокую достоверность результата отработки задаваемых углов.

Система замыкается по обратным связям с частотой питания фазоврашателя, что существенно повышает ее динамические показатели: устойчивость, малое перерегулирование, быстродействие, добротность.

Запаздывание сигналов уменьшается за счет исключения операции преобразовапия сигналов фазовращателя в код, передачи этого кода в ЦВМ, а также исключения из программы ЦВМ операций вычисления рассогласования и выдачи по каналам рассогласований в преобразователь код-напряжение. Эти достижения в сумме с пренебрежимым «устареванием сигналов между моментами замыкания системы (т. е. в течение периодов Го) существенно уменьщают динамические ошибки системы в режиме отработки «быстро изменяющихся заданий.

Повышение статической точности достигается за счет возможности использования многосчетного фазоврашателя, сигналы которого сравниваются с задаваемыми автономно по каждой из шкал, т. е. без утраты достоинств автономных систем.

Одновременно с улучшением точностных и динамических показателей достигается упрошение построения системы и сокращение ее оборудования.

Неоднозначность работы триггеров 24, 25, 26, которая может иметь место при совпадении импульсов на счетных входах этих триггеров, исключается каким-либо из известных распространенных методов, например путем синхронизации в формирователях 8, 9 и 10 фазовых импульсов обратной связи с импульсами генератора 1, сдвинутой во времени относительно частоты на

его основном выходе на необходимую для этого величину. На фиг. 1 эта связь между генератором 1 и формирователями 8, 9, 10 не обозначена.

Таким образом, заявляемая система, благодаря существенному улучшению комплекса ее важных показателей, является перспективной для построения высокоточных, надежных и быстродействующих устройств управления различными объектами.

Формула изобретения

1. Цифровая следящая система, содержащая S-триггеры, элементы И и ИЛИ, триггеры, генератор импульсов, выход которого подключен к входу делителя частоты и к первым входам первого, второго и третьего преобразователей кода, вторые и третьи входы которых соединены соответственно с выходом цифровой вычислительной мащины и первым выходом делителя частоты, второй выход которого через первый усилитель подключен к входам фазоврашателя, первый, второй и третий выходы которого соединены соответственно с входами первого, второго и третьего формирователей, двигатель, механически соединенный с тахогенератором и через редуктор с фазовращателем, второй усилитель, первый вход которого подключен к выходу преобразователя код-напряжение, второй вход - к тахогеператору, а выход - к двигателю, отличающаяся тем, что, с целью повышения точности, надежности и быстродействия системы, оно содержит элемент задержки, элемент съема кода, выход которого подключен к первому входу преобразователя код-напряжение, первые выходы первого, второго и третьего триггеров соединены соответственно с первыми входами первого, второго и третьего элементов И, вторые выходы - с первыми входами четвертого, пятого и шестого элементов И, третий выход первого триггера через первый элемент задержки подключен к вторым входам первого и четвертого элементов И, выходы которых соединены соответственно с первым и вторым входами первого RSтриггера, третий выход второго триггера подключен к входу второго элемента задержки, первый и второй выходы которого соединены соответственно с входом установки нуля второго триггера и вторыми входами второго и пятого элементов И, выходы которых соединены соответственно с первым и вторым входами второго / 5-триггера, первый в.ход третьего элемента задержки подключен к третьему выходу третьего триггера, второй вход - к выходу генератора импульсов, первый выход - к входу установки нуля третьего триггера, второй выход - к вторым входам третьего и шестого элементов И, третий и четвертый выходы - к первому и второму входам элемента съема кода, первый и второй входы третьего / 5-триггера соединены соответственно с выходами третьего и шестого элементов И, первый и второй выходы первого ,7 5-триггера соединены соответственно с первыми входами седьмого и восьмого элементов И и с первыми входами девятого и десятого элементов И, первый и второй выходы второго 5-триггера - с первыми входами одиннадцатого и двенадцатого элементов И и с первыми входами тринадцатого и четырнадцатого элементов И, вторые входы седьмого и восьмого элементов И соединены соответственно с четвертым и пятым выходами первого триггера, первый и второй счетные входы и вход установки нуля которого соединены соответственно с выходом первого преобразователя кода, выходом первого формирователя и с третьим выходом делителя частоты, вторые входы девятого и десятого элементов И соединены соответственно с выходом второго преобразователя кодов и выходом второго формирователя, вторые входы одиннадцатого и двенадцатого элементов И - с четвертым и пятым выходами второго триггера, вторые входы тринадцатого и четырнадцатого элементов И - с выходом третьего преобразователя кода и выходом третьего формирователя, выходы первого, второго и третьего элементов И через первый элемент ИЛИ подключены к второму входу преобразователя код-напряжение, выход седьмого элемента И, одиннадцатого элемента И и четвертый выход третьего триггера через второй элемент ИЛИ - к третьему входу преобразователя код-напряжение, выход восьмого элемента И, выход двенадцатого элемента И и пятый выход третьего триггера через третий элемент-ИЛИ - к четвертому входу преобразователя код-напряжение, выходы девятого и десятого элементов И соединены соответственно с первым и вторым счетными входами второго триггера, а выходы тринадцатого и четырнадцатого элементов И - с первым и вторым счетными входами третьего триггера, шестой выход которого и выход третьего / 5-триггера соединены соответственно с третьим и четвертым входами элемента съема кода. 2. Система по п. 1, отличающаяся тем, что в ней в каждом триггере первые входы первого и второго элементов И-НЕ соединены с первым счетным входом триггера, первые входы третьего и четвертого элементов И-НЕ - с вторым счетным входом триггера, вторые входы первого и третьего элементов И-НЕ - с выходом пятого элемента И-НЕ, вторые входы второго и четвертого элементов И-НЕ - с выходом шестого элемента И-НЕ, выходы первого и третьего элементов И-НЕ через первый элемент ИЛИ подключены к третьим входам второго и четвертого элементов И-НЕ, к первому входу пятого элемента И-НЕ и первому входу триггера памяти, первый выход которого соединен с вторым входом пятого элемента И-НЕ и первым выходом триггера, выходы второго и четвертого элементов И-НЕ через второй элемент ИЛИ подключены к третьим входам первого и третьего элементов И-НЕ, к первому входу шестого элемента И-НЕ и к второму входу триггера памяти, второй выход которого соединен с вторым входом шестого элемента И-НЕ и с вторым выходом триггера, а третий, четвертый, пятый и шестой выходы и вход установки нуля триггера соединены соответственно с выходами первого элемента ИЛИ, второго элемента И-НЕ, четвертого элемента И-НЕ, второго элемента ИЛИ и с третьим входом триггера памяти. Источники информации, принятые во внимание при экспертизе 1.Бай Р. Л. и др. Управление следящими электроприводами с применением цифровых устройств. М., «Энергия, 1969, с. 31-38, рис. 10, 11 и 13. 2.Авторское свидетельство СССР N° 525052, кл. G 05В 11/26, 15.05.73. 3.Авторское свидетельство СССР № 428358, кл. G 05В 11/26, 04.11.72 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь синусно-косинусных сигналов в последовательность импульсов | 1985 |

|

SU1309310A1 |

| ТРЕХФАЗНЫЙ БЕСТРАНСФОРМАТОРНЫЙ НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2020 |

|

RU2758443C1 |

| БЕСТРАНСФОРМАТОРНЫЙ НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2018 |

|

RU2691968C1 |

| Устройство для контроля и регулирования параметров | 1984 |

|

SU1249491A1 |

| Устройство для диагностирования коллекторной электрической машины | 1983 |

|

SU1182446A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1991 |

|

SU1820385A1 |

| Вычислительное устройство для решения уравнений | 1980 |

|

SU938287A1 |

| Следящий измеритель частоты | 1985 |

|

SU1298675A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

| НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ И НАПРЯЖЕНИЯ | 2021 |

|

RU2784879C1 |

Авторы

Даты

1979-08-30—Публикация

1977-05-18—Подача