Изобретение относнтся к области телемехалики.

Известшы устройства для :сжатня и коднрования аналоговых сообщении в системах с кодово-и.миульсной модуляцией, содержащее последовательно соедииениые дискретизатор, преобразователь аналог-цифра, блок анализа приращений, выходы которого иодключены к входам блока иамяти, а также генератор и миульсов, один из выходов котор0:го подсоедине.и к ИМпульснОму входу дисюретизатора, и делитель частоты.

Извесриые устройства, реализуюисне прииадии отбраковки избыточных вьсборо к исходного сообщеиия на основе анализа приращений, требуют перечМвнной частоты о-ироса, проводят оценку текущей щирины спектра сообщения с использованием предсказания, посылают в канал данные, которые должны быть снабжены больши.м количеством служебной (адресной) информации о текущей оценке ширины спектра и соответствующем этой оценке временном интервале. Они не позволяют объединять данные от большого числа источников из-за переменной частоты опроса и иногда дают большую ногрещностьв результате запаздывания.

Цель изобретения - но вышение эффективности использования пронускной способности канала .передачи данных.

Это достигается тем, что другой выход генератора иМНульсов подключен к входу делите,тя частоты, а выходы делителя - к импульсным входам блока аналнза приращений. Блок анализа приращений включает в себя последовательно соединенные .интерполяторы, каждый из которых содержит стробируемый каскад, одни из входов которого подключен через элемент задержки к одноМу из входов схемы вычитания, другой вход - к соответствующему выходу делителя частоты, выход - к одному из входов сумматора и входу восстанавливающего фильтра. Вы.ход фильтра подсоединен к другому входу схемы вычитания, один из выходов этой схемы - к нороговой схеме, а другой - к схеме запрета. В интерполятор введен также генератор адреса. Один из его входов соединен с первым выходом пороговой схемы, с входами первого ключа и фордшруюшего каскада, подключенного к схеме запрета, другой вход - с выходом первого ключа и с входом второго ключа, а выход через второй ключ - с сумматором. Второй выход пороговой схемы соединен с другим входОМ первого ключа.

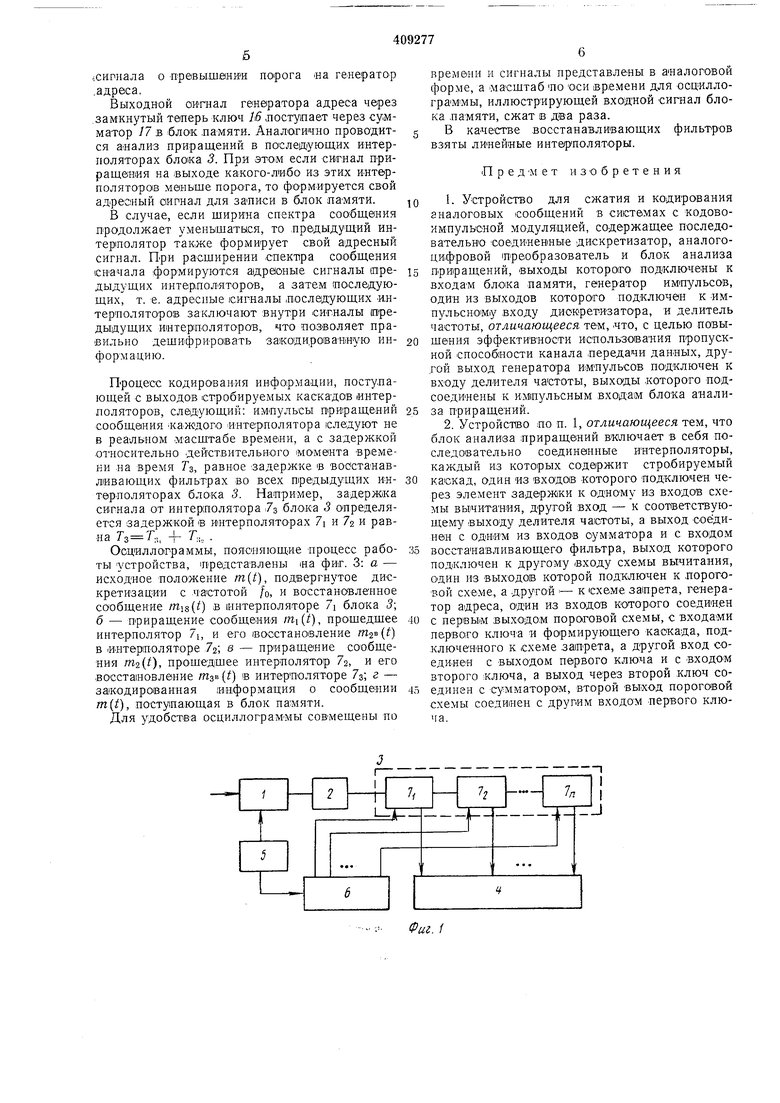

Ыа фиг. 1 показана блак-схема предложенного устройства; на фит. 2 - функциональная схема внтерполятора; на фиг. 3, а-г-осцилло|-раммы, поясняющие принцип работы устройДескретизатор / устройства, на который подается исходное сообщение, последователыг

соединен с аналого-цифровым преобразователем 2, блоком 3 анализа приращений сообщения и блоком 4 памяти. К иадпульсному входу диокреризатора подсоединен выход генератора 5 импульсов, другой выход этого генэратора - к делителю 6 частоты. Выходы делителя лодключены к соответств/ющиМ импульсным входам блока 3, содержащего п интерполяторов /1-7,1 , которые имеют (кроме последнего) по два выхода (один из них подсоединен к блоку памяти, а другой - к последующему интерполятору) .

Предложенное устройство работает следующим образом.

Подаваемое па его вход сообщение m(t) поступает на диокретизатор /, импульсный вход которого подключен к генератору 5 импульсов. Аналоговое сообщение (Подвергается амплитудно-импульаной модуляции с ф и кои ров-айн о и частотой опроса /о- Последняя выбирается из условия /o 2-FMai c (где FMBKC - ма:ксималыго возможная щприна спектра сообщения m(t). С выхода диокретиз-атора сигнал тл(1 проходит на вход прео бразователя 2, квантующего сообщения mn(t) ,по уровню. Цифровой выход преобразователя подается вы вход блока 3, состоящего из л идентичных интерполяторов.

Одновреме1нно на импульсный вход первого интерполятора 7 блока 3 поступают импульсы

с частотой следо Ва1Ния /i fo 2

где k - целое число, выбираемое из условия . (Fiiun - минимальная щирипа спектра сообщения m(t) от делителя 6 .частоты, в качестве которого может слуЖИть счетчик иа триггерах). Импульсы с частотой i попадают на стробируемый каскад 8 (схема «И) первого интер1полятора 7 ,и пропускают сигнал от преобразователя 2. Далее сигнал поступает на восстанавливающий цифровой фильтр 9, импульсная реакция которого в цифровой форме воспроизводит импульсную реакцию аналогового ступенчатого идаи лниейного интерполятора нлн более сложных восстанавливающих фильтров, согласованных с частотой следования импульсов, подаваемых на блоК делителя.

Для случая ступенчатой интерполяции восстанавливающим фильтром может служить запо минающее устройство (ЗУ) с временем памяти 7iiM /M (для интерполятора 7i , для интерполятора 7z и т. д.). Одновременно входной сигнал интерполятора подается на элемент 10 задержки (для цифровых данных это ЗУ, частота считывания j OTOporo определяется временем запаздывания Гзм сигнала в восста-навливающем фильтре). Для произвольного фильтра .

Далее сигналы от фильтра и элемента задерЖКИ поступают па вычитающее устройство //, выходной сигнал которого представляет разность (приращение) между входным сигналом и восстановленным . из входного по менипей (в 2 раз для г-го иптерполлтора) части его выборок. В том случае, если величина какой-ЛИбо выборки этой разности превышает установленный порог, то такой разностный сигнал подвергается дальнейшему анализу в последующем интерполяторе, если нет, то с выхода порогового устройства .12 поступает через формирующий каскад 13 сигнал на схему 14 запрета, который исключает необходимость проводить последующий анализ в следующем интерполяторе блока 5. Этот же сигнал, на который накладывается .«адрес интерполятора 7i в генераторе 15 адреса, проходит через ключ 16 и cyMiMaTOip 17 на блок 4 памяти для записи в нем информации об отсутствии в исходном сообщении высокочастотных составляющих, превосходящих но амплитуде установленный порог. При этом на блок памяти, работающий в старт-стопном режиме, поступают выборки от стробируемого каскада интерполятора 7 блока 3, которые постоянно записываются в блок памяти. Выборки приращений от интерполяторов 7, 7з и т. д. в случае отсутствия высокочастотных составляющих, превосходящих порог, не записываются. Если наступает такой момент, что интенсивность приращения превосходит порог, то соответствующий адресный сигнал интерполятора 7, сформированный в генераторе адреса, поступает через ключ 16 и сумматор 17 на блок па1мяти. Появление его дважды позволяет судить об отсутствии высокочастотных составляющих в интерв-але времени между двумя адресными сигналами и правильно расшифровать закодированную информацию. Вторая его запись может появиться в том случае, если первая запись уже была. Для этого служат самоблокирующиеся управляемые ключи ,16 и }8.

В начальном состоянии ключ 16 заммнут, а ключ . разомкнут. Если сигнал с выхода вычитающего устройства 11 не превыщает порог, то соответствующий сигнал с первого выхода порогового устройства 12 поступает одновременно на формирующий каскад 13, разомкнутый ключ (и замыкает его) и генератор 16 адреса, где на него накладывается адресный признак интерполятора. Далее сигнал с выхода генератора адреса подается через замкнутый ключ .16 на сумматор 17 и далее на блок на 1яти. Ключ 16 после прохождения сигнала переходит в разомкнутое состояние - самоблокируется. Замыкается он тенерь только после поступления на его второй вход сигнала с выхода ключа 18. Таким образом, второй раз адресный сигнал, свидетельствующий об отсутствии высокочастотных составляющих в исходном сообщении, не может быть записан.

Если после описанной ситуации порог превышается, то со второго выхода порогового устройства 12 подается сигнал на уже замкнутый ключ /S и далее на генератор адреса. Выходной сигнал ключа 1-8 замыкает ключ 16 и размыкает са.м ключ IS - блокирует его, что делает невозможным поступление второй раз

б

«сигнала о п-ревышании порога «а генератор .адреса.

Выходной оигнал генератора адрес-а через .замкнутый теперь ключ 16 .поступает через сумматор 17 в блок .памяти. Аналогично проводится анализ приращений в послеиующих интерполяторах блока 3. При это1М если сигнал приращбвия на выходе какого-либо из этих интерполяторов меньше порога, то формируется свой адресный сигнал для записи в блок памяти.

В случае, если ширина спектра соо1бш,ения продолжает уменышатыся, то .предыдущий интер1нолятор также формирует свой адресный сигнал. При расширении .cneKTipa сообщения сначала формируются адресные сигналы inpeдыдущих интерлолЯторов, а затем (последующих, т. е. адресные сигналы .последующих интерполяторов заключают внутри сигналы предыдущих интерполяторов, что позволяет правильно дешифрировать закодированную информацию.

Процесс кодирования инфор.мации, поступающей с выходов стробируемых каскадов интерполяторов, следующий: импульсы приращений сообщения Каждого интерполятора |Следуют не в реальном Масштабе времени, а с задерж.кой относительно действительного адо-мента времени на время Гз, равное задержке в восстанавливающих фильтрах во всех предыдущих интерноляторах блока 3. Например, задержка сигнала от интерполятора ./з блока 3 Опре.деляется задержкой в интерполяторах 7i и Zg и рав.на ,, Ц- Г,, .

Осциллограммы, пояоняющ.ие процесс работы устройства, представлены на фиг. 3: а - исходное положение ni(t, подвергнутое дискретизации с частотой /о, и восстановленное сообщение /HIS (О в интерполяторе 7 блока 5; б - приращение сообщения m(t), прошедшее интерполятор 7i, и его восстановление mzs(t) в Интерполяторе 7, в - прира.щение сообщения /П2(), прошедшее интерполятор /2, и его восста1новление /Пзв (t) IB интерполяторе 7з; г - за кодированная информация о сообщении m{t), поступающая в блок памяти.

Для удобства осциллограм-мы совмещены по

6

времени и сигналы представлены в аналоговой форме, а -масштаб шо оси ;времени для осциллограММЫ, иллюстрирующей входной сигнал блока .памяти, сжат в два раза.

В качестве восстанавливающих фильтров взяты линейные интерполяторы.

Пред М е т изобретения

1. Устройство для сжатия и кодирования аналоговых сообщений в системах с кодовоимпулысной модуляцией, содержащее последовательно соединенные дискретизатор, аналогоцифровой Преобразователь и блок анализа приращений, выходы которого подключены к входа-м блока памяти, генератор импульсов, один из ВЫХО.ДОВ которого подключен к нмпульсному .входу диокретизатора, и делитель частоты, отличающееся тем, что, с целью повышения эффективности использования пропускной способности канала передачи данных, дру.гой выход генератора импульсов подключен к входу делителя частоты, выходы которого подсоединены к импульсным входам блока анализа приращений.

2. Устройство .по п. 1, отличающееся тем, что блок анализа приращений включает в себя последовательно соединенные интерполяторы, каждый из которых содержит стробируемый каскад, один из входов которого подключен через элемент задержки к одному из входов схемы вычитания, другой вход - к соответствующему выходу делителя частоты, а выход соединен с одним из входов сумматора и с входом восстанавливающего фильтра, выход которого подключен к другому входу схемы вычитания, один из выходов которой подключен к пороговой схеме, а .другой - к схеме запрета, генератор адреса, один из входов которого соединен с первым выходом пороговой схемы, с входами первого ключа и формирующего каскада, подключенного к схеме за1прета, а другой вход соединен с выходом первого ключа и с входом второго ключа, а выход через второй .ключ соединен с сумматором, второй выход пороговой схемы соеди1нен с другим входом .первого ключа.

(PiiZ.2

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ ДЛЯ АДАПТИВНЫХ АДРЕСНЫХ СИСТЕМ | 1978 |

|

SU1840438A1 |

| Экстраполятор видеосигнала изображения | 1989 |

|

SU1718246A1 |

| АДАПТИВНОЕ ПРИЕМНОЕ УСТРОЙСТВО | 1980 |

|

SU1840134A1 |

| АВТОМАТИЧЕСКИЙ АУДИОМЕТР | 2024 |

|

RU2840436C1 |

| Устройство для автоматической компенсации неравномерности фона видеосигнала | 1980 |

|

SU924914A2 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ ДЛЯ АДАПТИВНЫХ АДРЕСНЫХ СИСТЕМ | 1979 |

|

SU1840440A1 |

| ГЕНЕРАТОР ПОСЛЕДОВАТЕЛЬНОСТЕЙ ИМПУЛЬСОВ | 2022 |

|

RU2784622C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СТАРТСТОПНЫХ СООБЩЕНИЙ | 2001 |

|

RU2210191C2 |

| Программно-управляемый генератор синусоидальных колебаний | 1986 |

|

SU1460768A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

.,

Авторы

Даты

1973-01-01—Публикация