1

Предлагаемое изобретение относится к цифровой электроизмерительной технике и предназначено для одновременного вычисления в реальном масштабе времени полного набора авто- и взаимных корреляционных функций п случайных процессов, что может быть использовано в задачах автоматического управления, технологического контроля и т. д.

В настоящее время известны и получили распространение цифровые коррелометры параллельно-последовательного действия, которые вычисляют в реальном масштабе времени т ординат автокорреляционной функции случайного процесса одного канала измерения или т ординат взаимной корреляционной функции случайных процессов двух каналов измерения.

Такие коррелометры, которые можно назвать двухканальными (по числу обрабатываемых случайных процессов) обычно включают в себя два аналого-цифровых преобразователя (АЦП), два регистра сомножителей, в которые поступают из АЦП дискретные отсчеты входных сигналов; множительное устройство, сумматор произведений и выходное запоминаюш,ее устройство (ЗУ) для хранения частичных сумм произведений отсчетов с одинаковым временным сдвигом в процессе вычислений и после их завершения. Временный сдвиг между отсчетами входных сигналов образуется с помош,ью промежуточного ЗУ либо определенным порядком выборки.

Во многих задачах технологического контроля, автоматического управления, технической диагностики, самонастройки и т. д. необходимо в реальном масштабе времени вычислять авто- и взаимные корреляционные функции нескольких случайных процессов. Такие задачи можно решать, используя необходимое количество (по числу вычисляемых корреляционных функций) двухканальных коррелометров параллельно-последовательного действия. Однако подобная вычислительная система дорога, сложна по количеству используемого оборудования и ее применение не всегда оправдано.

Цель предлагаемого изобретения - расширение возможностей двухканального коррелометра. Предлагаемый /г-капальный коррелометр параллельно-последовательного действия обрабатывает в реальном масштабе времени одиовре.менно /г случайных процессов п вычисляет одним вычислительным устройством все авто- и взаимные корреляционные фу 1кции этих процессов.

Сушность изобретения заключается в том, что между поразрядными выходами 2 п регистров, в которые поступают из п аналогоцифровых преобразователей дискретные отсчеты п обрабатывае,мых случайных сигналов,

и входами 6jiOis.a умнол еиия включены блоки схем «п (совпадения) для занесения в олок умножения нар дискретных отсчетов входныл си; налов; выоор сомножителей, вводимых в олок умножения, нроизаодится с помощью ojiOKa ьыоора сомножителей (пар сомножителей), входы которого соединены с поразрядными выходами группы младших разрядов (триггеров) адресного счетчика, а выходы со. единены со входами олоков схем «И. Иодооное схемное решение нозволяет одним вычислительным устройством оораоатывать в реальнол масшгаое времени п случайных процессов и вычислять полный паоор авто- и взаимных корреляционных функции (всего г кривых).

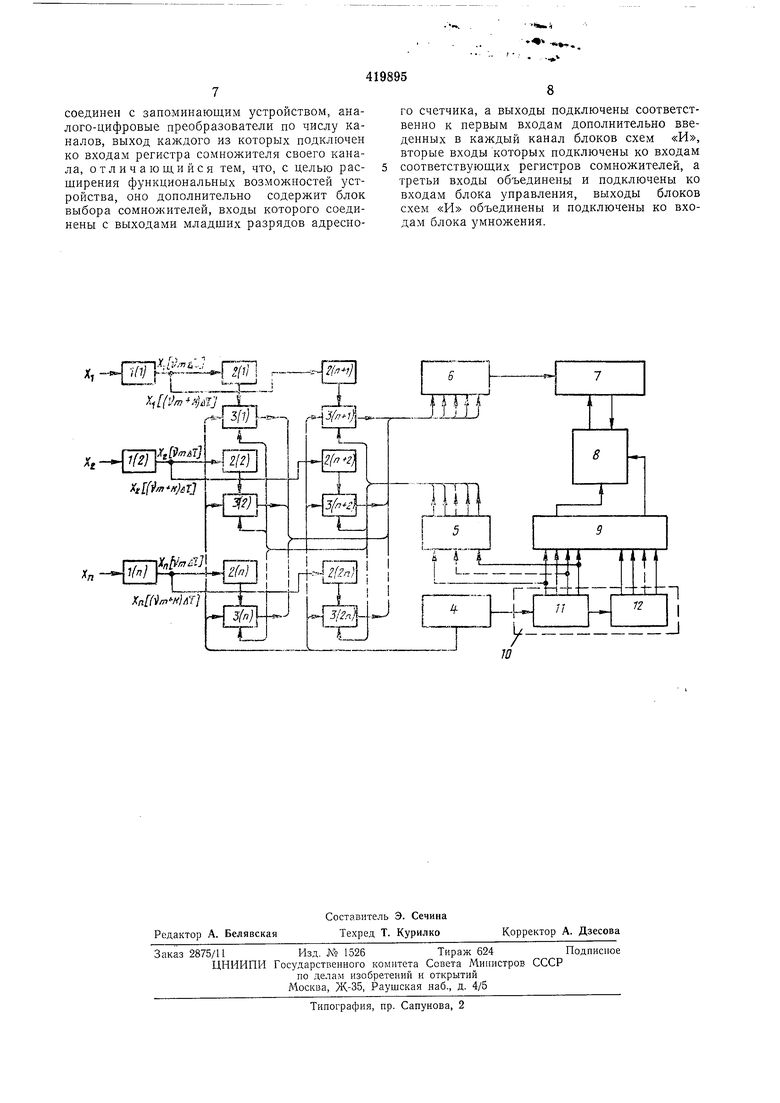

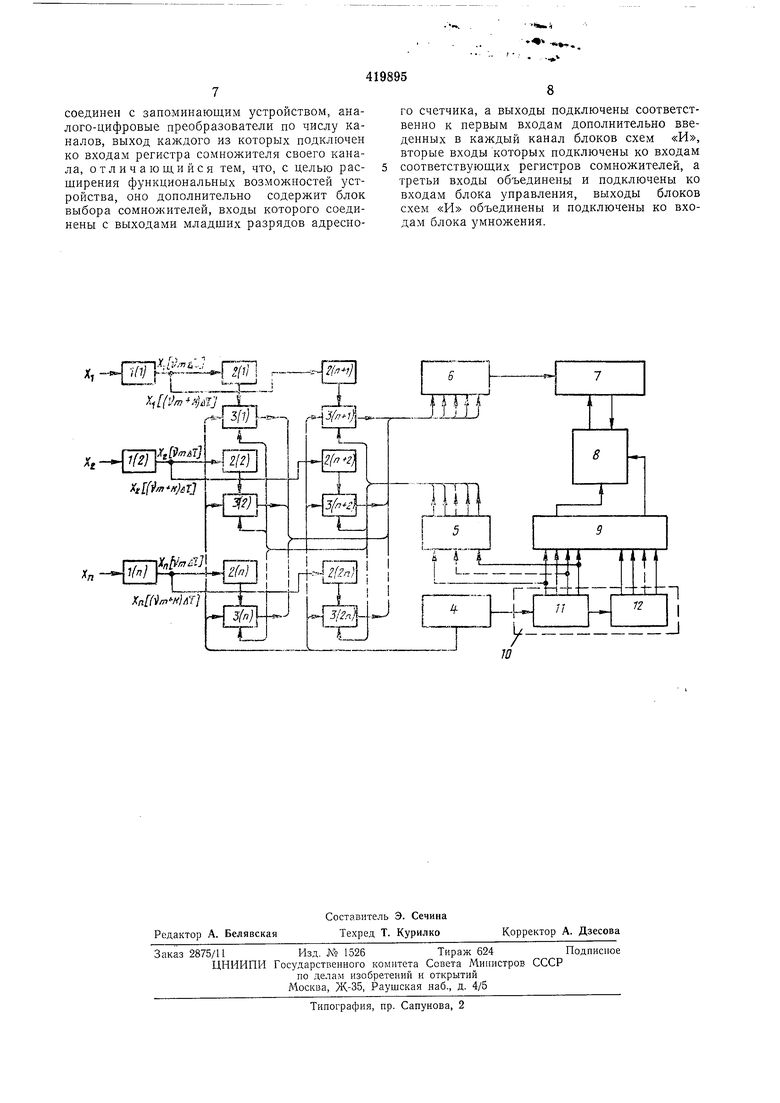

Функциональная схема нредлагаемого коррелятора приведена на чертеже, ибозначепия, принятые на схеме: 1(1), 1(2),... L(n)-аналого-цифровые нреобразователи (АЦИ); 2(1), 2(2),... 2(П), 2(n+i), 2(п+2),... 2(2п) - регистры сомножителей, в которые заносятся из АдИ коды дискретных отсчетов входных сигналов; 3(1), 3(2),... 3(п), 3(), 6(),... 3(2п) -блоки схем «И (совпадений). Кроме того в схему внесены; блок унравления 4, блок выбора сомножителей 5 (пар сомножителей), блок умножения 6, сумматор произведений 7, запоминающее устройство (bi) 6, дешифратор 9, адресный счетчик 10, младшие разряды адресного счетчика И (групна), старщне разряды адресного счетчика 12 (группа).

Предлагаемый коррелятор включает в себя п аналого-цифровых преооразователей 1(1), 1(2),... 1(/г), выходы которых соединены со входами регистров 2(1), 2(2),... 2(п), 2(д+1),... 2(2/г), поразрядные выходы упомянутых регистров соединены с блоками схем «И 3(1), 3(2), ... 3(ге), 3(я+1). 3(ft-i-2),... 3(2я); количество схем совпадений в блоке равно числу разрядов в регистре. Каждый из поразрядных выходов регистра соединен с одним входом одной схемы «И, второй вход схем «И (совпадений) всех блоков соединен с блоком управления 4; третий вход схем совпадения соединен с соответствующим выходом блока 5 выбора сомножителей (пар сомножителей). Выходы всех схем «И всех блоков подключены ко входам блока умножения 6, выходы которого нодключепы ко входам сумматора произведений 7, являющегося регистром числа выходного ЗУ 8. Выбор адреса ЗУ производится с помощью дешифратора 9, соединенного с поразрядными выходами группы младших разрядов 11 и группы старших разрядов 12 адресного счетчика. Поразрядные выходы группы 11 соединены со входами блока 5. Вход группы 11 соединен с блоком управления 4. Грунпа И пересчитывает тактовые импульсы, поступающие из блока управления на п, группа 12 - пересчитывает на т. Блок 5 является дешифратором состояний младших разрядов адресного счетчика и имеет п потенциальных выходов. С

помоптью младших разрядов адресного счетчика ЗУ делится на п зон - по количеству вычисляемых кривых; старшие разряды делят каждую зону на т ахлресов - по количеству вычисляемых в каждой кривой ординат.

Процесс обработки случайных процессов состоит Из А полных циклов вычислений (до достижения заданной статистической точности), в течение каждого из них вычисляется по одному произведению для каждого временного сдвига /еДт ( 0, 1,... т-) между отсчетами обрабатываемых процессов.

Каждый полный цикл состоит из т частных циклов. В течение частного цикла вычисляют5 Си все произведения для одного значения временного сдвига. Частный цикл состоит из /г тактов. В точение такта получается произведение одной из пар отсчетов, паходящихся в регистрах 2 (г), 2 («+/) -

Х( 1тЩ Xj (1т + к) AT,

полученное произведение добавляется в сумматоре к частичной сумме произведений отсчетов тех же процессов с соответственным 5 временным сдвигом, полученной в предыдущих циклах -

1-1

2 I/mAi:j Xj (Im + k) At,

г 1

и получается новая частичная сумма (lm+k)f.

В процессе вычислепий в регистры 2(1), 2 (2),... 2 (п) поступают отсчеты

Xi 1т А

(в первый такт первого частного цикла, интервал следования отсчетов - тДт); в регистры 2(п+1), 2(п+2),... 2(2п) поступают отсчеты

Xj (im + k) А.

(в каждый первый такт каждого частного цикла вычислений, интервал следования отсчетов - Дт). В течение каждого частного цикла вычислений получаются произведения

Xi Xj (Im 4 Щ At

- всего 11 произведений.

Рассмотрим порядок работы коррелометра в течение v-того полного цикла вычислений. В начале первого такта первого частного цикла v-Toro полного цикла в регистры 2(i) поступают отсчеты

,

а в регистры 2(/Н.0 - отсчеты Xj vy/zAt.

Далее из блока управления 4 в адресный счетчик подается «1, и он устанавливается в нулевое состояние. 15лок выбора пар сомножителей 6 дещифрирует состояние группы 11 младщих разрядов адресного счетчика и нодает разрешающий потенциал на блоки схем

«И 3(1), 3(ft+l). Из блока управления 4 поступает команда опроса всех блоков схем «И и через группы 3(1), 3(«+), на которые подано разрешенне с блока 5, в блок 6 поступают сомножители из регистров 2(1), 2(/г-{-1)-в данном случае эти сомножители равны. Из ЗУ 8 в сумматор 7 считывается сумма произведений .-I

Xj /ягАт Xi .

Сомножители, поступившие в блок умножения, перемножаются, полученное произведение добавляется в сумматоре к находящейся сумме и новая сумма

записывается в ЗУ 8. Затем сумматор 7 сбрасывается в нулевое состояние. На этом первый такт первого частного цикла заканчивается.

Во второй такт из блока управления 4 в группу 11 младших разрядов добавляется «1, блок выбора сомножителей 5 подает разрешение на блоки схем «И 3(1), 3(«-f2), сомножители

X, v/nAt, ЛГа v/7tA-

вводятся из регистров 2(1), 2(/г-|-2) в блок умножения 6, из ЗУ 8 в сумматор 7 считывается частная сумма

4-1

2 X, Im&i X,, l/mA-v ;

введенные в блок 6 сомножители перемножаются, и полученное произведение добавляется в сумматоре к находящейся там сумме, новая сумма

2 х /шАт Xf ///гЛт:

записывается в ЗУ, а сумматор сбрасывается. Описанный порядок работы повторяется в течение всех п тактов первого частного цикла. В конце последнего такта первого частного цикла регистры 2(п+1), 2(п+2),... 2(2п) сбрасываются-В «О и на этом первый частный цикл заканчивается.

В начале первого такта второго частного цикла в регистры 2(), 2(),... 2(2,i) поступают отсчеты

д;,-(-ш + 1)

после поступления «1 из блока управления 4 в адресный счетчик из группы младших разрядов 11 в группу старших разрядов 12 подается «1 переноса, и порядок работы повторяется аналогично описанному для первого частного цикла. В течение 2-го частного цикла получается набор произведений

Xi vmA- Xj (vm + I) l

которые добавляются в сумматоре к суммам

,lmA-.Xj(lm + )

и получаются новые суммы

Xi{lni Xj(lm + ).

1-Л

Порядок вычислений в течение каждого частного цикла повторяется для всех частных циклов. Таким образом, в течение полного vтого цикла вычислений получается набор произведений

Xi Xj (vm -|- А) AT, (/ 1, 2,. . ., п; у -. 1, 2,..., л; у% О, 1,..., m - 1) -

- всего произведений, и образуются частные суммы

2 1 vmA-J Xj (vm -f k) A-.

В конце последнего такта последнего частного цикла регистры 2(0, 2(/г+/) сбрасываются в «О, v-тый цикл вычислений заканчивается. Через Л полных циклов вычисления прекращаются, и в ЗУ 8 оказываются оценки п корреляционных функций, по т точек каждая. Из всего набора функций получаются п автокорреляционных функций

г(Мт) (i j) и n(n-l)

взаимных корреляционных функций Rij() (i J).

Описанный коррелометр вычисляет по две ветви для каждой взаимной корреляционной функции. В течение каждого частного цикла

н(н -1)

вычисляются

пар «симметричных

произведений

Хр vmAt Xq (v/n -f k AT (i - p; j q; p q) и (vm-{-k)-}( j-p- p-+q),

образуюпдих точки взаимной корреляционной функции, симметричные относительно ординаты

R,,(()) R,M

Таким образом, из п- ветвей получаются п

п(п - 1) автокорреляционных и полных взаимЛл

пых корреляционных функций.

Предмет изобретения

Мцогокаиальцый цифровой коррелометр, соержащий блок управления, выход которого подключен ко входу адресного счетчика, выходы адресного счетчика через дешифратор подключепы к запоминающему устройству, выход которого соединен с сумматором, подключенным к блоку умножения, выход сумматора

соединен с запоминаюплим устройством, аналого-цифровые преобразователи по числу каналов, выход калсдого из которых подключен ко входам регистра сомножителя своего канала, отличающийся тем, что, с целью расширения функциональных возможностей устройства, оно дополнительно содержит блок выбора сомножителей, входы которого соединены с выходами младших разрядов адресно-% 4

.„.

8

го счетчика, а выходы подключены соответственно к первым входам дополнительно введенных в каждый канал блоков схем «И, вторые входы которых подключены ко входам соответствующих регистров сомножителей, а третьи входы объединены и подключены ко входам блока управления, выходы блоков схем «И объединены и подключены ко входам блока умножения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный многомерныйцифРОВОй КОРРЕлОМЕТР | 1978 |

|

SU809199A1 |

| Многоканальный многомерный цифровой коррелометр | 1984 |

|

SU1187177A1 |

| Цифровой коррелометр | 1979 |

|

SU783797A1 |

| Многоканальный цифровой коррелометр | 1982 |

|

SU1040492A1 |

| Многоканальный коррелометр | 1976 |

|

SU613329A1 |

| Цифровой коррелометр | 1983 |

|

SU1113806A1 |

| Многоканальный многомерный цифровой коррелометр | 1985 |

|

SU1305714A1 |

| Многоканальный цифровой коррелометр | 1985 |

|

SU1262523A1 |

| Цифровой коррелометр | 1985 |

|

SU1298767A1 |

| Вероятностный коррелометр | 1977 |

|

SU705457A1 |

- L- .117Д i

Даты

1974-03-15—Публикация

1972-01-24—Подача