Изобретение относится к технике измерений в области передачи данных но дискретным каналам связи и может быть использовано при исследованиях, испытаниях, регламентных проверках дискретных каналов связи, используемых для передачи данных двоичным кодом.

Известны приборы выявления ошибок при передаче на низких и средних скоростях и приборы для подсчета сбоев в каналах для передачи двоичной информации на высоких скоростях.

Приборы состоят из передаюш;его и приемного полукомплектов. Передающий полукомплект представляет собой датчик квазислучайного двоичного испытательного сигнала, который подключается ко входу дискретного канала. В приемном полукомплекте запрограммирован идентичный - контрольный сигнал. Поступивший из канала испытательный сигнал, который может быть искажен вследствие наличия помех в канале, сравнивается с контрольным сигналом, в результате чего отмечаются неправильно принятые элементы, т. е. ошибки или сбои. Отношение числа ошибок к общему числу элементов, переданных за сеанс измерения, определяет достоверность передачи и является качественьгой характеристикой дискретного канала.

Приемный полукомплект содержит также систему фазовой автоподстройки частоты (поэлементная -синхронизация) и систему фазирования циклов испытательного и контрольного сигналов (цикловое фазирование).

Ручное включение системы циклового фазирования приводит к потере сеанса измерения при сдвиге циклов сигналов, который может иметь место из-за нарушения поэлементной

синхронизации вследствие кратковременных перерывов связи. Это требует постоянного присутствия оператора у прибора, так как в противном случае при нарушении циклового фазирования прибор регистрирует такое количество ошибок, которое уничтол ает все предыдлщие показания.

Цель изобретения - автоматическое включение системы цт клового фазирования при сдвиге циклов испытательного и контрольного сигналов и автоматическое ее отключение при восстановлении цикловой синфазности.

Это улучшает качественные и эксплуатационные характеристики приборов и позволяет с более высокой точностью производить

измерения без необходимости постоянного присутствия оператора.

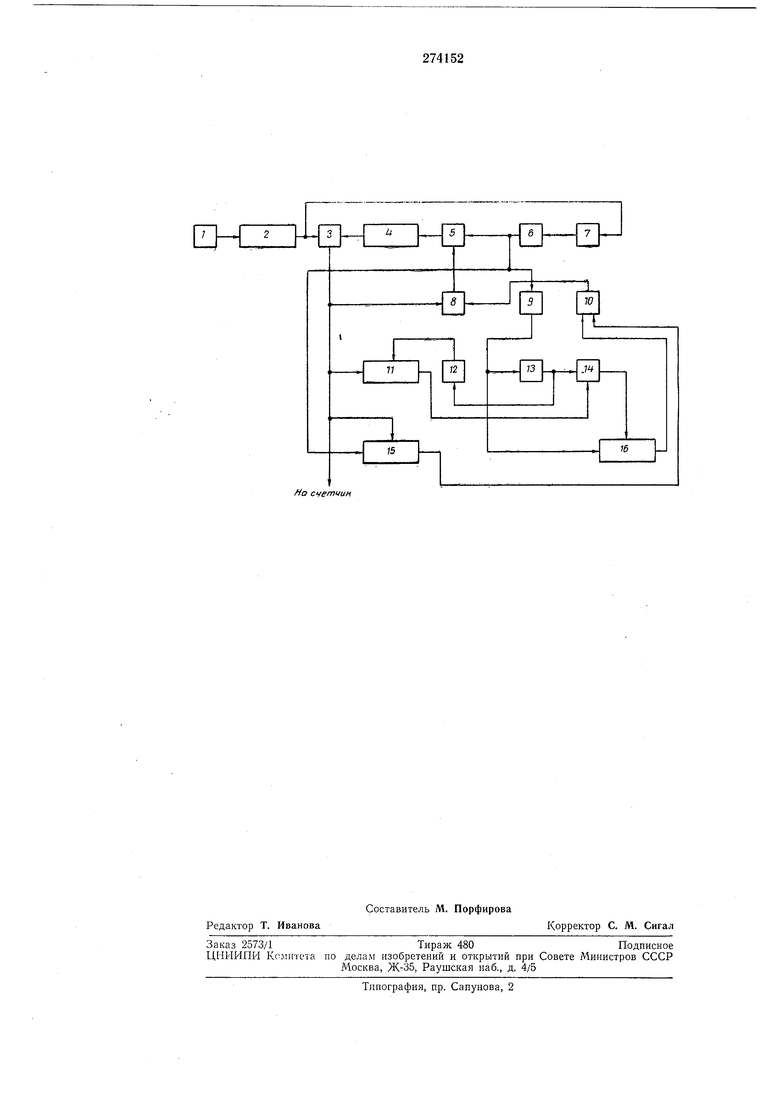

Предлагаемое устройство отличается от известных тем, что выход схемы сравнения подключен к одному из входов схемы совпадения, женных циклов и к сбросовому входу индикатора фазирования; при этом выход генератора тактовых импу.тьсов подключен к тактовому входу индикатора фазирования, соединенному с одним из входов триггера циклового фазирования, а также с управляющим входом генератора меток цикла, выход которого подключен к тактовому входу интегратора, через элементы задержки - к сбросовому входу интегратора и через элемент задержки и схему запрета - к сбросовому входу интегратора, причем выход индикатора нораженных циклов соединен с занрещающим входом схемы запрета, а выход интегратора соединен со вторым входом триггера циклового фазирования, выход которого подключен ко второму входу схемы совпадения, включенной своим выходом на запрещающий вход схемы запрета. На чертеже изображена блок-схема предлагаемого устройства для определения достоверности передачи. Устройство содержит датчик 1 испытательного сигнала, подключаемый ко входу дискретного канала 2 и представляющий собой регистр сдвига с логической обратной связью, вырабатывающий квазислучайную последовательность с длительностью цикла, равной 127 элементам, которая описывается рекуррентным уравнением , элемент последовательности с порядковым номером п; знак суммирования по модулю 2; схему 3 сравнения, поэлементно сравнивающую испытательный сигнал, поступивщий из канала 2, с сигналом от датчика 4 контрольного сигнала, идентичного датчику 1, и выдающую на выходе сигнал оплибки в случае несовпадения сигналов на входах; схему 5 запрета, через которую на датчик 4 поступают тактовые импульсы от генератора 6 тактовых импульсов; систему 7 поэлементной синхронизации, обеспечивающую равенство тактовых частот датчика 1 и генератора 6; схему 8 совпадения, выдающую сигнал на запрещающий вход схемы 5 запрета; генератор 9 меток цикла, вырабатывающий сигналы, период следования которых равен длительности цикла испытательного и контрольного сигналов; триггер 10 циклового фазирования; индикатор 11 пораженных циклов, представляющий собой счетчик, продвигаемый сигналами ощибки от схемы 3 и выдающий сигнал на выходе при поступлении на его вход 32 ошибок, сброс индикатора расфазирования в исходное состояние осуществляется метками цикла от генератора 9 через элементы 12 и 13 задержки, схему 14 запрета, на запрещающий вход-которой поступает сигнал от индикатора 11 порапредставляющий собой счетчик, продвигаемый тактовыми импульсами от генератора 6 и сбрасываемый в исходное состояние сигналом ошибки от схемы 3 сравнения, сигнал на выходе индикатора фазирования ноявляется в том случае, когда на его вход поступит 15 тактовых импульсов до поступления сброса, что соответствует безошибочному приему 15 элементов испытательного сигнала; интегратор 16, представляющий собой счетчик, продвигаемый метками цикла от генератора 9 меток цикла и сбрасываемый в исходное состояние также метками цикла через элемент 13 задержки и схему 14 запрета, сигнал на выходе интегратора появляется при условии, если сигнал сброса на него будет запрещаться до тех пор, пока счетчик не установится в седьмое состояние. Устройство работает следующим образом. Датчик 1 испытательного сигнала подключается ко входу дискретного канала 2 и передает в него циклический квазислучайный сигнал, длительность цикла которого равна 127 элементам. На приемном конце в произвольный момент времени включается датчикконтрольного сигнала, вырабатывающий идентичную носледовательность, которая подается на вход схемы 3 сравнения. С выхода дискретного канала испытательный сигнал поступает на второй вход схемы 3, и как синхронизирующий он поступает на систему 7 поэлементной синхронизации. Последняя под воздействием синхронизирующего сигнала управляет частотой генератора 6 тактовых импульсов, с выхода которого тактовые импульсы поступают на датчик 4 через схему 5 запрета. Таким образом, система поэлементной синхронизации обеспечивает равенство скоростей и совпадение фронтов испытательного и контрольного сигналов, поступающих на входы схемы 3. Поскольку датчик 4 был включен в произвольный момент времени, циклы испытательного и контрольного сигналов совпадать не будут, и для проведения сеанса измерений необходимо их сфазировать, т. е. совместить однозначные элементы циклов. Аналогичная задача возникает при нарушении цикловой синфазности во время сеанса измерения, которое может произойти при возникновении перерыа в канале, вызывающего поэлементную деинхронизацию. Критерием расфазирования в данном устойстве является число следующих подряд иклов, каждый из которых поражен опредеенным количеством ощибок. Известно, что при данной статистической труктуре испытательного сигнала схема 3 отетит за время, равное длительности одного икла, 64 ошибки в случае отсутствия циклоой синфазности.

Для надежной регистрации нораженного цикла нри расфазировании критическое число принято равным 32.

Индикатор 11 пораженных циклов подсчитывает число ошибок, отмеченных схемой 5 за время, равное одному циклу. Сброс индикатора 11 в исходное состояние осуществляется меткой цикла от генератора 9 через элементы 12 и 13 задержки. Если индикатор 11 за время между двумя сбросами, т. е. в течение одного цикла, успеет насчитать 32 ошибки, то этот цикл считается пораженным, а с выхода индикатора 11 подается сигнал на запрещающий вход схемы 14 запрета. Если число ощибок в цикле менее 32, то сигнал запрета не подается.

Так как в процессе сеанса измерения цикл может быть поражен числом ошибок, большим 32, даже при отсутствии расфазнрования, то для включения системы циклового фазирования необходимо отметить несколько следующих друг за другом пораженных циклов. Эту задачу выполняет интегратор 16.

Интегратор 16 представляет собой счетчик на «7, продвигаемый метками цикла от генератора 9 и сбрасываемый в исходное состояние теми же метками цикла через элемент 13 задержки и схему 14. При отсутствии пораженных циклов каждый сигнал сброса поступает на интегратор 16, и последний не продвигается дальще первого состояния. Каждый пораженный цикл запрещает поступление сброса на интегратор 16.

При наличии щести пораженных циклов, следующих непрерывно друг за другом, интегратор 16 устанавливается в седьмое состояние, и на выходе его появляется сигнал включения системы циклового фазирования, устанавливающий триггер 10 циклового фазирования в рабочее состояние. При любом другом числе следующих непрерывно друг за другом пораженных циклов, меньшем шести, сигнал включения системы циклового фазирования выдан не будет. По желанию оператора эту цифру можно изменять в зависимости от свойств исследуемого канала и скорости передачи.

От триггера 10 подается сигнал совпадения на схему 8 совпадения, с выхода которой поступает сигнал на запрещающий вход схемы 5 запрета при наличии сигнала ошибки на выходе схемы 5 сравнения.

Таким образом, при включенной системе циклового фазирования каждый сигнал ошибки запрещает поступление тактового импульса от генератора 6 на датчик 4, что стопирует датчик и смещает фазу сигнала на его выходе. Этот процесс длится до прекращения поступления ошибок от схемы сравнения, т. е. до полного совмещения циклов испытательного и контрольного сигналов.

После окончания фазирования необходимо отключить систему циклового фазирования. Эту задачу выполняет индикатор 15 фазирования. Принцип его действия основан на том, что при расфазированных циклах в сигналах используемой структуры не может следовать подряд более шести элементов сигнала, в которых не отмечены ошибки.

Только при поэлементном сравнении сфазированных циклов появляется семь и более следующих подряд безошибочных тактов - «неошибок. Отсутствие ошибок в семи тактах подряд свидетельствует о том, что циклы сфазированы. Чтобы исключить ложное срабатывание, критерием фазирования в данном устройстве является 14 следующих друг за другом «неошибок.

Индикатор 15 фазирования представляет собой счетчик на «15, продвигаемый тактовыми импульсами от генератора 6 и сбрасываемый в исходное состояние сигналом ошибки от схемы 3 сравнения.

При окончании фазирования в 14 элементах сигнала схема сравнения не отметит ошибки, сброс на индикатор 15 поступать не будет, и он установится в 15 состояние. При этом сигналом с выхода индикатора 15 устанавливается в исходное состояние триггер 10 и снимается сигнал совпадения со схемы 8 совпадения. При этом сигналы ошибок, отмеченные в сеансе измерения, уже не воздействуют на тактовые импульсы, т. е. система циклового фазирования отключена.

Предмет изобретения

Устройство для определения достоверности передачи двоичной информации, содерл ащее датчики испытательного и контрольного сигналов, схему сравнения, схему запрета, генератор тактовых импульсов и систему тактовой синхронизации, отличающееся тем, что, с целью повышения точности и автоматизации процесса измерений путем автоматического фазирования циклов испытательного и контрольного сигналов, выход указанной схемы сравнения подключен к одному из входов схемы совпадения, а также к тактовому входу индикатора порал енных циклов и к сбросовому входу индикатора фазирования; при этом выход генератора тактовых импульсов подключен к тактовому входу индикатора фазирования, соединенному с одним из входов триггера циклового фазирования, а также с управляющим входом генератора меток цикла, выход которого подключен к тактовому входу интегратора, через элементы задержки - к сбросовому входу интегратора, а через элемент задерлски и схему запрета - к сбросовому входу интегратора, причем выход индикатора пораженных циклов соединен с запрещающим входом схемы запрета, а выход интегратора соединен со вторым входом триггера циклового фазирования, выход которого подключен ко второму входу смехы совпадения, включенной своим выходом на запрещаюн1,нй вход схемы запрета.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения достоверности передачи двоичной информации | 1975 |

|

SU618857A2 |

| Устройство для определения достоверности передачи двоичной информации | 1988 |

|

SU1670794A1 |

| Устройство для обнаружения ошибок по элементам двоичного сигнала | 1984 |

|

SU1256228A1 |

| УСТРОЙСТВО ДЛЯ ПОДСЧЕТА ОШИБОК В ТЕЛЕГРАФНЫХ И ТЕЛЕФОННЫХ КАНАЛАХ СВЯЗИ | 1972 |

|

SU432685A1 |

| Устройство для измерения достоверности передачи информации | 1987 |

|

SU1418919A1 |

| Устройство для регистрации ошибок | 1972 |

|

SU437236A1 |

| УСТРОЙСТВО для ОПРЕДЕЛЕНИЯ ДОСТОВЕРНОСТИ ИНФОРМАЦИИ, ПЕРЕДАВАЕМОЙ ЦИКЛИЧЕСКИМ КОДоМ | 1971 |

|

SU316204A1 |

| Устройство для измерения достоверности передачи информации по дискретному каналу связи | 1987 |

|

SU1478349A1 |

| Устройство для определения достовер-НОСТи пЕРЕдАчи дВОичНОй иНфОРМАции | 1979 |

|

SU813805A2 |

| ПРИЕМНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯХАРАКТЕРИСТИКИ ГРУППОВОГО ВРЕМЕНИЗАПАЗДЫВАНИЯ | 1972 |

|

SU428309A1 |

Авторы

Даты

1970-01-01—Публикация