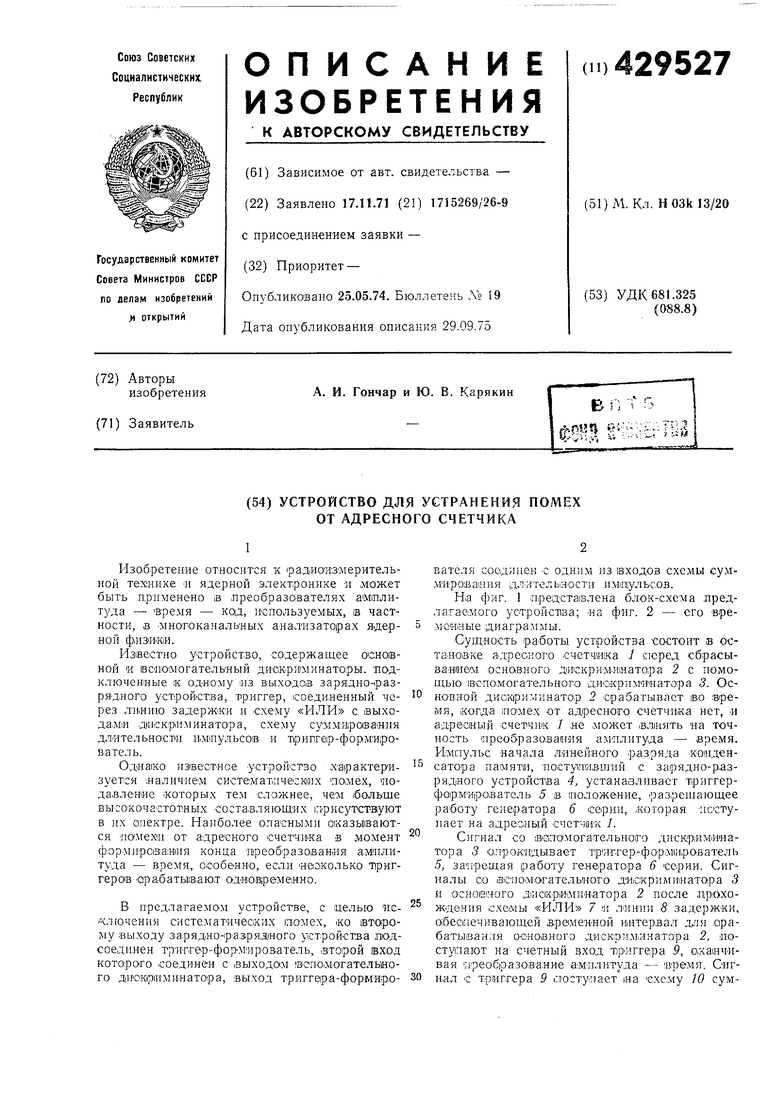

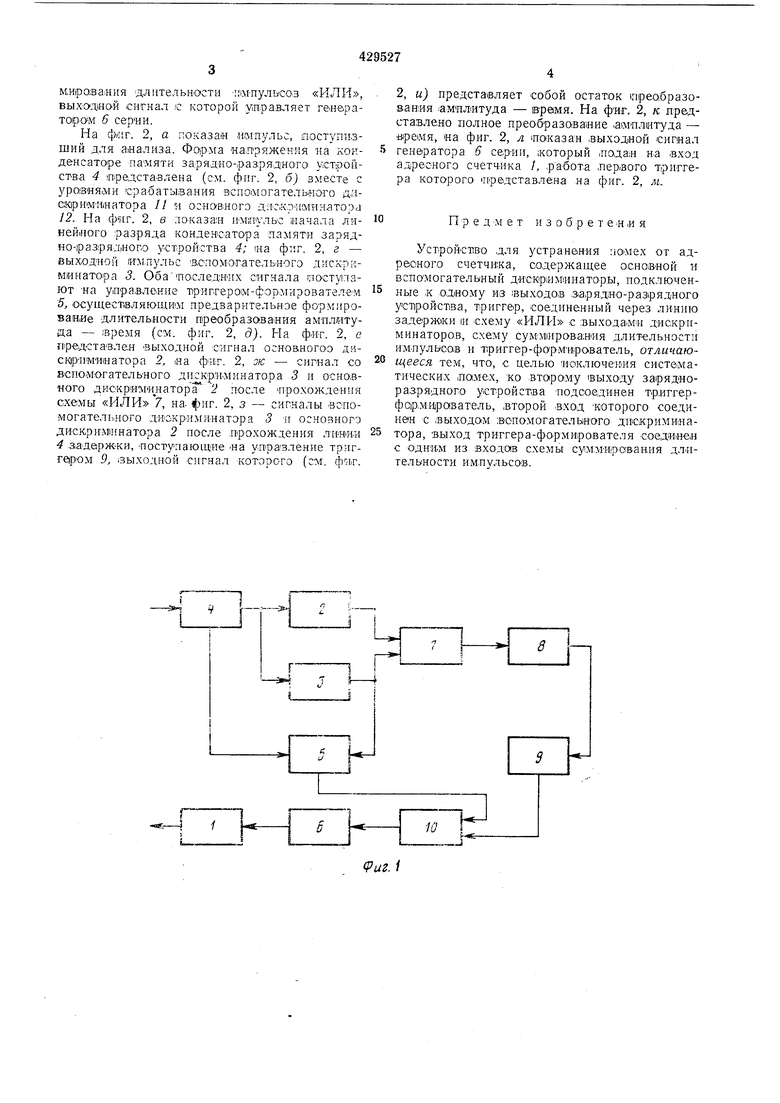

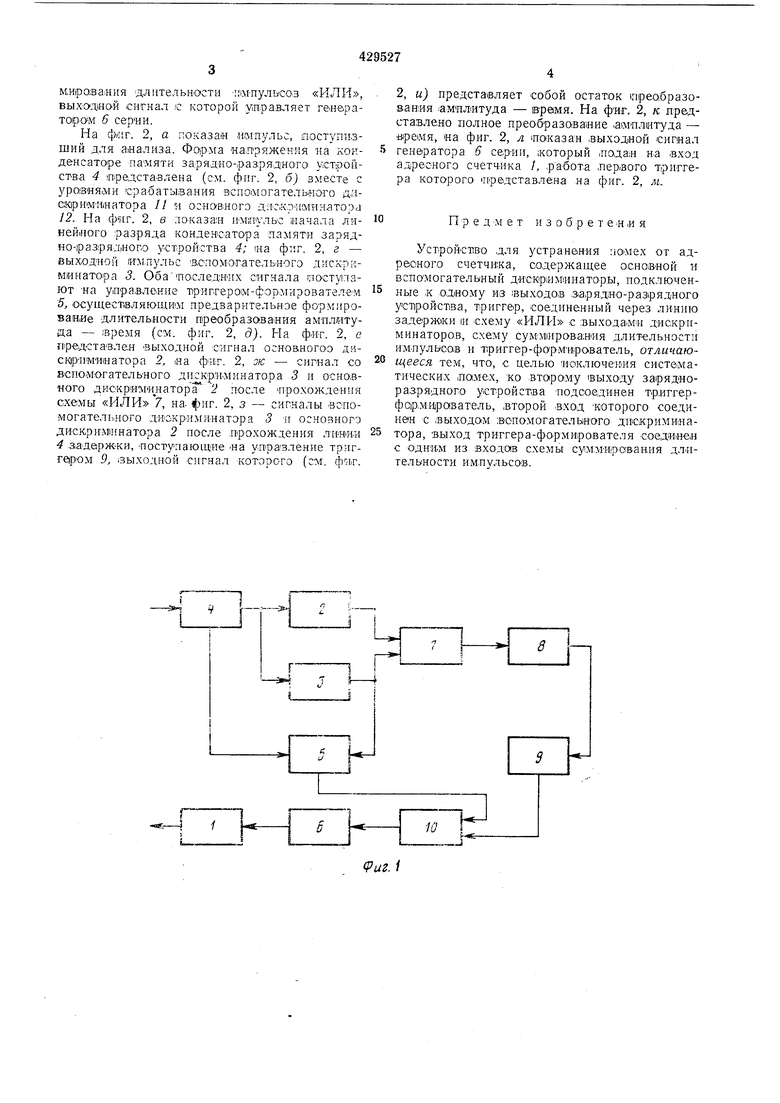

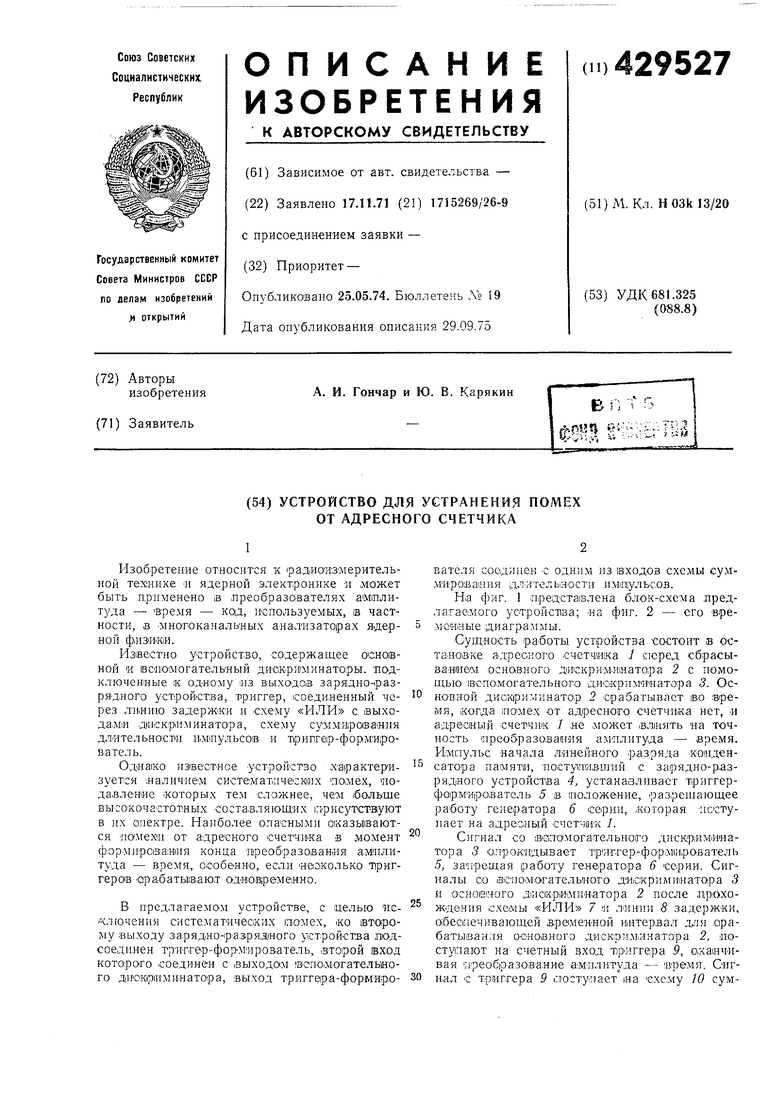

Изобретение относится к радиоиз-мерительной технике -и ядерной электронике -и иМожет быть дриме«ено IB -преобразователях амплитуда - время - код, используемых, в частности, в Многоканальных анализаторах ядерной флзШои. Известно устройство, содержащее OCHOIBной и всло могательный дис;кри минато1ры. :подключениые к од-ному «з выходов зарядно-разряд.ного устройства, триггер, 1соеди,ненный через линию задержки и €хел1у «ИЛИ с 1выходалпи д1И|Скр(Иминатора, схему суммираваяия длительности имиульсов и трилгер-формИрователь. Однако из1вестное устройство .характеризуется ;наличиеМ систематических aoiMex, подавлеиие которых тем сложнее, чем |больше высокочзстотных соста,вля1ОЩИХ присутствуют в их спектре. Наиболее оласными оказываются -помехи от адресного счетчика в момент формирования конца тиреобразовандя а.матлитуда - время, особенно, если «егоколько Т риггер ов ор аб аты1в-а ют ем е;н н о. В предлагаемо устройстве, с щелью неключения систематИческих стомех, ко iBTOipoму выходу заряд,но-1раэряд1ного устройства подсоединен триггер-форМ:ирователь, второй вход которого соединен с выходам всполюгательиого дискриминатора, выход тригге1ра-формирователя соединен с одним из входов схемы суммИ:рока1}1ия дл ительности им1П ульсов. Н-а фиг. 1 лредставлена блок-схема предлагаемого устройспва; -на фиг. 2 - его времсниые диаграммы. Сущность работы устройства -состоит в остановке адресного счетчгика 1 шсред сбрасываииел основного дагскри-м-инатора 2 с иомощью вспомогательного д.ИСкршкгаатогра 3. Основной диск|риминатор 2 срабатывает во время, когда помех от адресиого счетчика нет, и адресный счетчик / не может вл1иять на точность прео5разова1нз-1я амплитуда - время. Импульс «ачала лйнейиого разряда конденсатора па1мят1и, посту пмвигий с зарядно-рл.зрядного устройства 4, устанавливает триггерформирователь 5 в положение, разре1пающее работу генератора 6 серии, которая исстунает на адреоный счетчик /. Сигнал со всломогательного ди:ск.р;им1инатора 5 олрокпдывает триггер-форлиирователь 5, запрещая работу генератора 6 серии. Сигналы со вспомогательного дтаскримиматора 5 и осноЕного Д иакрнмин.атора 2 после прохождения схемы «ИЛИ 7 к Линпи 8 задержки, О1бес1печивающей временной интервал для cipaбатыван; я основного дискр г.м инатора 2, поступают на счетный вход триггера 9, о,ка1НЧИвая Преобразование а-мллитуда - иремя. Сигнал с триггера 9 (Поступает на схе.му 10 сумми|ро;ва,ння длительности Г тульсоа «ИЛИ, выходяой сигнал /с которой управляет ге-нератор-ом 6 серии.

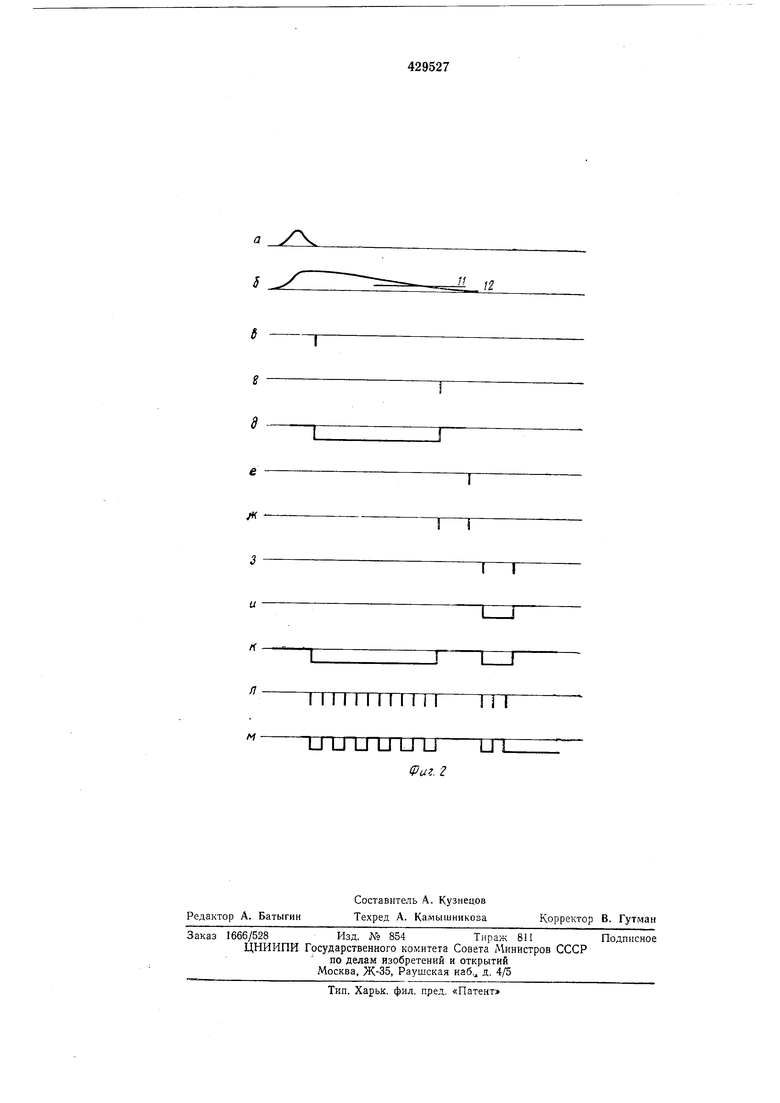

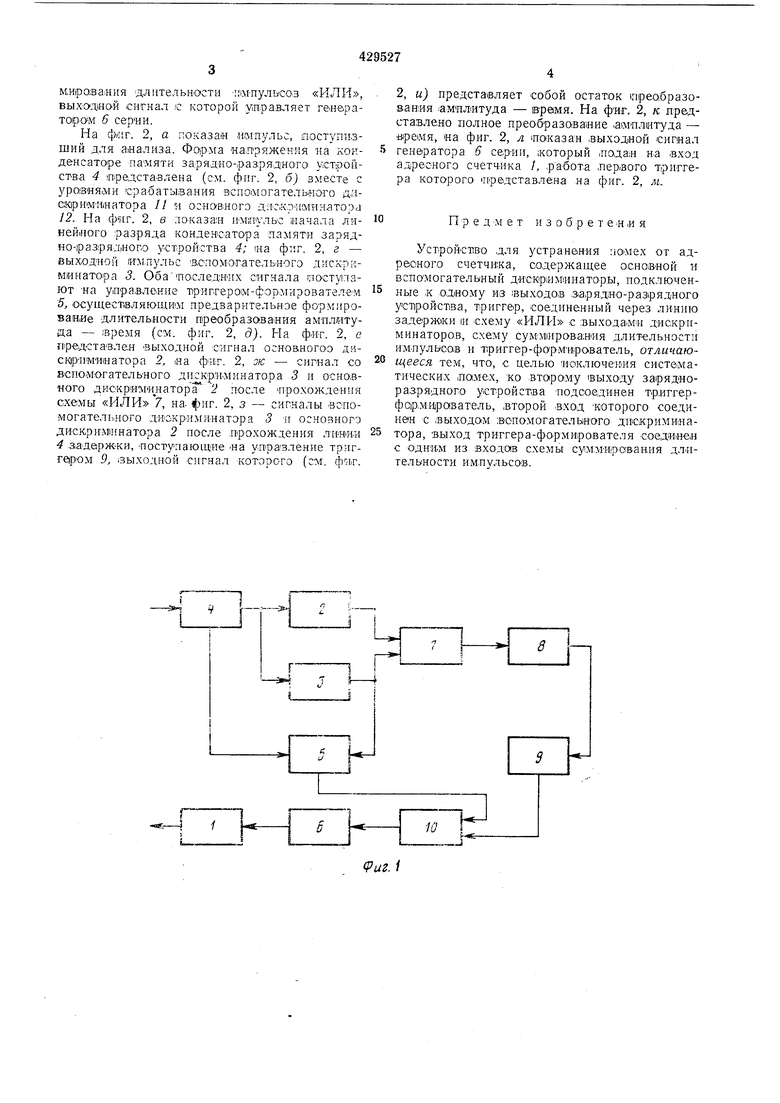

На ф)иг. 2, а показан импульс, поступнзший для айализа. Фарма напряжения на конденсаторе памяти за;рядно-1раз:ряд ного ycTipoftст-ва 4 тредставлена (см. фиг. 2, б) вместе с Зфо:знял1и срабатывания в-спомогательного длсвдримИиатора // я оснав:ногэ дЛСкоИминатора 12. На фиг. 2, в локаза:н и м;пульс начала линей.ного разряда конденсатора ламяти зарядно-|раз;ряД|НОпо устройства 4; та фиг. 2, г - выходной имлульс Вспомогательного дискриминатора 3. Оба последних сигнала ито-стулают -на управление триггером-формирователеМ 5, осуществляющим предварительное формирование длительиости преобразования амплитуда - 1время (см. фиг. 2, д). На фиг. 2, с предСтавле,н выходной основногоо диск)рИМИ1натора 2, яа фИг. 2, ж - сигнал со вспомогательного дискра-гминатора 3 и основного дискриМИ натора 2 после прохождения схемы «ИЛИ 7, на. фиг. 2, з - сигналы -всиомогательного дискр-иминатора 5 и основного дискр1гм1инатора 2 после .прохождения лИН1И.и 4 .задержки, поступающие «а улра-зление тригreipoM 9, ;выходиой сигнал которого (см. фиг.

2, и) предста вляет собой остаток inpe.0i6pa3oваняя .амллитуда - время. На фиг. 2, к представлено полное преобразоваиие .амплитуда - «ремя, «а фиг. 2, л показан .выходной сигнал генератора 6 сер-ии, который ,пода;Н на .вход адресного счетчика /, работа .первого триггера которого Представлена на фиг. 2, м.

Пред м е т изобретения

Устрой.спво .для устранения помех от адресного счетчи;ка, со.держащее ос.но;в«ой и вспомогательный дискрнм1инаторы, подключенные к о.дному из 1ВЫХОДОВ .з.аря.дно-раз1рядного усТ1ройства, триггер, соединенный через линию задержки ai Схему «ИЛИ с :выхода.М« дискриминаторов, схему сум М1Ирава:нИя длительности и.м.пулБсо:в И триггер-фор.МИ.рователь, отличающееся тем, что, с целью иioключeиiия систематических |Поме;х, ко второму ВЫХОДУ заряднора.з.рядного устройства подсоединен триггерфсрлщрователь, .второй БХОД которого соединен с .выходом всио.могательиого дискрими«атора, выход триггера-формирователя соедииен с одни.м из входов схемы с)лм.МИ(рО вания дл.птельности импульсо;В.

| название | год | авторы | номер документа |

|---|---|---|---|

| Амплитудный дифференциальный дискриминатор | 1978 |

|

SU1091311A1 |

| Устройство коррекции временных искажений | 1980 |

|

SU932648A1 |

| Устройство синхронизации фаз сигналов двух генераторов | 1978 |

|

SU771886A1 |

| Устройство для преобразования дискретных числоимпульсных посылок в непрерывный ЧИМ-сигнал | 1961 |

|

SU150303A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1970 |

|

SU287422A1 |

| Устройство фиксации временных положений сигналов | 1987 |

|

SU1443150A1 |

| Устройство для оценки напряженного состояния массива горных пород | 1989 |

|

SU1645512A1 |

| Многоканальное устройство регистрации пиков акустико-эмиссионных сигналов | 1987 |

|

SU1501718A1 |

| Цифровой частотный дискриминатор | 1975 |

|

SU542328A1 |

| Частотный компаратор | 1981 |

|

SU1023630A1 |

-

I I I I I I I I I И I ГПГ

м

U U U U или и

Фиг. 2

Даты

1974-05-25—Публикация

1971-11-17—Подача