1

Изобретение относится к области вычислительной техники и может быть использовано, например, при построении частотно-цифровых приборов.

Известны устройства, которые осуществляют синхронизацию выполнения двух независимых последовательностей операций, обусловленных поступлением на входы устройства двух соответствующих команд. В этих устройствах осуществляется запоминание прихода одной из команд и выполнение соответствующей ей последовательности после того, как произведена команда, поступившая первой.

Для формирования двух последовательностей операций требуется введение двух регистров или делителей, число состояний которых определяется количеством операций каждой из последовательностей. Известны также устройства, содержащие один регистр.

Однако очередность выполнения команд зависит от состояния тактирующего триггера. Кроме того, подобные устройства обладают малым быстродействием, так как начало выполнения той или другой команды определяется не только моментом подачи управляющего сигнала, но и состоянием регистра и тактирующего триггера.

В целях упрощения в предлагаемом устройстве одни из входов первой и второй схем «И соединены с выходом регистра, вход которого через схему «ИЛИ подключен к выходам третьей и четвертой схем «И. Одни входы последних соединены с одним из входов устройства, другие подключены соотзетственно к единичному выходу первого триггера и к нулевому выходу второго триггера. Управляющие входы дещифраторов подключены соответственно к нулевому и единичному выходам третьего триггера.

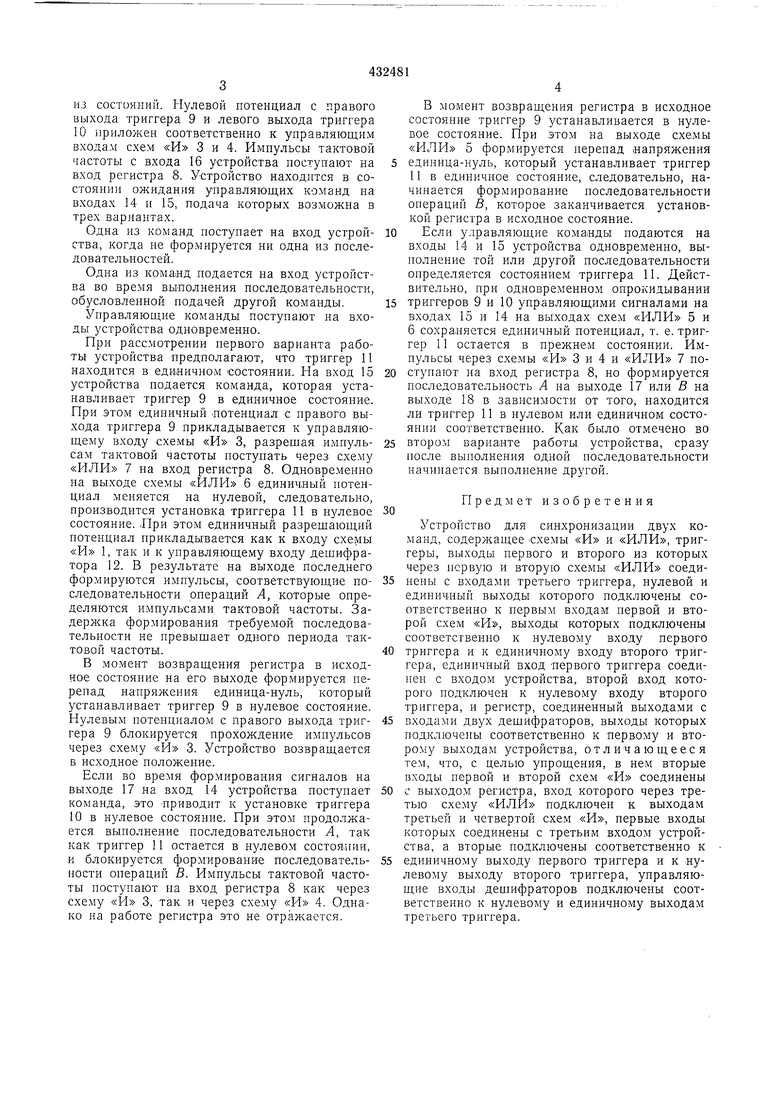

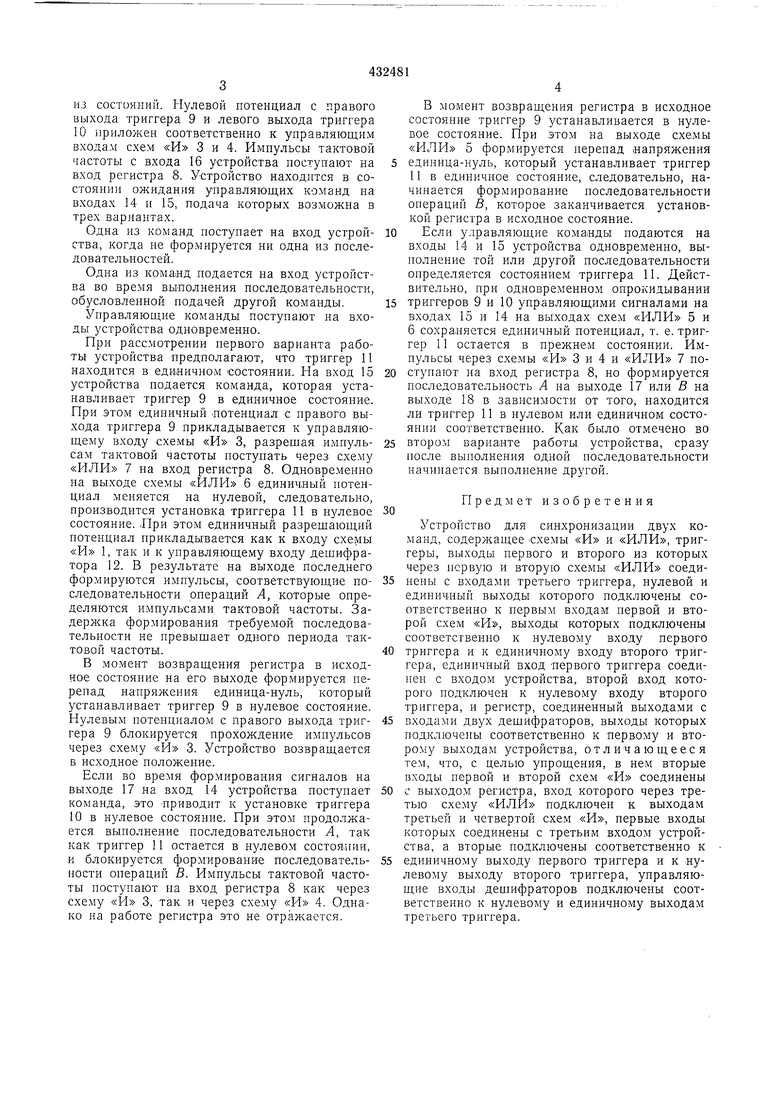

На чертеже показана схема предлагаемого устройства.

Устройство содержит схемы .«И 1-4, схемы «ИЛИ 5, 6 и 7, регистр 8, триггеры 9, 10 и И и дещифраторы 12 и 13 и имеет входы

14, 15 и 16 и выходы 17 и 18.

В описании используется позитивная логика и принято, что триггер находится в единичном состоянии, когда на его правом выходе присутствует единичный потенциал. Триггер

изменяет свое состояние при условии, что на его соответствующем входе единичный потенциал меняется на нулевой. Регистр л еняет свое состояние также при подаче на его вход перепада напряжения единица-нуль. Формирование сигналов на выходах 17 и 18 блокируется подачей «а управляющие входы дещифраторов нулевого потенциала.

В исходном положении триггер 9 находится в нулевом состоялии, триггер 10 - в единичном. Триггер 11 может находиться в любом

из состояний. Нулевой потенциал с правого выхода триггера 9 и левого выхода триггера 10 приложен соответственно к управляющим входам схем «И 3 и 4. Импульсы тактовой частоты с входа 16 устройства поступают на вход регистра 8. Устройство находится в состоянии ожидания управляющих команд на входах 14 и 15, подача которых возможна в трех вариантах.

Одна из команд поступает на вход устройства, когда не формируется ни одна из последовательностей.

Одна из команд подается на вход устройства во время выполнения последовательности, обусловленной подачей другой команды.

Управляющие команды поступают на входы устройства одновременно.

При рассмотрении первого варианта работы устройства предполагают, что триггер 11 находится в единичном состоянии. На вход 15 устройства подается команда, которая устанавливает триггер 9 в единичное состояние. При этом единичный потенциал с правого выхода триггера 9 прикладывается к управляющему входу схемы «И 3, разрешая импульсам тактовой частоты поступать через схему «ИЛИ 7 на вход регистра 8. Одновременно на выходе схемы «ИЛИ 6 единичный потенциал .меняется на нулевой, следовательно, производится установка триггера 11 в нулевое состояние. Лри этом единичный разрешающий потенциал прикладывается как к входу схемы «И 1, так и к управляющему входу дешифратора 12. В результате на выходе последнего формируются импульсы, соответствующие последовательности операций Л, которые определяются импульсами тактовой частоты. Задержка формирования требуемой последовательности не превышает одного периода тактовой частоты.

В момент возвращения регистра в исходное состояние на его выходе формируется перепад напряжения единица-нуль, который устанавливает триггер 9 в нулевое состояние. Нулевым потенциалом с правого выхОлТ;а триггера 9 блокируется прохождение импульсов через схему «И 3. Устройство возвращается в исходное положение.

Если во время формирования сигналов на выходе 17 на вход 14 устройства поступает команда, это приводит к установке триггера 10 в нулевое состояние. При этом продолжается выполнение последовательности А, так как триггер 11 остается в нулевом состоянии, и блокируется формирование последовательности операций В. Импульсы тактовой частоты поступают па вход регистра 8 как через схему «И 3, так и через схему «И 4. Однако на работе регистра это не отрал ается.

В момент возвращения регистра в исходное состояние триггер 9 устанавливается в нулевое состояние. При этом на выходе схемы «ИЛИ 5 формируется иерепад иапряжения единица-нуль, который устанавливает триггер 11 в единичное состояние, следовательно, начинается формирование последовательности оиераций В, которое заканчивается установкой регистра в исходное состояние.

Если управляющие команды подаются на входы 14 и 15 устройства одновременно, выполнение той или другой последовательности определяется состоянием триггера 11. Действительно, при одновременном опрокидывании

триггеров 9 и 10 управляющими сигналами на входах 15 и 14 на выходах схем «ИЛИ 5 и 6 сохраняется единичный потенциал, т. е. триггер 11 остается в прежнем состоянии. Импульсы через схемы «И 3 и 4 и «ИЛИ 7 поступают на вход регистра 8, но формируется последовательность Л на выходе 17 или В на выходе 18 в зависимости от того, находится ли триггер 11 в нулевом или единичном состоянии соответственно. Как было отмечено во

втором варианте работы устройства, сразу после выполнения одной последовательности начинается выполнение другой.

Предмет изобретения

Устройство для синхронизации двух команд, содержащее схемы «И и «ИЛИ, триггеры, выходы первого и второго из которых через первую и вторую схемы «ИЛИ соедипены с входа.ми третьего триггера, нулевой и единичный выходы которого подключены соответственно к первым входам первой и второй схем «И, выходы которых подключены соответственно к нулевому входу первого

триггера и к единичному входу второго триггера, единичный вход нервого триггера соединен с входом устройства, второй вход которого подключен к нулевому входу второго триггера, и регистр, соединенный выходами с

входами двух дешифраторов, выходы которых подключены соответственно к первому и второму выходам устройства, отличающееся тем, что, с целью упрощения, в нем вторые входы первой и второй схем «И соединены

о выходом регистра, вход которого через третью схему «ИЛИ подключен к выходам третьей и четвертой схем «И, первые входы которых соединены с третьим входом устройства, а вторые подключены соответственно к

единичному выходу первого триггера и к нулевому выходу второго триггера, управляющие входы дещифраторов подключены соответственно к нулевому и единичному выходам третьего триггера.

16

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ДВУХ КОМАНД | 1972 |

|

SU436341A1 |

| СИНХРОНИЗАТОР ДВУХ КОМАНДТ'2СВСОЮЗНД"; iU:.-;::rT.^ri,,.Tr|-K::-'r;.!v^: | 1973 |

|

SU374601A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1984 |

|

SU1188745A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1325501A1 |

| Устройство для формирования команд | 1977 |

|

SU622083A1 |

| Вторичные часы | 1976 |

|

SU651302A1 |

| Устройство для отладки вычислительной системы | 1986 |

|

SU1336015A1 |

| Устройство для сопряжения | 1978 |

|

SU723561A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КАНАЛАМИ | 1973 |

|

SU386395A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

Даты

1974-06-15—Публикация

1972-12-20—Подача