Изобретение относится к электроизмерительной вычислительной технике и может найти применение при построении частотно-цифровых приборов, в частности приборов, измерение в которых производится в примыкающих интервалах.

Известно устройство, которое осуществляет синхронизацию импульсов двух независимых одна от другой частот импульсами тактовой (опорной) частоты. Устройство содержит тактовый триггер и два одинаковых тракта, каждый из которых состоит из триггера, элемента совпадения и одновибратора.

Устройство обладает тем недостатком, что очередность появления выходных импульсов зависит не только от порядка поступления импульсов входных частот, но и от состояния тактового триггера. Если с приходом одного импульса входной частоты с выхода каждого тракта необходимо получить серию импульсов, управляющих рядом последователь;ных операций, триггеры трактов можно заменить на делители частоты или регистры. Однако при этом осуществление одной из последовательностей операций пе исключает выполнения в то же время другой.

Указанные недостатки не позволяют использовать устройство, когда требуется учитывать очередность поступления входных команд и запрещать выполнение одной из последовательностей операций на время выполнения второй.

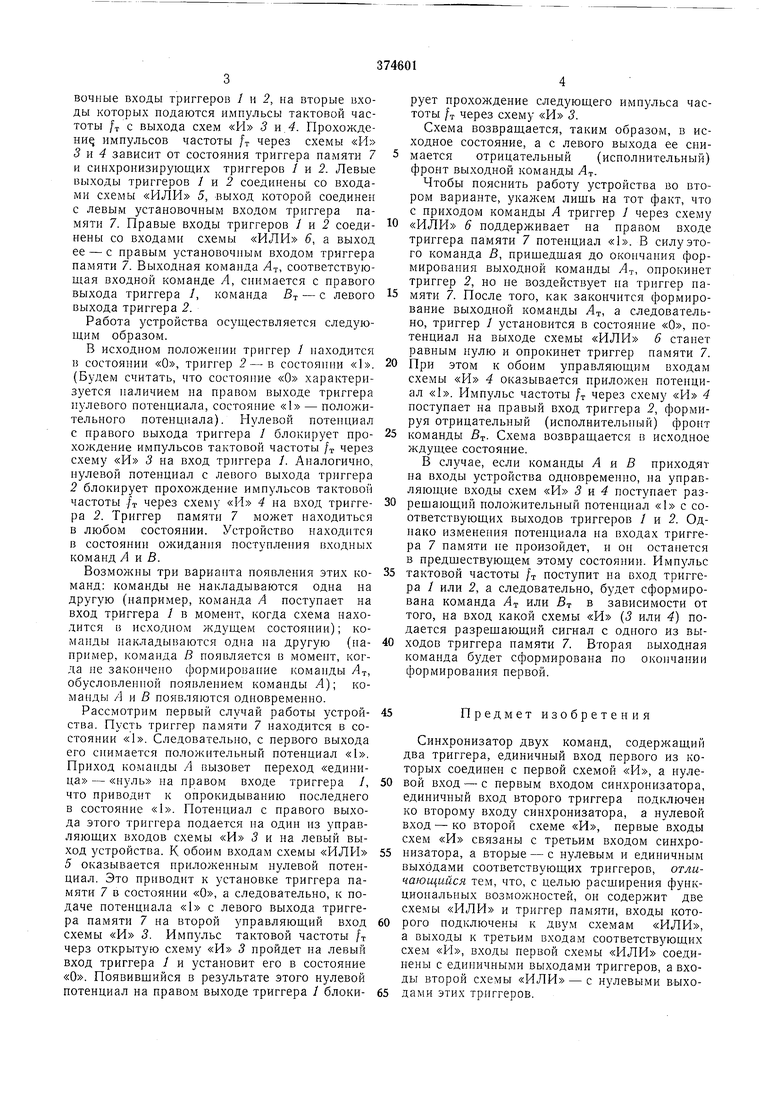

Для расширения функциональных возможностей предлагаемое устройство содержит две схемы «ИЛИ и триггер памяти, входы которого подключены к двум схемам «ИЛИ, а выходы к третьим входам соответствующих схем «И, входы первой схемы «ИЛИ соединены с единичными выходами триггеров, а входы

второй схемы «ИЛИ - с нулевыми выходами этих триггеров.

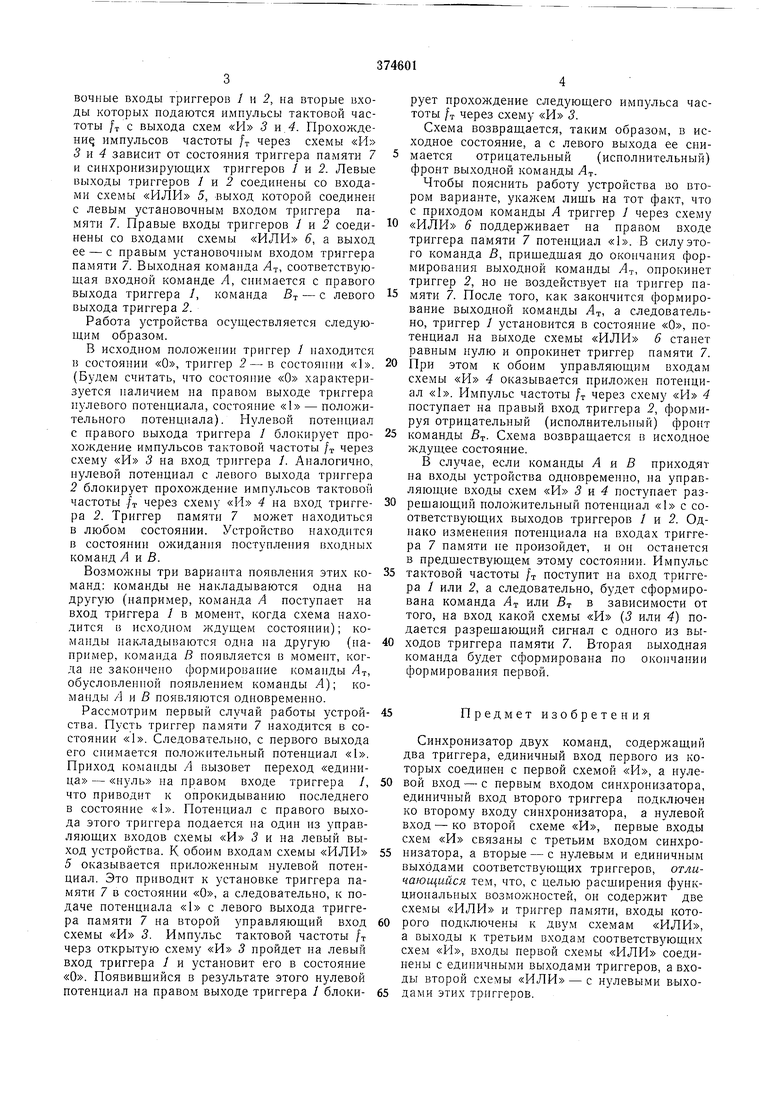

На чертеже изображена схема предлагаемого устройства. Устройство содержит триггеры 1 и 2, схемы

«И 3 к 4, схемы «ИЛИ 5 и 6, триггеры 7 памяти.

Если синхронизатор осуществляет синхронизацию двух отдельных команд, точки а и b на чертеже соединяют. Если требуется производить синхронизацию двух независимых последовательностей операций, между точками а к b необходимо установить делители или регистры, число состояний которых определяется количеством необходимых операций.

Для простоты рассмотрим случай синхронизации двух независимых команд (точки а и b соединены).

Отдельные узлы устройства связаны между собой следующими функциональными зависимостями. Команды А и В подаются на установочные входы триггеров / и 2, на вторые входы которых подаются импульсы тактовой частоты /т с выхода схем «И 3 и,4. Прохождени импульсов частоты /т через схемы «И 3 и 4 зависит от состояиия триггера памяти 7 и синхропизирующих триггеров 1 и 2. Левые выходы триггеров I и 2 соединены со входами схемы «ИЛИ 5, выход которой соединен с левым установочным входом триггера памяти 7. Правые входы триггеров 1 и 2 соединены со входами схемы «ИЛИ 6, а выход ее - с правым установочным входом триггера памяти 7. Выходная команда Лт, соответствующая входной команде Л, снимается с правого выхода триггера У, команда Вт - с левого выхода триггера 2.

Работа устройства осупдествляется следующим образом.

В исходном положении триггер / иаходится в состоянии «О, триггер 2 - в состоянии «1. (Будем считать, что состояние «О характеризуется наличием на правом выходе триггера нулевого потенциала, состояние «Ь - положительного потенциала). Нулевой потенциал с нравого выхода триггера 7 блокирует прохождение импульсов тактовой частоты /т через схему «PI 3 на вход триггера /. Аналогично, нулевой потенциал с левого выхода триггера 2 блокирует прохождение импульсов тактовой частоты /т через схему «И 4 на вход триггера 2. Триггер памяти 7 может находиться в любом состояиии. Устройство находится в состоянии ожидания поступления входных команд А ц В.

Возможны три варианта появления этих команд: команды не накладываются одна на другую (например, команда А поступает на вход триггера 1 в момент, когда схема находится в исходном ждущем состоянии); команды накладываются одна иа другую (например, команда В появляется в момент, когда не закончено формирование команды Лт, обусловленной появлением команды Л); команды Л и В появляются одновременно.

Рассмотрим первый случай работы устройства. Пусть триггер памяти 7 находится в состоянии «1. Следовательно, с первого выхода его снимается положительный потенциал «1. Приход комаиды Л вызовет переход «единица - «нуль на правом входе триггера /, что приводит к опрокидыванию последнего в состояние «1. Потенциал с правого выхода этого триггера подается на один нз управляющих входов схемы «И 3 и на левый выход зстройства. К обоим входам схемы «ИЛИ 5 оказывается приложенным нулевой потенциал. Это приводит к устаиовке триггера памяти 7 в состоянии «О, а следовательно, к подаче потенциала «1 с левого выхода триггера памяти 7 на второй управляющий вход схемы «И 3. Импульс тактовой частоты /т черз открытую схему «И 5 пройдет на левый вход триггера / и установит его в состояние «О. Появившийся в результате этого нулевой потенциал на правом выходе триггера / блокирует прохождение следующего импульса частоты /т через схему «И 3.

Схема возвращается, таким образом, в исходное состояние, а с левого выхода ее снимается отрицательный (исполнительный) фронт выходной команды Лт.

Чтобы пояснить работу устройства во втором варианте, укажем лищь на тот факт, что с приходом команды Л триггер J через схему

«ИЛИ 6 поддерживает на правом входе триггера памяти 7 потенциал «1. В силу этого команда В, прищедшая до окончания формирования выходной команды Лт, опрокинет триггер 2, но не воздействует на триггер намяти 7. После того, как закончится формирование выходной команды Лт, а следовательно, триггер / установится в состояние «О, нотенциал на выходе схемы «ИЛИ 6 станет равным нулю и опрокинет триггер памяти 7.

При этом к обоим управляющим входам схемы «И 4 оказывается приложен потенциал «1. Импульс частоты /т через схему «И 4 поступает на правый вход триггера 2, формируя отрицательный (исполнительпый) фронт

команды В. Схема возвращается в исходное ждущее состояние.

В случае, если команды А я В приходят на входы устройства одновременно, на управляющие входы схем «И 3 и 4 поступает разрешающий положительный потенциал «1 с соответствующих выходов триггеров 1 и 2. Одиако изменения потенциала на входах триггера 7 памяти не произойдет, и ои останется в предществующем этому состоянии. Импульс

тактовой частоты f поступит иа вход триггера / или 2, а следовательно, будет сформирована команда Лт или Вт в зависимости от того, на вход какой схемы «И (3 или 4) подается разрещающий сигнал с одного из выходов триггера намяти 7. Вторая выходная команда будет сформирована по окончании формирования первой.

Предмет изобретения

Синхронизатор двух команд, содерл ащий два триггера, единичный вход первого из которых соединен с первой схемой «И, а нулевой вход - с первым входом синхронизатора, едииичный вход второго триггера подключен ко второму входу синхронизатора, а нулевой вход - ко второй схеме «И, первые входы схем «И связаны с третьим входом синхронизатора, а вторые - с нулевым и единичным выходами соответствующих триггеров, отличающийся тем, что, с целью расширения функциональных возможностей, он содержит две схемы «ИЛИ и триггер памяти, входы которого подключены к двум схемам «ИЛИ, а выходы к третьим входам соответствующих схем «И, входы первой схемы «ИЛИ соединены с единичными выходами триггеров, а входы второй схемы «ИЛИ - с нулевыми выходами этих триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации | 1977 |

|

SU734645A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ДВУХ КОМАНД | 1972 |

|

SU432481A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Устройство для приведения матрицы к треугольной идемпотентной форме | 1983 |

|

SU1312610A2 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Устройство для числового программного управления станками | 1985 |

|

SU1291928A1 |

| Способ фотоэлектрического определения толщины листового изделия и устройство для его осуществления | 1983 |

|

SU1190191A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| ФОРМИРОВАТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 2013 |

|

RU2528141C1 |

Авторы

Даты

1973-01-01—Публикация