.i

3150

Изобретение относится к вычислительной технике и может быть использовано для контроля и испытаний на надежность запоминающих устройств на цилиндрических магнитных доменах .

Цель изобретения - расширение области применения за счет возможности изменения параметров сигналов устройства и повьппение достоверности испытаний на надежность доменной памяти.

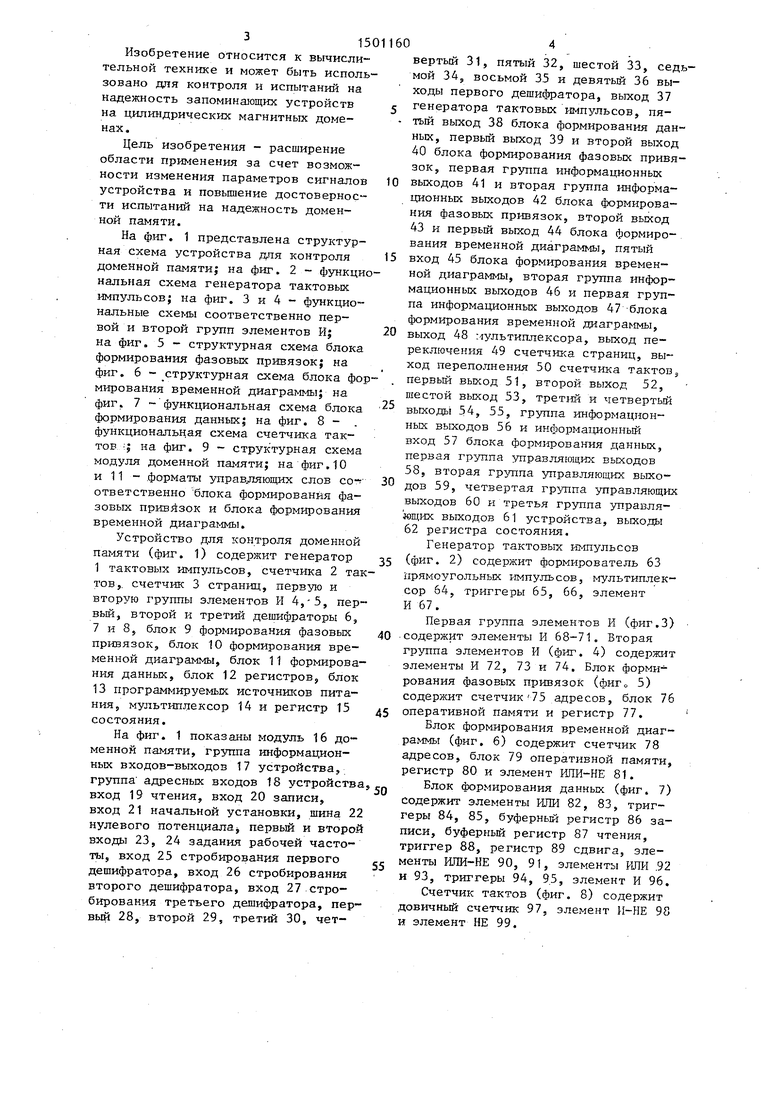

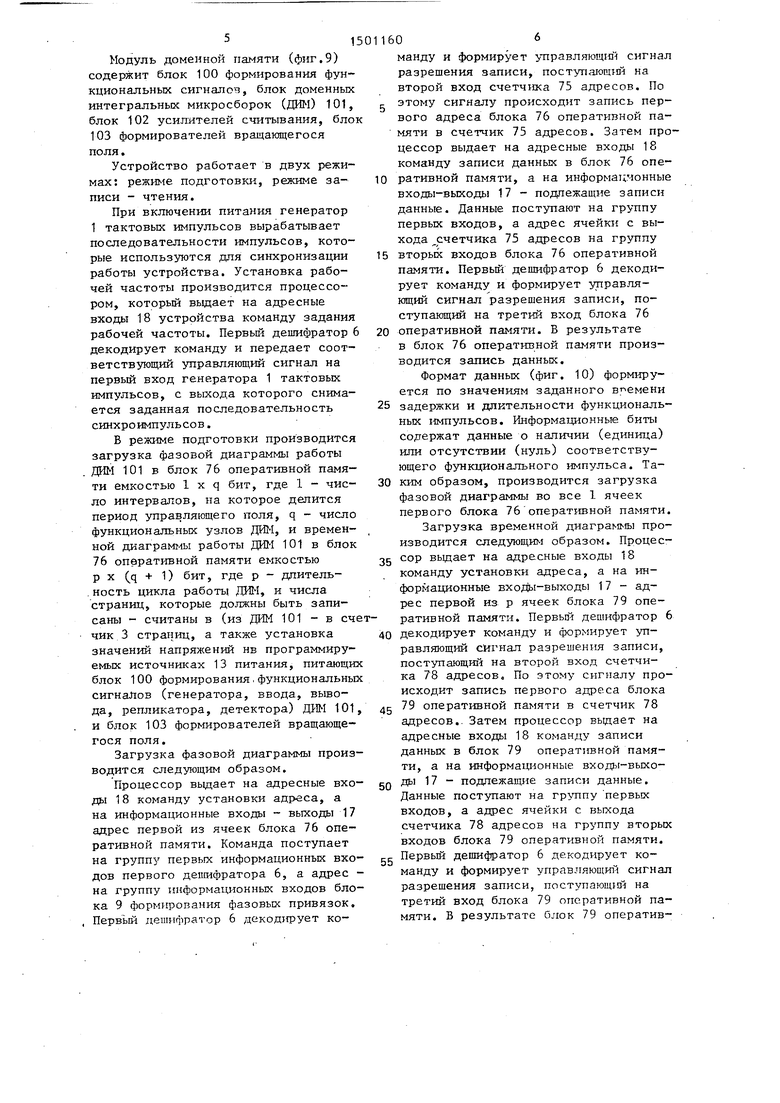

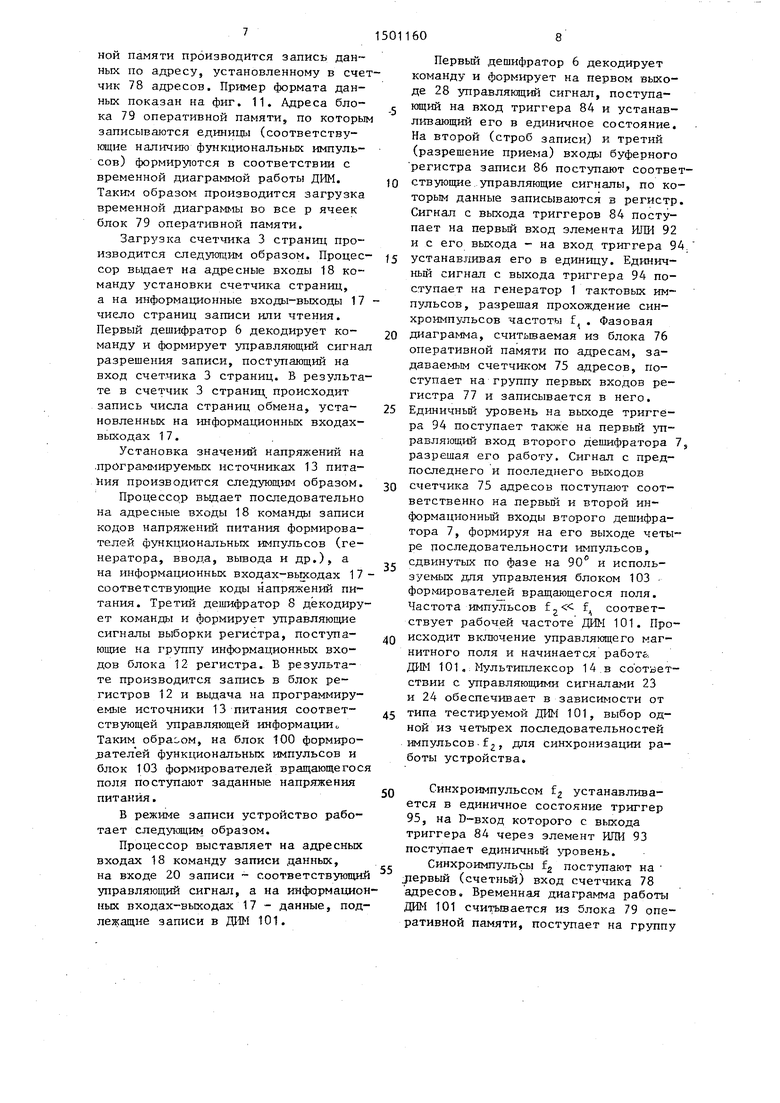

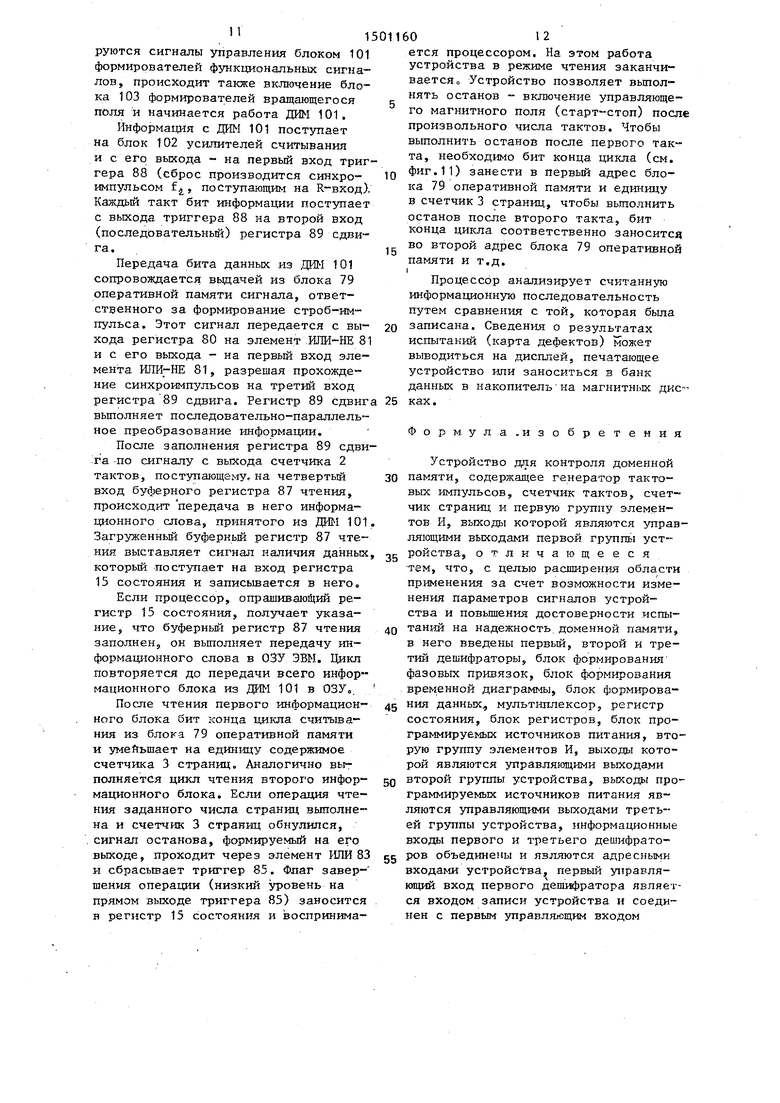

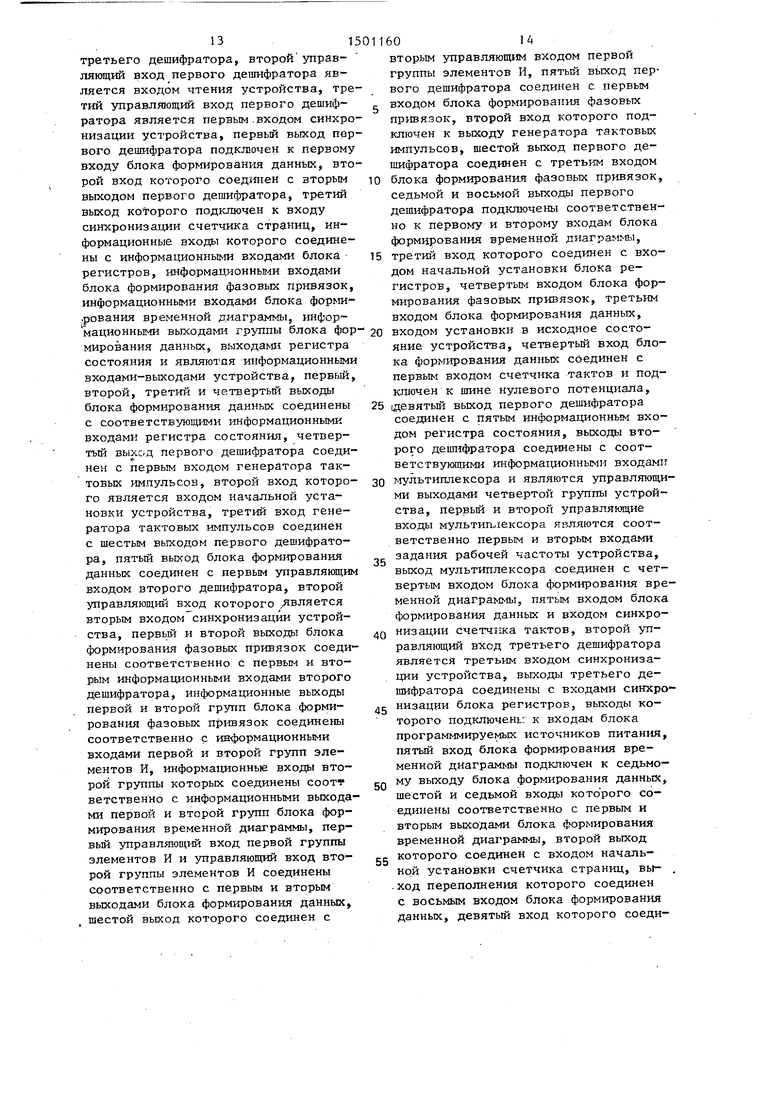

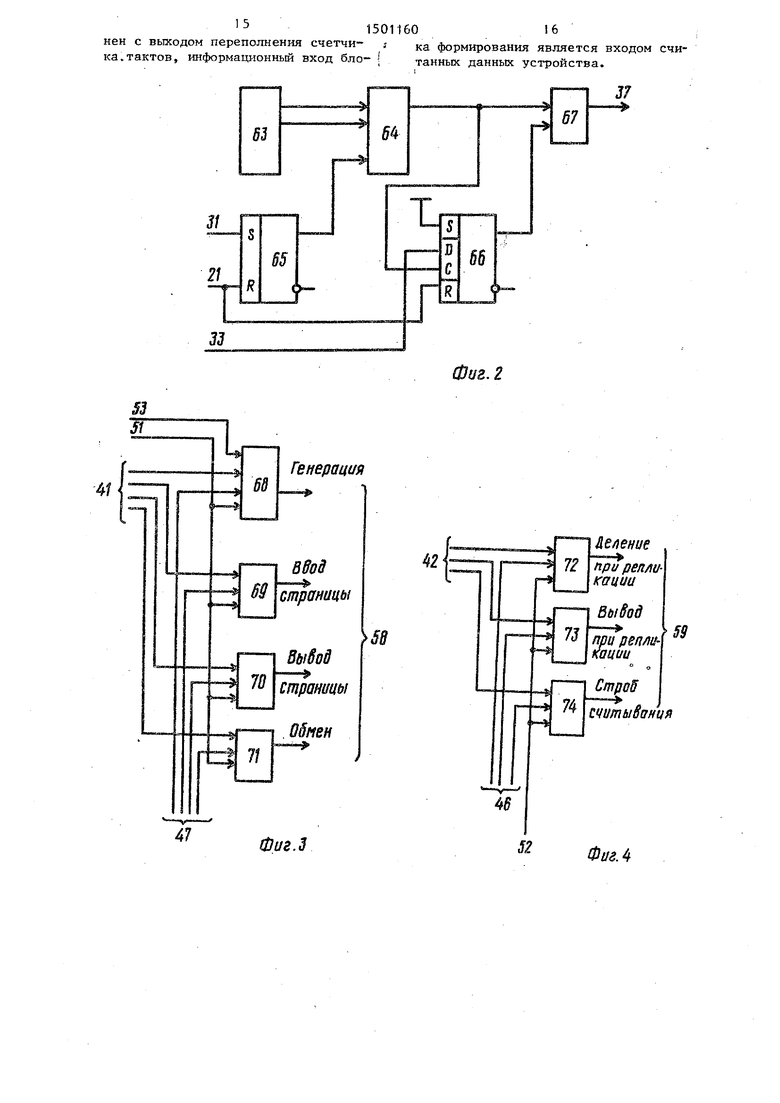

На фиг. 1 представлена структурная схема устройства для контроля доменной памяти| на фиг. 2 - функциональная схема генератора тактовых импульсов; на фиг. 3 и 4 - функциональные схемы соответственно первой и второй групп элементов И| на фиг. 5 - структурная схема блока формирования фазовых привязок; на фиг. 6 - структурная схема блока формирования временной диаграммы; на фиг. 7 - функциональная схема блока формирования данных; на фиг. 8 - . функциональцая схема счетчика тактов :; на фиг. 9 - структурная схема модуля доменной памяти; на фиг.10 и 11 - форматы управляющих слов ответственно блока формирования фазовых привязок и блока формирования временной диаграммы.

Устройство для контроля доменной памяти (фиг. 1) содержит генератор 1 тактовых импульсов, счетчика 2 тактов,, счетчик 3 страниц, первую и вторую группы элементов И 4, 5, первый, второй и третий дешифраторы 6, 7 и 8, блок 9 формирования фазовых привязок, блок 10 формирования временной диаграммы, блок 11 формирования данных, блок 12 регистров, блок 13 программируемых источншсов питания, мультиплексор 14 и регистр 15 состояния.

На фиг. 1 показ аны модуль 16 доменной памяти, группа информационных входов-выходов 17 устройства, группа адресных входов 18 устройства вход 19 чтения, вход 20 записи, вход 21 начальной установки, шина 22 нулевого потенциалаj первый и второй входы 23, 24 задания рабочей частоты, вход 25 стробирования первого дешифратора, вход 26 стробирования второго дешифратора, вход 27 стро- бирования третьего дешифратора, первый 28, второй 29, третий 30, чет4

вертый 31, пятый 32, шестой 33, седьмой 34, восьмой 35 и девятый 36 выходы первого дешифратора, выход 37

генератора тактовых импульсов, пя- тый выход 38 блока формирования данных, первый выход 39 и второй выход 40 блока формирования фазовых привязок, первая группа информационных

выходов 41 и вторая группа информационных выходов 42 блока формирования фазовых привязок, второй выход 43 и первый выход 44 блока формирования временной диаграммы, пятый

вход 45 блока формирования временной диаграммы, вторая группа информационных выходов 46 и первая группа информационных выходов 47 блока формирования временной диаграммы,

выход 48 мультиплексора, выход переключения 49 счетчика страниц, выход переполнения 50 счетчика тактовj первый выход 51, второй выход 52, шестой выход 53, третий и четвертый

выходь 54, 55, группа информационных выходов 56 и ино1юрмаи;ионный вход 57 блока формирования данных, первая группа управляющих выходов 58, вторая гр уппа управляющих выходов 59, четвертая группа управляющих выходов 60 и третья группа управляющих выходов 61 устройства, выходы 62 регистра состояния.

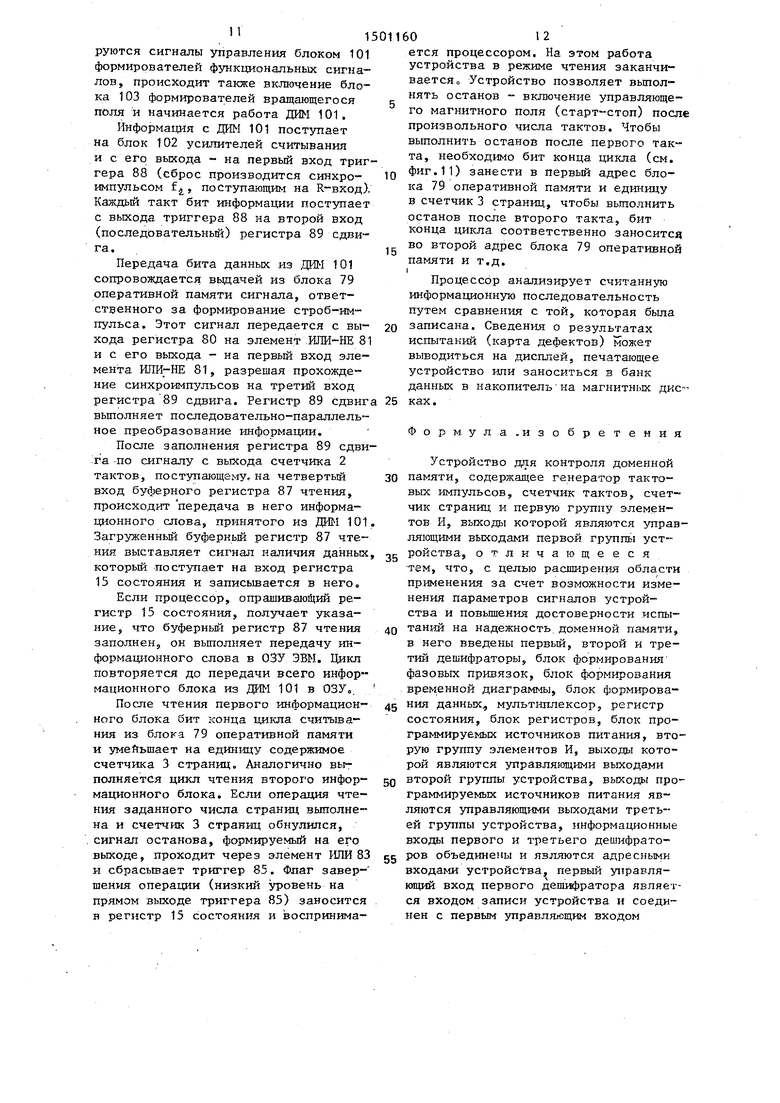

Генератор тактовых ш-шульсов

(фиг. 2) содержит формирователь 63 Прямоугольных j-гмпульсов, мультиплексор 64, триггеры 65, 66, элемент И 67.

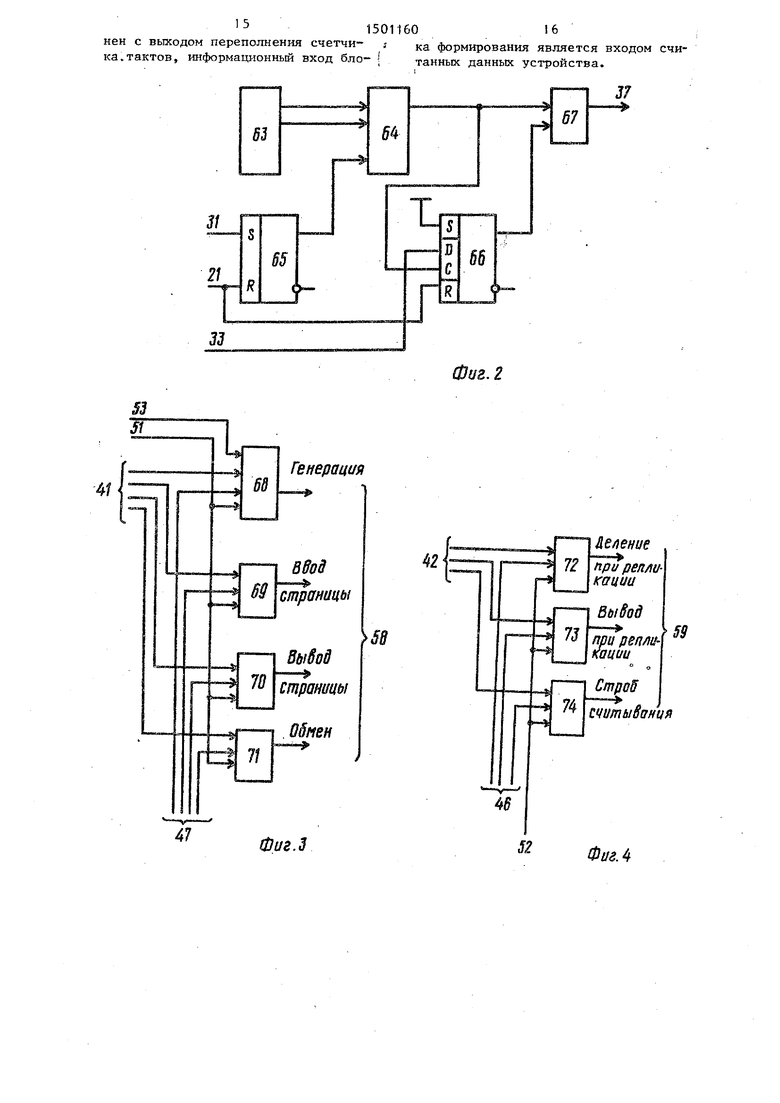

Первая группа элементов И (фиг.З)

-содержит элементы И 68-71. Вторая группа элементов И (фиг. 4) содержит элементы И 72, 73 и 74. Блок форми рования фазовых привязок (фиг 5) содержит счетчик 75 адресов, блок 76

оперативной памяти и регистр 77.

Блок формирования временной диаграммы (фиг. 6) содержит счетчик 78 адресов, блок 79 оперативной памяти, регистр 80 и элемент ИЛИ-НЕ 81.

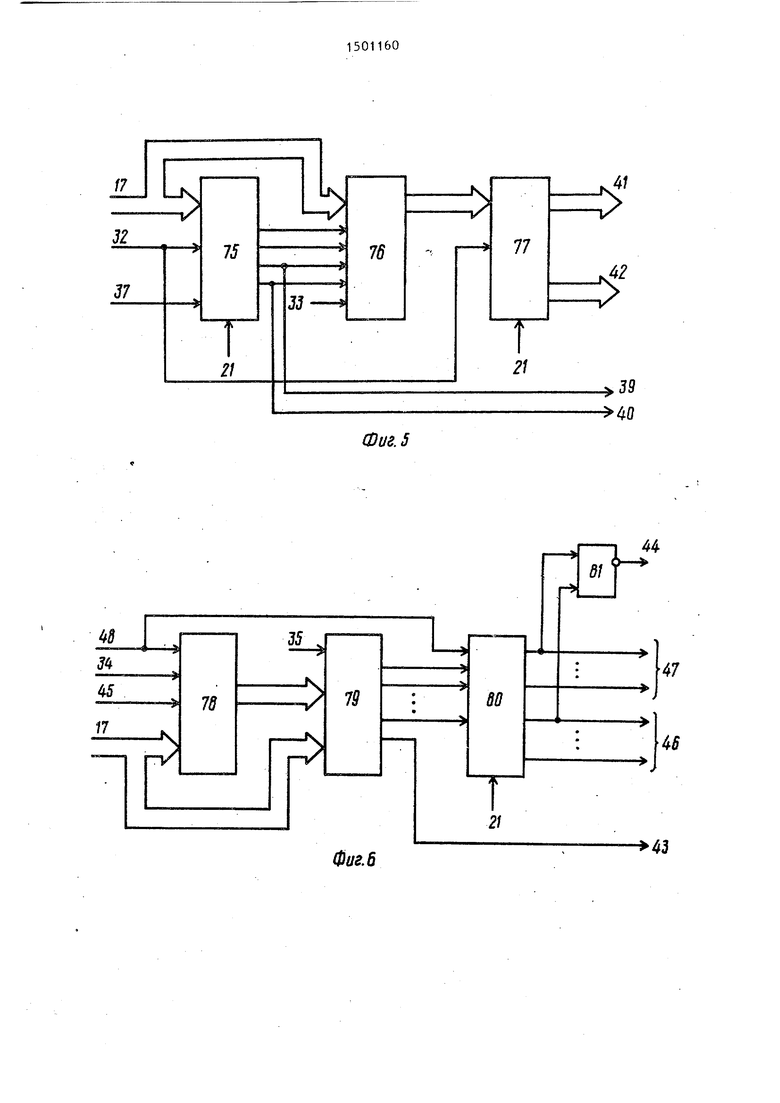

Блок формирования данных (фиг. 7) содержит элементы ИЖ 82, 83, триггеры 84, 85, буферньй регистр 86 записи, буферный регистр 87 чтения, триггер 88, регистр 89 сдвига, элементы ИЛИ-НЕ 90, 91, элементы ИЛИ .92 и 93, триггеры 94, 95, элемент И 96, Счетчик тактов (фиг. 8) содержит довичный счетчик 97, элемент И-НЕ 98 и элемент НЕ 99.

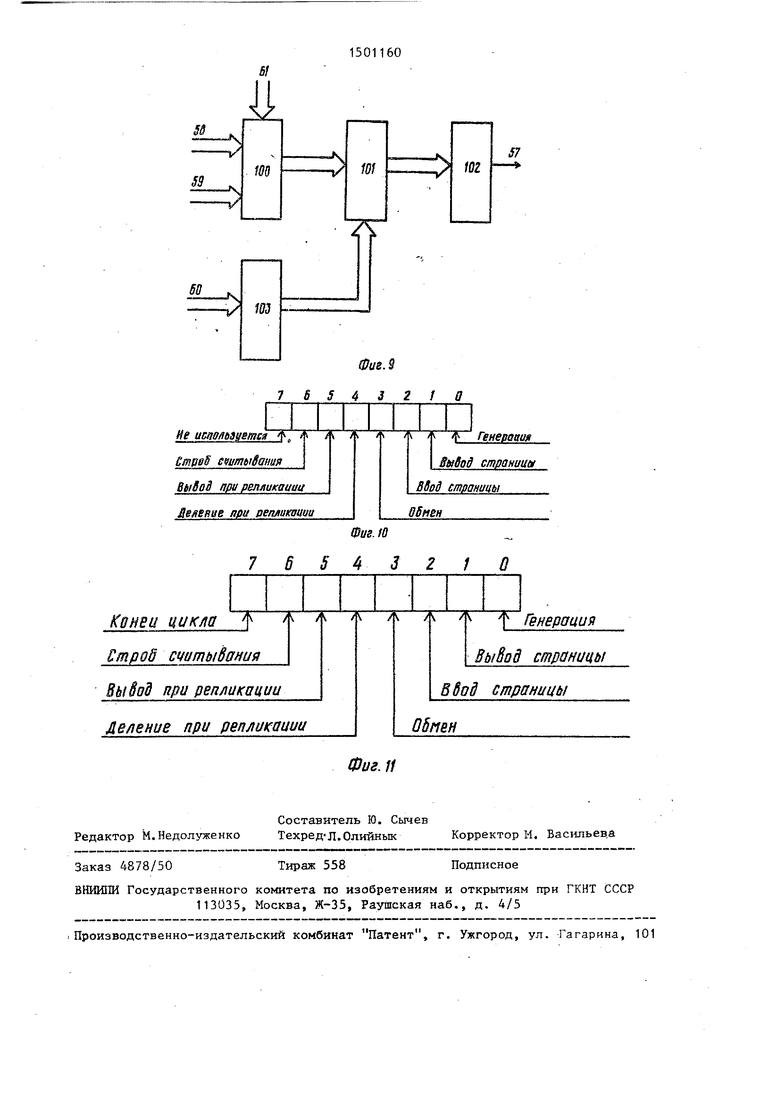

Модуль доменной памяти (фиг.9) содержит блок 100 формирования функциональных сигналов, блок доменных интегральньЕХ микросборок (ДИМ) 101, блок 102 усилителей считывания, блок 103 формирователей вращающегося поля.

Устройство работает в двух режимах: режиме подготовки, режиме записи - чтения.

При включении питания генератор 1 тактовых импульсов вырабатывает последовательности импульсов, которые используются для синхронизации работы устройства. Установка рабочей частоты производится процессором, который вьщает на адресные входы 18 устройства команду задания рабочей частоты. Первьш дешифратор 6 декодирует команду и передает соответствующий управляющий сигнал на первый вход генератора 1 тактовых импульсов, с выхода которого снимается заданная последовательность синхроимпульсов.

В режиме подготовки производится загрузка фазовой диаграммы работы ДИМ 101 в блок 76 оперативной памяти емкостью 1 X q бит, где 1 - число интервалов, на которое делится период управляющего поля, q - число функционапьньЕх: узлов ДИМ, и временной диаграммы работы ДИМ 101 в блок 76 оперативной памяти емкостью р X (q + 1) бит, где р - дпитель- .ность цикла работы ДИМ, и числа страниц, которые должны быть записаны - считаны в (из ДИМ 101 - в счетчик 3 страниц, а также установка значений напряжений нв программируемых источниках 13 питания, питающих блок 100 формирования.функциональных сигналов (генератора, ввода, вывода, репликатора, детектора) ДИМ 101, и блок 103 формирователей вращающегося поля.

Загрузка фазовой диаграммы производится следующим образом.

Процессор выдает на адресные входы 18 команду установки адреса, а на информационные входы - выходы 17 адрес первой из ячеек блока 76 оперативной памяти. Команда поступает

10

20

25

манду и формирует управляющий сигн разрешения записи, поступающей на второй вход счетчика 75 адресов. П этому сигналу происходит запись пе вого адреса блока 76 оперативной п мяти в счетчик 75 адресов. Затем п цессор выдает на адресные входы 18 команду записи данных в блок 76 оп ративной памяти, а на информа1;монн входы-выходы 17 - подлежащие запис данные. Данные поступают на группу первых входов, а адрес ячейки с вы хода счетчика 75 адресов на группу

15 вторых входов блока 76 оперативной памяти. Первьй дещифратор 6 декоди рует команду и формирует управляющий сигнал разрешения записи, поступающий на третий вход блока 76 оперативной памяти. В результате в блок 76 оперативной памяти произ водится запись данных.

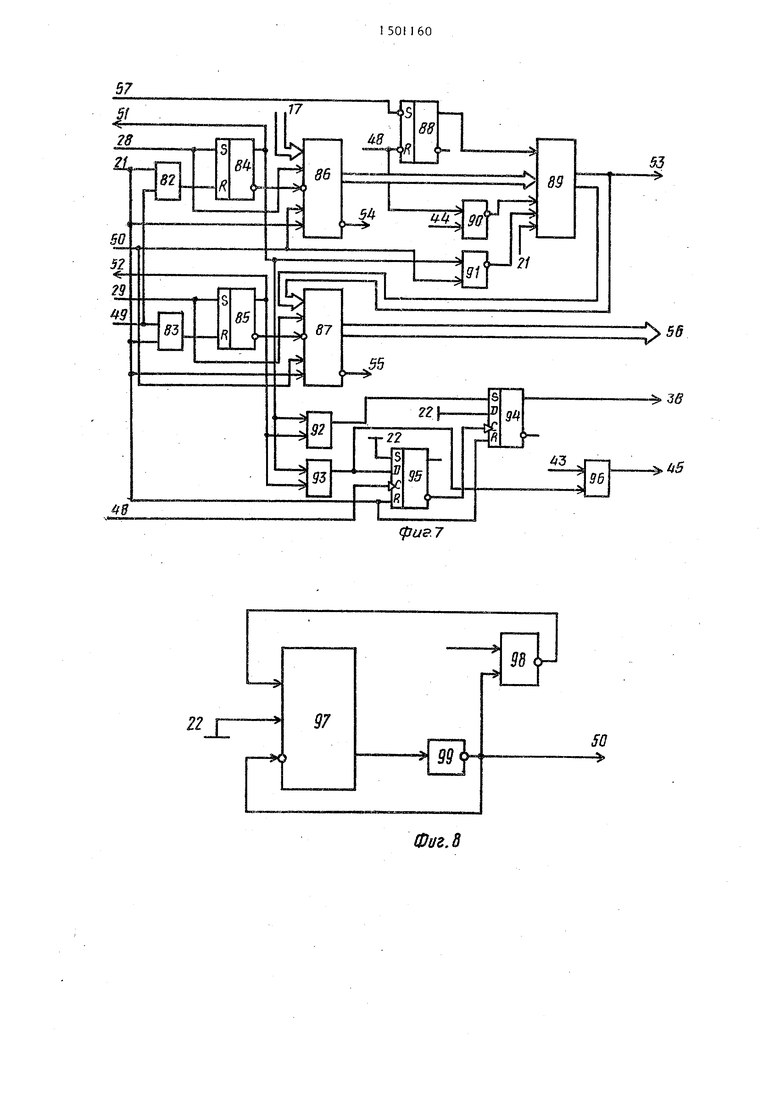

Формат данных (фиг. 10) формируется по значениям заданного в - емени задержки и длительности функциональ ных Iiмпyльcoв. Информационные биты содержат данные о наличии (единица или отсутствии (нуль) соответствующего функционального импульса. Таким образом, производится загрузка фазовой диаграммы во все 1 ячеек первого блока 76 операттшной памяти Загрузка временной диаграммы про изводится следующим образом. Процес

35 сор выдает на адресные входы 18 команду установки адреса, а на информационные входы-выходы 17 - адрес первой из р ячеек блока 79 оперативной памяти. nepBbtfi дешифратор декодирует команду и формирует управляющий сигнал разрешения записи, поступающий на второй вход счетчика 78 адресов. По этому сигналу про исходит запись первого адреса блока 79 оперативной памяти в счетчик 78 адресов.. Затем процессор выдает на адресные входы 18 команду записи данных в блок 79 оперативной памяти, а на информационные вход1з1-выхо- ды 17 - подлежащие записи данные. Данные поступают на группу первых входов, а адрес ячейки с выхода счетчика 78 адресов на группу вторы входов блока 79 оперативной памяти.

30

40

45

50

на группу первых информационных вхо- 55 Первый дещифратор 6 декодирует кодов первого дешифратора 6, а адрес - на группу информационных входов блока 9 формирования фазовых привязок. Первьш дешифратор 6 декод1Фует команду и формирует управляющий сигна разрешения записи, поступающ1ш на третий вход блока 79 оперативной па мяти. В результате блок 79 оператив

0

0

5

манду и формирует управляющий сигнал разрешения записи, поступающей на второй вход счетчика 75 адресов. По этому сигналу происходит запись первого адреса блока 76 оперативной памяти в счетчик 75 адресов. Затем процессор выдает на адресные входы 18 команду записи данных в блок 76 оперативной памяти, а на информа1;монные входы-выходы 17 - подлежащие записи данные. Данные поступают на группу первых входов, а адрес ячейки с выхода счетчика 75 адресов на группу

5 вторых входов блока 76 оперативной памяти. Первьй дещифратор 6 декодирует команду и формирует управляющий сигнал разрешения записи, поступающий на третий вход блока 76 оперативной памяти. В результате в блок 76 оперативной памяти производится запись данных.

Формат данных (фиг. 10) формируется по значениям заданного в - емени задержки и длительности функциональных Iiмпyльcoв. Информационные биты содержат данные о наличии (единица) или отсутствии (нуль) соответствующего функционального импульса. Таким образом, производится загрузка фазовой диаграммы во все 1 ячеек первого блока 76 операттшной памяти. Загрузка временной диаграммы производится следующим образом. Процес5 сор выдает на адресные входы 18 команду установки адреса, а на информационные входы-выходы 17 - адрес первой из р ячеек блока 79 оперативной памяти. nepBbtfi дешифратор 6 декодирует команду и формирует управляющий сигнал разрешения записи, поступающий на второй вход счетчика 78 адресов. По этому сигналу происходит запись первого адреса блока 79 оперативной памяти в счетчик 78 адресов.. Затем процессор выдает на адресные входы 18 команду записи данных в блок 79 оперативной памяти, а на информационные вход1з1-выхо- ды 17 - подлежащие записи данные. Данные поступают на группу первых входов, а адрес ячейки с выхода счетчика 78 адресов на группу вторых входов блока 79 оперативной памяти.

0

0

5

0

Первый дещифратор 6 декодирует команду и формирует управляющий сигнал разрешения записи, поступающ1ш на третий вход блока 79 оперативной памяти. В результате блок 79 оперативной памяти производится запись дан ных по адресу, установленному в счетчик 78 адресов. Пример формата данных показан на фиг, 11, Адреса блока 79 оперативной памяти, по которым записываются единицы (соответствующие наличию фзгнкциональньк импуль- сов) формируются в соответствии с временной диаграммой работы ДИМ, Таки14 образом производится загрузка временной диаграммы во все р ячеек блок 79 оперативной памяти.

Загрузка счетчика 3 страниц производится следующим образом. Процессор выдает на адресные входы 18 команду установки счетчика страниц, а на информационные входы-выходы 17 число страниц записи или чтения. Первый дешифратор 6 декодирует команду и формирует управляющий сигнал разрешения записи, поступающий на вход счетчика 3 страниц, В результате в счетчик 3 страниц происходит запись числа страниц обмена, установленных на информационных входах- выходах 17,

Установка значений напряжений на .программируемых источниках 13 пита- 1-шя производится следующим образом. Процессор выдает последовательно на адресные входы 18 команды записи кодов напряжений питания формирователей функциональных импульсов (генератора, ввода, вывода и др,), а на информационных входах-выходах 17 соответствующие коды напряжений питания. Третий дешифратор 8 декодирует команды и формирует управляющие сигналы выборки регистра, поступающие на группу информационных входов блока 12 регистра, В результате производится запись в блок регистров 12 и вьщача на программируемые источники 13 питания соответствующей управляющей информации Таким образом, на блок 100 формиро- лател ей функциональных импульсов и блок 103 формирователей вращающегос поля поступают заданные напряжения питания,

В режиме записи устройство работает следующим образом.

Процессор выставляет на адресных входах 18 команду записи данных, на входе 20 записи соответствующий управляющий сигнал, а на информационых входах-выходах 17 - данные, подлежащие записи в ДИМ 101,

Первый дешифратор 6 декодирует команду и формирует на первом выходе 28 управляющий сигнал, поступа- ющий на вход триггера 84 и устанавливающий его в единичное состояние. На второй (строб записи) и третий (разрешение приема) входы буферного регистра записи 86 поступают соответствующие управляющие сигналы, по которым данные записываются в регистр. Сигнал с выхода триггеров 84 поступает на первый вход элемента ИЛИ 92 и с его выхода - на вход триггера 94.

устанавливая его в единицу. Единичный сигнал с выхода триггера 94 поступает на генератор 1 тактовых импульсов, разрешая прохождение синхроимпульсов частоты f , Фазовая

диаграмма, считьшаемая из блока 76 оперативной памяти по адресам, задаваемым счетчиком 75 адресов, поступает на группу первых входов регистра 77 и записывается в него,

Единичньш уровень на выходе триггера 94 поступает также на первый управляющий вход второго дешифратора 7, разрешая его работу. Сигнал с предпоследнего и последнего выходов

счетчика 75 адресов поступают соответственно на лервьй и второй информационный входы второго дешифратора 7, формируя на его выходе четыре последовательности импульсов,

сдвинутых по фазе на 90 и используемых для управления блоком 103 . формирователей вращающегося поля. Частота импульсов fj , соответствует рабочей частоте 101, Происходит включение управляющего магнитного поля и начинается работе, ДРШ 101,: Мультиплексор 14.в соответствии с управляющиьш сигналами 23 и 24 обеспечивает в зависимости от

типа тестируемой ДИМ 101, выбор одной из четьфех последовательностей импульсов 2, для синхронизации работы устройства.

Синхроимпульсом f устанавливается в единичное состояние триггер 95, на D-вход которого с выхода триггера 84 через элемент ИЛИ 93 поступает единичный тровень.

Синхроимпульсы fg поступают на .рервый (счетный) вход счетчика 78 адресов. Временная диаграмма работы ДИМ 101 считьшается из блока 79 оперативной памяти, поступает на группу

9 ,

входов регистров 8 и записьтается в него.

Из регистра 77 и регистра 80 фазо вал и временная диаграммы поступают на первую группу элементов И 4, на выходе которой формируются сигналы управления блоком 100 формирования функциональных сигналов.

Последовательность импульсов час- тотой поступает на счетньй вход счетчика 2 тактов. После отсчета числа тактов, равных разрядности слова, на выходе 50 счетчика тактов появляется сигнал высокого уровня. Этот сигнал поступает на четвертый вход буферного регистра 86 записи, а через элемент ШШ-НЕ 90 - на четвертый вход регистра 89 сдвига. В результате происходит передача данных из буферного регистра 86 записи в регистр 89 сдвига.

Информация с первого разряда регистра 80 ответственного за формирование импульсоа генераци, поступа- ет на первый вход элемента ИЛИ-НЕ 81 и с его выхода на первый вход элемента ИЛИ-НЕ 90. Если генерация раз- решена (активная зона), импульсы поступают на третий вход регистра 89 сдвига. Регистр.89 сдвига вьшолняет параллельно-последовательное преобразование информации, которая поступает с первого выхода на четвертый вход 53 элемента И 68 из первой группы элементов И 4, ответственного за формирование импульса генерации. На каждый период синхроимпульсов происходит запись информации в ДИМ 101. .

Свободный буферный регистр 86 записи выставляет сигнал запроса данньк, который поступает третий вход регистра 15 состояниям записы- вается в него. Процессор опрашивает регистр 15 состояния посредством команды чтения регистра состояния. Эта команда декодируется первым дешифратором 6, который формирует соот- ветствующий сигнал на своем девятом 36 выходе. Слово состояния вьщается на информационные входы-выходы 17 устройства. Если процессор получает указание, что буферный регистр 86 записи свободен, он выполняет передачу следующего информационного слова из ОЗУ ЭВМ в устройство. Цикл работы устройства по записи информа160, 10

ционного слова в ДИМ 101 повторяется заданное число раз с

После того как все слова информационного блока (страницьО переданы из ОЗУ в устройство и записаны в ДРМ 101, т.е. цикл работы устройства по записи информационного блок завершен, с последнего выхода (п+1) блока 79 оперативной памяти считывается бит конца цикла, который поступает на счетный вход счетчика 3 страниц и уменьшает на единицу его содержимое.

Одновременно этот сигнал поступает через элемент И 96 на третий вхо (сброса) счетчика 78 адресов и сбрасывает его в нуль. Цикл работы устройства по записи информационного блока повторяется.

Если вьшолнена запись заданного числа страниц и счетчик 3 страниц обнулился, на его выходе 49 вьфаба- тывается сигнал останова, котгрьй проходит через элемент ИЛИ 82 и сбрасьтает триггер 84. На D-вход триггера 95 поступает сигнал низкого уровня, следукяцим синхроимпульсом f он сбрасьюается и сбрасьгеает триггер 94. В результате прекращается подача синхроимпульсов f от генератора 1 тактовых импульсов.

Флаг завершения операции записи (низкий уровень на прямом выходе триггера 84) заносится в регистр 15 состояния и воспринимается процессором. На этом работа устройства в режиме записи заканчивает ся.

В режиме чтения устройство работает следующим образом.

Процессор выставляет на адресные входы 18 устройства команду чтения данных, а на вход 19 режима чтения - соответств пощий управляющий сигнал. Первьш дешифратор 6 декодирует команду и формирует на втором 29 вьиоде управляющий сигнал, устанавливающий в единичное состояние триггер 85. Этот управляющий сигнал устанавливает также в единичное состояние гер 94 и разрешает прохождение син-. хроимпульсов f, о Таким же образом, как и в режиме записи из блока 76 оперативной памяти считьгоается фазовая диаграмма, а из блока 79 оперативной памяти - временная диаграмма. Фазовая и временная диаграмма поступают на вторую группу логических элементов И 5, на выходе которой форми

руются сигналы управления блоком 101 формирователей функциональных сигналов, происходит также включение блока 103 формирователей вращающегося поля и начинается работа ДИМ 101.

Информация с ДИМ 101 поступает на блок 102 усилителей считывания и с его вькода - на первьш вход триггера 88 (сброс производится синхроимпульсом f J, поступающим на R-вкод) Каждьй такт бит информации поступает с выхода триггера 88 на второй вход (последйвательньй) регистра 89 сдвига.

Передача бита данных из ,ЦИМ 101 сопровождается вьщачей из блока 79 оперативной памяти сигнала, ответственного за формирование строб-импульса. Этот сигнал передается с выхода регистра 80 на элемент ИЛИ-НЕ 8 и с его выхода - на первый вход элемента ШШ-НЕ 81, разрешая прохождение синхроимпульсов на третий вход регистра 89 сдвига. Регистр 89 сдвиг вьшолняет последовательно-параллельное преобразование информации.

После заполнения регистра 89 сдвига -по сигналу с выхода счетчика 2 тактов, поступающему на четвертый вход буферного регистра 87 чтения, происходит передача в него информационного слова, принятого из Д5-М 101 Загруженньй буферный регистр 87 чтения выставляет сигнал наличия данных которь1й поступает на вход регистра 15 состояния и записывается в него,

Если процессор, опрашиваюй1ий регистр 15 состояния, получает указа

нне, что буферньй регистр 87 чтения заполнен, он выполняет передачу информационного слова в ОЗУ ЭВМ. Цикл повторяется до передачи всего информационного блока из ДИМ 101 в ОЗУ.

После чтения первого информационного блока бит конца цикла считывания из блока 79 оперативной памяти и умеАьшает на единицу содержимое счетчика 3 страниц. Аналогично выполняется цикл чтения второго информационного блока. Если операция чтения заданного числа страниц выполнена и счетчик 3 страниц обнулился, сигнал останова, формируемый на его выходе, проходит через элемент ИЛИ 8 и сбрасьшает триггер 85. Флаг завершения операции (низкий уровень на прямом выходе триггера 85) заносится н регистр 15 состояния и воспринима

ках.

ется процессором. На этом работа устройства в режиме чтения заканчивается Устройство позволяет выполнять останов - включение управляющего магнитного поля (старт-стоп) посл« произвольного числа тактов. Чтобы выполнить останов после первого такта, необходимо бит конца цикла (см. фиг.11) занести в первый адрес блока 79 оперативной памяти и единицу в счетчик 3 страниц, чтобы вьшолнить останов после второго такта, бит конца цшспа соответственно заносится во второй адрес блока 79 оперативной

памяти и т.д. I

Процессор анализирует считанную

информационную последовательность путем сравнения с той, которая бьша записана. Сведения о результатах испытаний (карта дефектов) может выводиться на дисплей, печатающее устройство или заноситься в банк данных в накопитель на магнитньк днеках.

Форм, ула.изобретения

Устройство для контроля домерпюй памяти, содержащее генератор тактовых импульсов, счетчик тактов, счет чик страниц и первую группу элементов И, выходы которой являются управляющими выходами первой группь устройства, отличающееся тем, что, с целью расширения области применения за счет возможности изменения параметров сигналов устройства и повьшения достоверности испытаний на надежность, доменной памяти, в него введены первый, второй и третий дешифраторы, блок формирования фазовых привязок, блок формирования временной диаграммы, блок формирования данных., мульт1-шлексор., регистр состояния, блок регистров, блок программируемых источников питания, вторую группу элементов И, выходы которой являются управляющими выходами

второй группы устройства, выходы программируемых источников питания являются управляющими выходами третьей группы устройства, информационные входы первого и третьего дешифраторов объединены и являются адресными входами устройства, первый управляющий вход первого дешифратора является входом записи устройства и соединен с первым управляющим входом

третьего дешифратора, второй управляющий вход первого дешифратора является входом чтения устройства, третий управляющий вход первого дешифратора является первым.входом синхронизации устройства, первый выход первого дешифратора подключен к первому входу блока формирования данных, второй вход которого соедшшн с вторым выходом первого дешифратора, третий выход которого подключен к входу синхронизации счетчика страниц, информационные входы которого соединены с информационными входами блока регистров, из1формационньв-1и входами блока формирования фазовых привязок, информационными входами блока форми- .рования временной диаграммы, инфорвторым управляющим входом первой группы элементов И, пятый выход пер вого дешифратора соединен с первым с входом блока формирования фазовых привязок, второй вход которого подключен к выходу генератора тактовых импульсов, шестой выход первого дешифратора соединен с третьим входом

10 блока формирования фазовых привязок седьмой и восьмой выходы первого дешифратора подключены соответствен но к первому и второму входам блока формирования временной диаграммы,

15 третий вход которого соединен с вхо дом начальной установки блока регистров, четвертым входом блока фор мирования фазовых привязок, третьим входом блока формирования данных.

мационными выходами группы блока фор- 2о входом установки в исходное состовторым управляющим входом первой группы элементов И, пятый выход первого дешифратора соединен с первым входом блока формирования фазовых привязок, второй вход которого подключен к выходу генератора тактовых импульсов, шестой выход первого дешифратора соединен с третьим входом

блока формирования фазовых привязок, седьмой и восьмой выходы первого дешифратора подключены соответственно к первому и второму входам блока формирования временной диаграммы,

третий вход которого соединен с входом начальной установки блока регистров, четвертым входом блока формирования фазовых привязок, третьим входом блока формирования данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Программируемый формирователь многочастотного сигнала | 1989 |

|

SU1739472A1 |

| Устройство для контроля за ходом вычислительного процесса | 1987 |

|

SU1539780A1 |

| Многоканальное буферное запоминающее устройство | 1980 |

|

SU903971A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Процессор с микропрограммным управлением | 1990 |

|

SU1700564A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля и испытаний на надежность запоминающих устройств на цилиндрических магнитных доменах. Цель изобретения - расширение области применения за счет возможности изменения параметров сигналов устройства и повышение достоверности испытаний на надежность доменной памяти. Устройство содержит генератор 1 тактовых импульсов, счетчик 2 тактов, счетчик 3 страниц, первую 4 и вторую 5 группы элементов И, первый 6, второй 7 и третий 8 дешифраторы, блок 9 формирования фазовых привязок, блок 10 формирования временной диаграммы, блок 11 формирования данных, блок 12 регистров, блок 13 программируемых источников питания, мультиплексор 14 и регистр 15 состояния. 11 ил.

мирования данных, выходам регистра состояния и являютая информационными входами-выходами устройства, первый второй, третий и четвертый выходы блока формирования данных соединены с соответствующими информационными входами регистра состояния, четвертый выход первого дешифратора соединен с первым входом генератора так- товьк импульсов, второй вход которого является входом начальной установки устройства, третий вход генератора тактовых импульсов соединен с шестым выходом первого дешифратора, пятый вькод блока формирования данных соединен с первым управляющим входом второго дешифратора, второй управляющий вход которого является вторым входом синхронизации устройства, первый и второй выходы блока формирования фазовых привязок соединены соответственно с первым и вторым информационньми входами второго дешифратора, информационные выходы первой и второй групп блока формирования фазовых привязок соединены соответственно с информационными входами первой и второй групп элементов И, информационные входы второй группы которых соединены cooTf ветственно с информационными выходами первой и второй групп блока формирования временной диаграммы, пер- вьй управляющий вход первой группы элементов И и управляющий вход второй группы элементов И соединены соответственно с первым и вторым выходами блока формирования данных, шестой выход которого соединен с

яние устройства, четвертый вход блока формирования данных соединен с первым входом счетчика тактов и подключен к шине нулевого потенциала,

девятый выход первого дешифратора соединен с пятым информационным входом регистра состояния, выходы второго дешифратора соединены с соответствующими информационными входами

-1ультиш1ексора и являются управляющими выходами четвертой группы устройства, первьй и второй управляющие входы мультип юксора яг ляются соответственно первым и вторым входами

задания рабочей частоты устройства, выход мультиплексора соединен с четвертым входом блока формирования временной диаграммы, пятым входом блока формирования данных и входом синхронизации счетчика тактов, второй управляющий вход третьего дешифратора является третьим входом синхронизации устройства, выходы третьего дешифратора соединены с входами синхро

низации блока регистров, выходы которого подключены к входам блока программмируемых источников питания, пятый вход блока формирования временной диаграммы подключен к седьмому выходу блока формирования данных, шестой и седьмой входы кото рого соединены соответственно с первым и вторым выходами блока формирования временной диаграммы, второй выход которого соединен с входом начальной установки счетчика страниц, вы- , ход переполнения которого соединен с восьмым входом блока формирования данных, девятый вход которого соеди

150116016

нен с выходом переполнения счетчи- - ка формирования является входом счи- ка.тактов, информаодюнный вход бло- { анных данных устройства.

63

§5

Генерация

4f

Вбод

страницы

Выёод

страницы ОЗнен

Фиг.З

4

67

Ъ

бб

Фиг. 2

8

иепение

-

при репликации

BbiSod --

при репликации

CmpoS

S9

считшбанцй

ФагЛ

$f

.17

Z2J97

(риэ.7

IF}SO-

ф1/г. 8

fi/

1 6 5 4 3 2 J a

. EmBeS eyuiiw8gm

Bti8o3 npa рвпяикаиаа

Seastttts при региикацт

Фиг. 10

7 6 S 4 S 2 f О

Коней цикла

/

tf TI I Генерация

СтроВ с тыбания

Вы Sod при репликации

Деление при репликаиии

Фиг. 11

Составитель Ю. Сычев Редактор М.Недолуженко Техред-л.Олийньж Корректоры. Басильев.а

Заказ 4878/50

Тираж 558

ВНИШШ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

/ / / Геиеродая Зыбод страница

BSod страницы

OSnsH

Вь(8од стрйницы

BSod страницы

Одпвн

Подписное

| Устройство для контроля доменной памяти | 1982 |

|

SU1022216A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков доменной памяти | 1982 |

|

SU1020862A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-08-15—Публикация

1988-02-22—Подача