1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при реализации технических средств ЭЦВМ.

Известно устройство для определения наибольшего и наименьшего из я чисел и их максимальной разности, содержащее регистры, в которых хранятся числа, схемы «ИЛИ, счетчик максимальной разности, счетчик наибольшего числа и счетчик наименьшего числа.

Однако известное устройство требует большого количества оборудования.

Предложенное устройство отличается тем, что оно содержит синхронный переключатель, каждый из двух выходов которого связан со входом управления соответствующего реверсивного счетчика, выходы обоих реверсивных счетчиков поразрядно подключены ко входам сумматора, выходы которого подключены к выходам устройства.

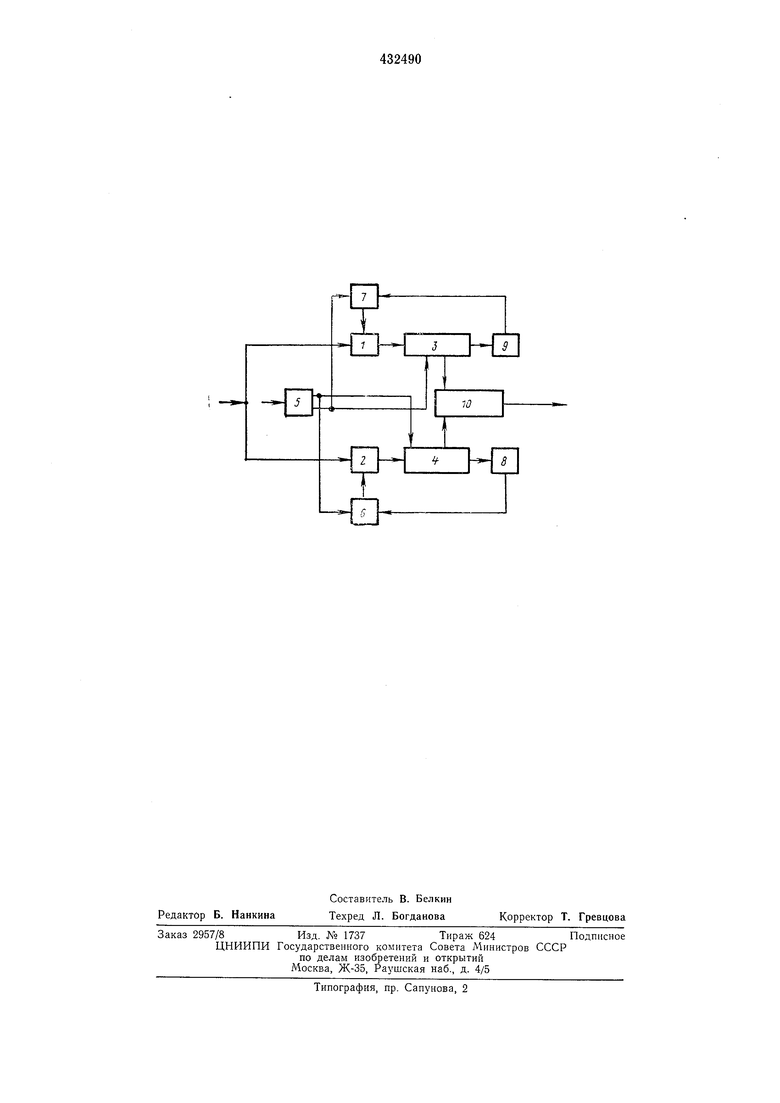

На чертеже приведена структурная схема устройства.

Устройство содержит схемы «И 1, 2, реверсивные счетчики 3, 4, синхронный переключатель 5, схемы «ИЛИ б, 7, 8, 9; сумматор 10.

Устройство работает следующим образом.

Числа ряда, каждое из которых представлено серией импульсов, последовательно одно за другим подаются через схемы «И 1, 2 на входы реверсивных счетчиков 3 4. Синхронный переключатель 5, каждый из двух выходов которого связан со входом управления соответствующего реверсивного счетчика и входом схем «ИЛИ 6, 7, обеспечивает попеременное переключение счетчиков в режимы «сложения и «вычитания и, вместе с тем, обеспечивает попеременную блокировку счетчиков 3, 4 путем подачи соответствующего сигнала на схемы «И 1, 2 через схемы

«ИЛИ 6, 7.

В начале анализа ряда чисел первое число, представленное серией импульсов, подается, например, через двухвходовую схему «И 1 на вход счетчика 3, который синхронны.м переключателем 5 переводится в режим суммирования. На выходе схемы «И 1 будет серия импульсов, которыми представлено число, в течение времени пока на втором входе схе.мы «И 1 присутствует сигнал с выхода синхронного переключателя 5, поданный на схему «И 1 через схему «ИЛИ 7. Счетчик 4 в это время синхронным переключателем 5 переводится в режим «вычитания. Однако, счетчик 4 в это время не работает, так как нет импульсов

на выходе схемы «И 2.

Отсутствие импульсов на выходе схемы «И 2, которые по входной щине подаются на один из ее входов, обеспечено отсутствием сигнала на другом входе схемы «И 2 через

схему «ИЛИ 6. На входы 6 не поступает сигнал с выхода синхронного переключателя 5 или сигнал с выхода схемы «ИЛИ 8, входы которой соединены с выходами реверсивного счетчика 4. В следуюш,ем такте счетчик 4 переводится в режим «суммирования, а счетчик 3 - в режим «вычитания. При этом на одном из входов схемы «И 1 нрнсутствует снгнал с выхода схемы «ИЛИ 7, ноданный по непи: выходы реверсивного счетчика 3 - схема «ИЛИ 9 - схема «ИЛИ 7; по входной шине, которая служит в качестве второго входа схемы «И 1, подается серия импульсов, представляющая число, на выходе схемы «И 1 будет серия импульсов; на одном из входов схемы «И 2 присутствует сигнал с выхода синхронного переключателя 5, поданный через схему «ИЛИ 6. но входной шине подаются импульсы, представляюш,не число, на вход счетчика 4 поступает серия импульсов.

В счетчике 4 будет производиться запись, а в счетчике 3 - вычитание очередного числа. Если вычитаемое число больше нли равно ранее занисанному в счетчике 3 числу, то счетчик 3 переходит в нулевое состояние, при этом сигнал на выходе схемы «И 1 отсутствует, так как исчезает снгнал с выхода схемы «ИЛИ 9, входы которой подключены к выходам реверсивного счетчика 3. Если вычитаемое число меньше ранее записанного в счетчике 3 числа, то в нем по окончании вычнтания остается остаток, в результате чего на одном нз входов схемы «И 1 будет присутствовать сигнал, ноданный но цепи; выходы реверсивного счетчика 3 - схема «ИЛИ 9 - схема «Р1ЛИ 7, подготавливая тем самым счетчик 3 к записи очередного числа. При поступлении очередного числа, представленного серией импульсов, на вход счетчика 3 через схему «И 1, происходит его суммирование с остатком.

По окончании анализа всего ряда чисел дается разрешение на сброс чисел, записанных в реверсивных счетчиках 3, 4, выходы которых норазрядно нодключены ко входам сумматора 10, и максимальное число из нредставленного ряда чисел определяется в сумматоре 10 как сумма двух чисел, содержашихся в счетчиках 3, 4.

Работа устройства поясняется примером.

Пусть имеется ряд десятичных чисел, представленных числом нмпульсов: 100, 120, 150, 150, 180, 235, 235, 166, 152. Данный ряд нредставляет собой конечный замкнутый интервал значений функций, имеюшей на этом интервале один ник (максимум).

Максимальное число ряда 235.

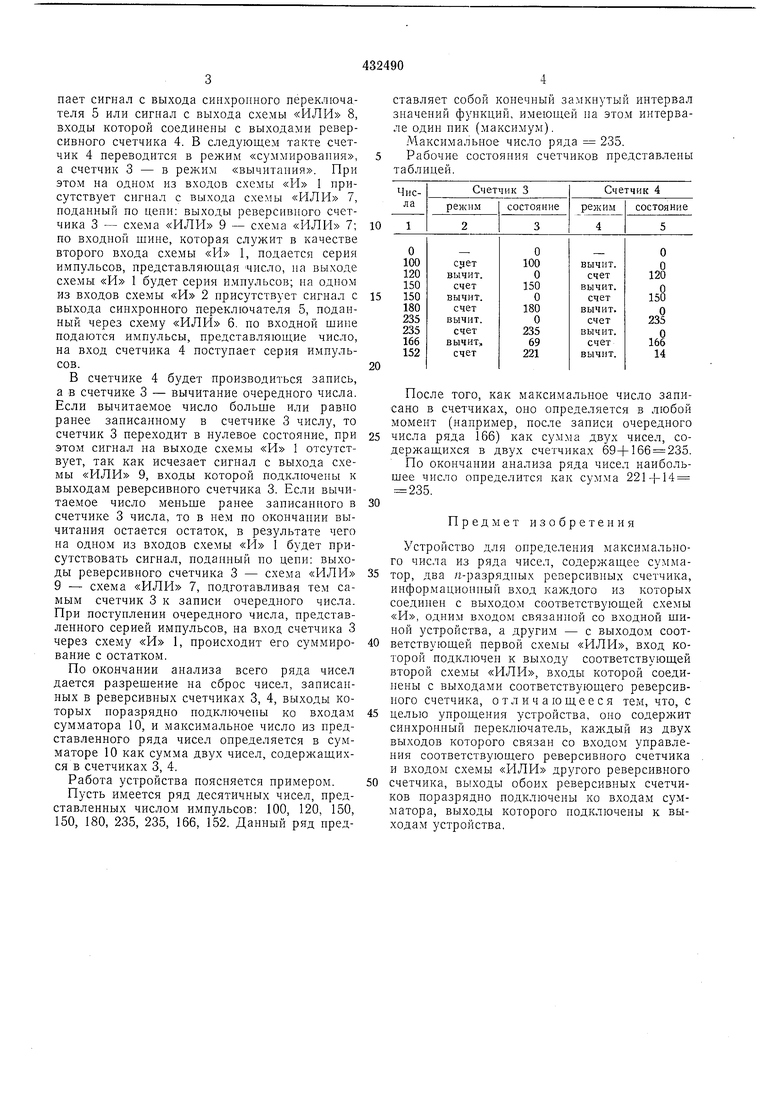

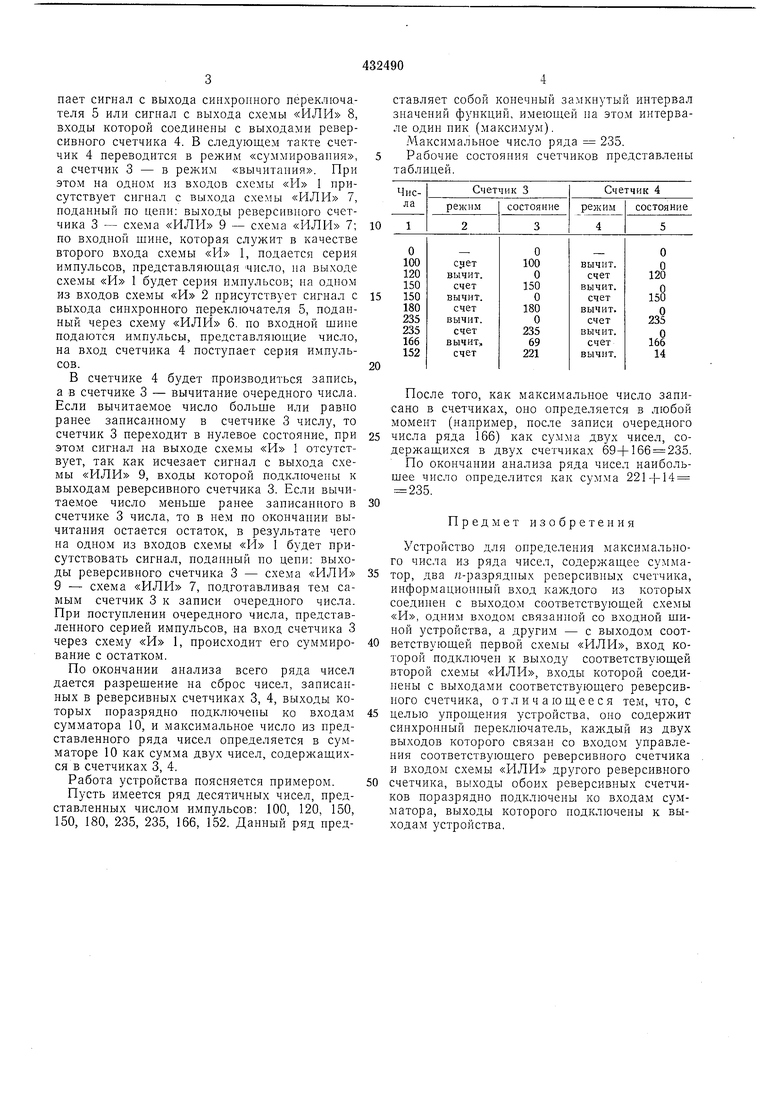

Рабочие состояния счетчиков представлены таблицей.

После того, как максимальное число занисано в счетчиках, оно определяется в любой

момент (например, после записи очередного

числа ряда 166) как сумма двух чисел, содержаш,ихся в двух счетчиках 69+166 235.

По окончании анализа ряда чисел наибольшее число определится как сумма 221-|-14 235.

Предмет изобретення

Устройство для онределения максимального числа из ряда чисел, содержаш,ее сумматор, два п-разрядных реверсивных счетчнка, информационный вход каждого из которых соединен с выходом соответствуюндей схемы «И, одним входом связанной со входной шиной устройства, а другим - с выходом соответствуЕОщей первой схемы «ИЛИ, вход которой подключен к выходу соответствующей второй схемы «ИЛИ, входы которой соединены с выходами соответствующего реверсивного счетчика, отличающееся тем, что, с

целью упрощения устройства, оно содержит синхронный переключатель, каждый из двух выходов которого связан со входом управления соответствующего реверсивного счетчика и входом схемы «ИЛИ другого реверсивного

счетчнка, выходы обоих реверсивных счетчиков поразрядно нодключены ко входам сумматора, выходы которого нодключены к выходам устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ ДЛИТЕЛЬНОСТИ ЭЛЕМЕНТАРНОЙ ПОСЫЛКИ ТЕЛЕГРАФНЫХ СООБЩЕНИЙ С РАЗЛИЧНЫМИ СКОРОСТЯМИ ТЕЛЕГРАФИРОВАНИЯ | 1973 |

|

SU383218A1 |

| Устройство для определения максимального числа из ряда чисел | 1978 |

|

SU725072A1 |

| УСТРОЙСТВО для ВЫЧИСЛЕНИЯ линий'РЕГРЕССИИ | 1971 |

|

SU290282A1 |

| ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU404083A1 |

| УСТРОЙСТВО для ДЕЛЕНИЯ ИМПУЛЬСНОГО СИГНАЛА НА ЧАСТОТУ ИМПУЛЬСОВ | 1970 |

|

SU265577A1 |

| Вычислительное устройство | 1972 |

|

SU439803A1 |

| УСТРОЙСТВО для ЦИФРОВОГО РЕГУЛИРОВАНИЯ СКОРОСТИ | 1973 |

|

SU374580A1 |

| СЧЕТЧИК С ПРЕДУСТАНОВКОЙ | 1970 |

|

SU269207A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| КОРРЕЛЯТОР | 1972 |

|

SU432510A1 |

Авторы

Даты

1974-06-15—Публикация

1972-06-27—Подача