г(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЖСЙМдЛЬЙОГО

.- I

ЧИСЛА ИЗ РЯДА ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для упорядочивания чисел | 1981 |

|

SU1012239A1 |

| Устройство для определения максимального числа из ряда чисел | 1980 |

|

SU928341A1 |

| Устройство для определения максимального числа из ряда чисел | 1981 |

|

SU1003072A2 |

| Устройство для определенияМАКСиМАльНОгО чиСлА из РядА чиСЕл | 1979 |

|

SU800990A1 |

| Устройство для упорядочивания чисел | 1980 |

|

SU932487A1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ ДЛИТЕЛЬНОСТИ ЭЛЕМЕНТАРНОЙ ПОСЫЛКИ ТЕЛЕГРАФНЫХ СООБЩЕНИЙ С РАЗЛИЧНЫМИ СКОРОСТЯМИ ТЕЛЕГРАФИРОВАНИЯ | 1973 |

|

SU383218A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МАКСИМАЛЬНОГО ЧИСЛА ИЗ РЯДА ЧИСЕЛ | 1972 |

|

SU432490A1 |

| Устройство для упорядочивания чисел | 1983 |

|

SU1144103A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для сравнения чисел | 1974 |

|

SU521566A1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано при обработке информации.

По основному авт. св. 432490 известно устройство для определения максимального числа из ряда чисел содержащее сумматор, два «1-разрядных реверсивных счетчика, информационный вход каждого из которых соединен с выходом соответствующей схемы И, одним входом связанной со входной йиной устройства, а ДРУгим - с выходом соответствующей первой схемы И.ЛИ, вход которой подключен к выходу сортветст ующей второй схемы ИЛИ, входа| которой соединены с выходами соответствующего реверсивного счетчика, а также синхронный переключатель, каждый из двух выходов которого связан со входом управления соответствующего реверсивного счетчика и входом схемы ИЛИ другого реверсивного счетчика, выходы обоих реверсивных счетчиков поразрядно подключены ко входам сумматора, выходы которого подключены к выходам устройства. Это устройство . позволяет в течение анализа ряда .последовательно поступающих нэгвМод

чисел и по его окончании получать на выходе максимально е число из поступивших от на ала7аналйз а 11 .

Однако с помощью известного устройства невозможно определить какое по счету число от нач-ала анализа является максимальным, что бывает . необходимо, например/ .при оценке уровня сигнала в параллельных кана0лах связи на различных частотах или при автоматической коммутаций антенн для определения направления на источник излучения.

Целью изобретения является расширение функциональных возможностей устройства путем определения номера максимального числа в последовательности чисел.

Поставленная цель достигается

0 тем, что в устройство введены третья и четвертая схемы И, третий счетчик, формирователь импульсов, узел перезаписи информации, узел памяти, причем выходы синхронного переключателя

5 основного устройства соединены со входом формирователя,, первый выход которого подключён к первому входу третьей схемы И, второй вход которой срединен с выходом четвертой схемы 0 и, входы которой подключены к выходам первой и второй схем ИЛИ основногоустройства, выход третьей схемы И соединен с управляющим входом узла перезаписи информации, инфбрйацйбйныёвходы которого подклйчены к вУходА 15ётьего счетчйка, информационный вход которого соединен со вторым выходом формирователя импульсов, выход узла перезаписи информации подключен ко входам узла памяти, установочные входы счетчика и узла памяти соединены с шиной начальной установки.

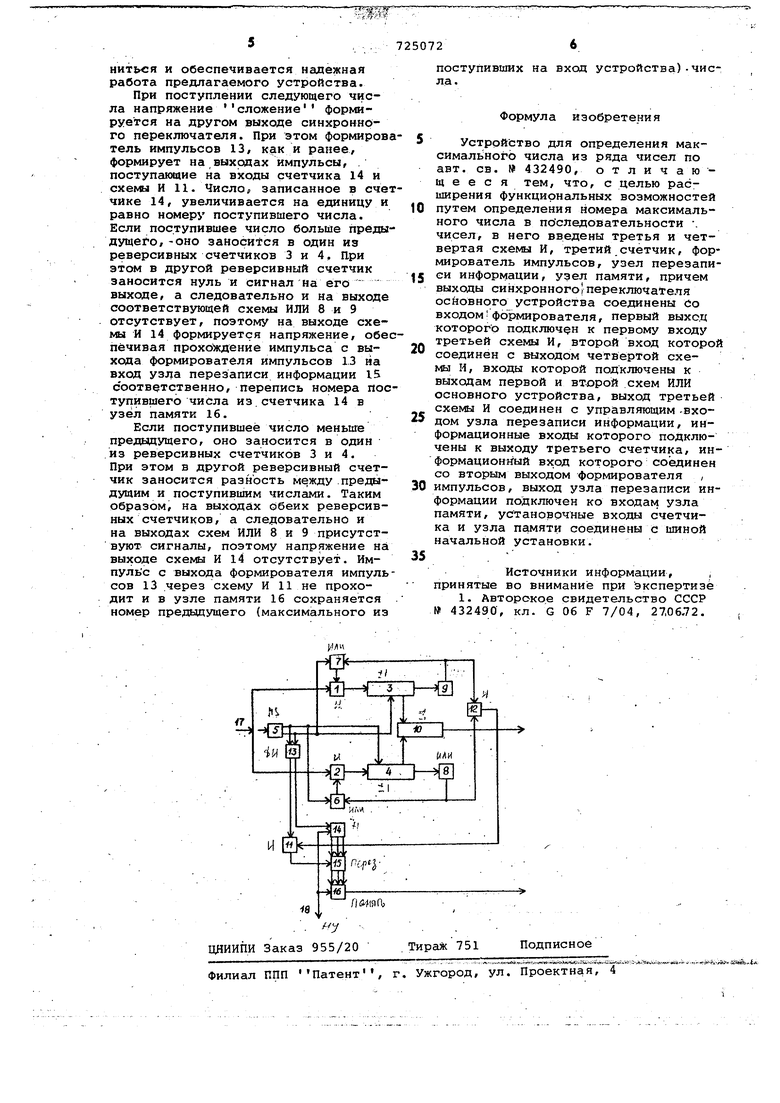

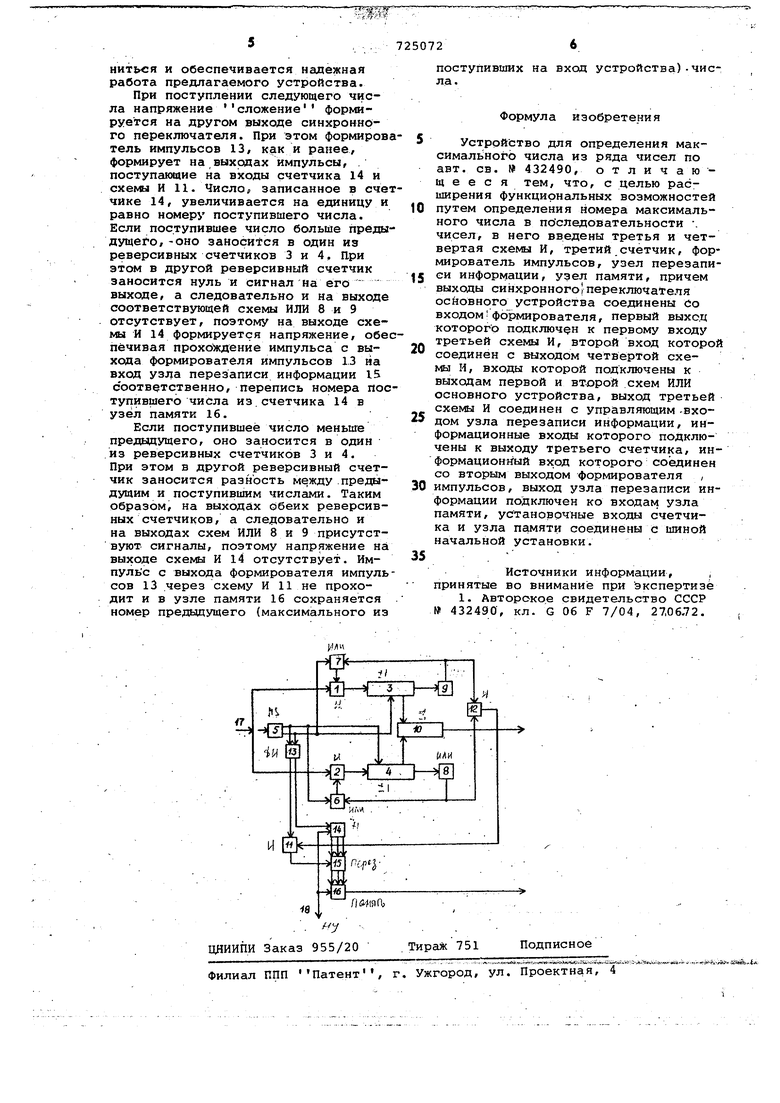

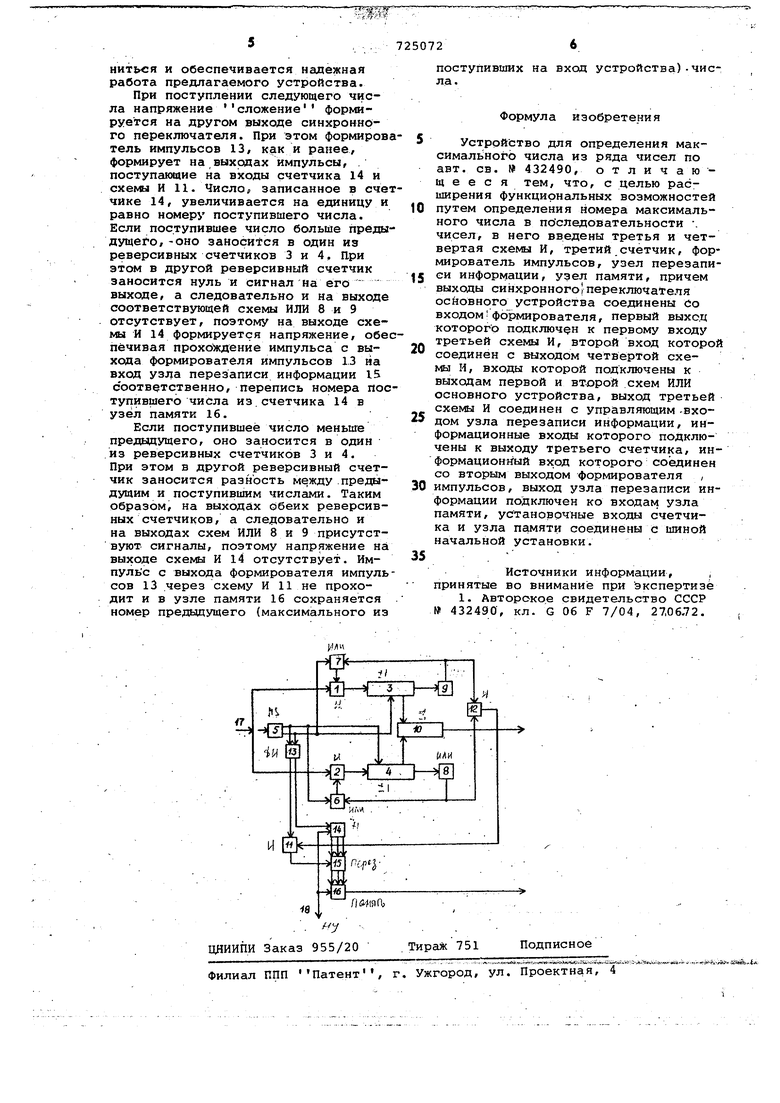

Блок-схема устройства представлена -на чертеже.

Устройство содержит схемы И 1 и 2, реверсивные счетчики 3 и 4, синхронный переключатель 5, схеки ИЛИ 6 - 9, cyiviMaTbp 10, схемы И 11 и 12, формирователь 13 йЯпуНЬсов, счетчик 14, узел 15 перезаписи информации, узел 16 памяти, входную шину 17, шину 18 начальной установки. , .

Устройство работает следующим образом.

В начале анализа ряда чисел первое число, представленное серией импульсов, подается, например, черей двухвхЬдовую схему И 1 на вход счетчика 3, который син: ронным переключателем 5 переводится в режим суммирования. На выходе схемы И l будет серия импульсов, которыми представле:1о число, в течение в земели, пока на втором входе схемы И 1 присутствуёт сигнал с выхода синхронного переключателя 5, поданный на схему И 1 через схему ИЛИ 7. Счетчик 4 синхронным переключателем 5 переводитсяв режим вычитания и в это время не работает, так как не импульсов на выходе схемы И 2.

Отсутствие импульсов на выходе схемы И 2, которые по входной шине подаются наодин из ее входов, обеспечено отсутствием сигнала HS другом входе схемы И 2 через схему ИЛИ б. На входы схемы б не поступает сигнал с выхода синхронного переключателя 5 или сигнал с выхода схемы Или 8, входы которой соеДИНёны с выходами реверсивного счетчика 4. В следующем такте счетчик 4 переводится в -режим суммирования, а счетчик 3 - в-режим вычитаний. При

этом на одном из входов схемы И

1 присутствует- ситнал с ёыхад а -схе- мы ИЛИ 7, -поданный по цепи: выхо-. ы реверсивного счет-чика. 3 - схема ИЛИ 9 - cxeMli ИЛИ 7. По входной шине, которая служит в качестве втоого входа схемы И 1, подается .сеий импульсов, представляющая число,

на выходе схемы И 1 будет серия мпульсов: на одном из входов схеы И 2 присутствует сигнал с выхоа синхронного переключателя 5, ; поданный через схему ИЛИ б; по входной 111ине подаются импульсы.

/ - . .

представляющие число; на вход счетчика 4 no&Tynaef серия импульсов.

В счетчике 4 производится запись а в счетчике 3 - вычитание очередного числа. Если вычитаемое ,число больше ИЛИ равноранёёзапйсан ному в счетчике 3 числу, то счетчик 3 переходит в нулевое состояние, при этом сигнал На выходе схемы И 1 отсутствует, так как исчезает сигнал с выхода схемы ИЛИ 9, йходы которой подключены к выходам реверсивного счётчика 3.Если вычитаемое число меньше ранее записанного в счетчике 3.числа, то в нем по окончании вычитания остается остаток, в результате чего на одном из входо схемы И 1 будет присутствовать сигнал j поданный по цепи: выходы реверсивного счетчика 3 - схема ИЛИ 9 - схема ИЛИ 7, подготавливая тем. самым счетчик . к записи очередного числа. При поступлении очередного числа, представленного серией импульсов, на вход счетчика 3 через схему И 1 происходит его суммирование с остатком.

До поступления на вход устройства анализируемых чисел в счетчике 14 и узле памяти 16 записан код, соответствующий нулю. При поступлении на вход устройства последователного ряда чисел синхронный переключатель 5 на обоих выходах формирует напряжения, переводящие реверсивные счетчики 3 и 4 попеременно в режимы сложение и вычитание. Данные напряжения поступают на вход формирователя импуЛьсов.13, который при появлении напряжения .сложение на любом из входов -формирует на каждом из выходов импульс.

Импульс, поступающий на вход счечика 14,изменяет его состояние на единицу . Импульс, поступающий на вход третьей схемы И 11, проходит на ее выход, толькоесли на другом ее входе, связанном с выходом схемы и 14, присутствует напряжение. Схема И .14 формирует на выходе напряжение в случаях отсутствия хотя бы на одном из входов сигнала (услоной единицы) с выходов схем ИЛИ 8 и.9, что соответствует нулевому состоянию хотя бы одного из реверсивных, счетчиков 3 и 4. При наличии напряжёния на-выходе схемы И 14 импульс с выхода формиробателя импульсов 13 проходит через схему И 11 на управляющий вход узла перезаписи информации 15, обеспечивая прохождение кода числа, записанного в счетч:ик 14, в узел памяти 16, Импул на формирователя импульсов 1 соединенном с входом .счетчика 14, несколько опережает импульс на другом выходе формирователя, .благодаря чему состояние счетчика 14 к моменту перезаписи успевает изме-

Авторы

Даты

1980-03-30—Публикация

1978-03-20—Подача