1

Изобретение относится к системам а1втоматического регулирования и может быть использовано в системах точной стабилизации скорости.

Известные цифровые интегральные регуляторы скорости, Содержащие сравнивающее устройство, устройство задания акорости, импульсный датчик скорости и устройство управления, ха,рактеризуются относительно Hieвыоокой скоростью при интегральном Законе регулироваиия и относительно узки.м диапазоном отклонений.

Цель изо.бретения - увеличение точности устройства и расширение динамического диапазона его работы.

Для этого предлагаемое устройство содержит схему блокировки, лервый вход которой соеди.нен1 с выходом импульсного датчика скорости, вторые входы - с выходами переполнения схемы сравнения, первый выход схемы блокировки связан с входом вычитания схемы сравнения, второй выход - с входом сложения схемы сравнения, а третьи выходы схемы блокир01вки подключены к входам блока задания скорости.

Для увеличения быстродействия устройства схема сравнения содержит интегратор, к счетному входу триггера мантиссы г-ого разряда которого через первую линию задержки присоединен выход первой схемы «ИЛИ,

первый вход которой 1соединен с выходом первой схемы совпадения (г-1)-ого разряда и с первым входом второй схемы совпадения, втОрой вход которой связан с первым выходом триггера мантиссы, а вьиход через вторую схему «ИЛИ соединен с первым входом первой схемы совпадения, второй вход которой соединен с шиной сложения, второй вход первой схемы «ИЛИ соединен с выходом

третьей схемы совпадения (г-1)-ого разряда и с первым входом третьей схемы совпадения, второй вход которой соединен со вторым выходОМ триггера мантиссы, первый выход которого соединен с первы-м входом четвертой схемы совпадения, второй вход которой соединен с входной: шиной г-ого разряда интегратора,, а выход четвертой схемы совпадения через вторую линию задержки и вторую схему «ИЛИ соединен с первым входом второй схемы совпадения.

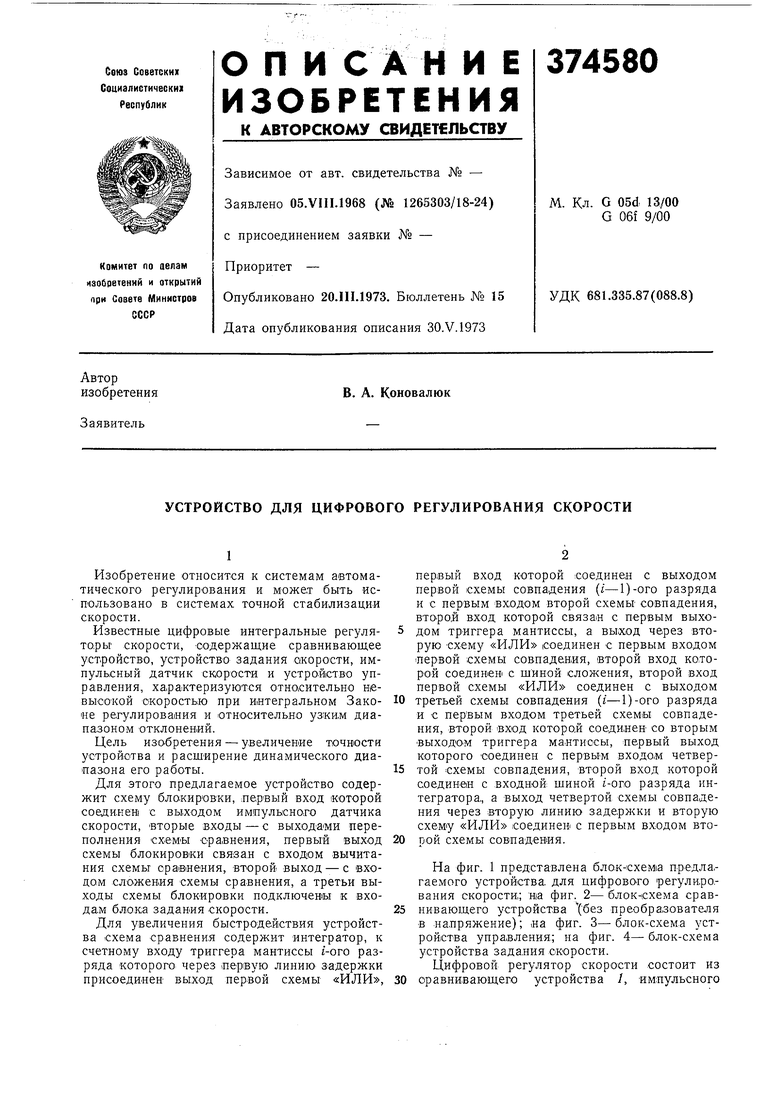

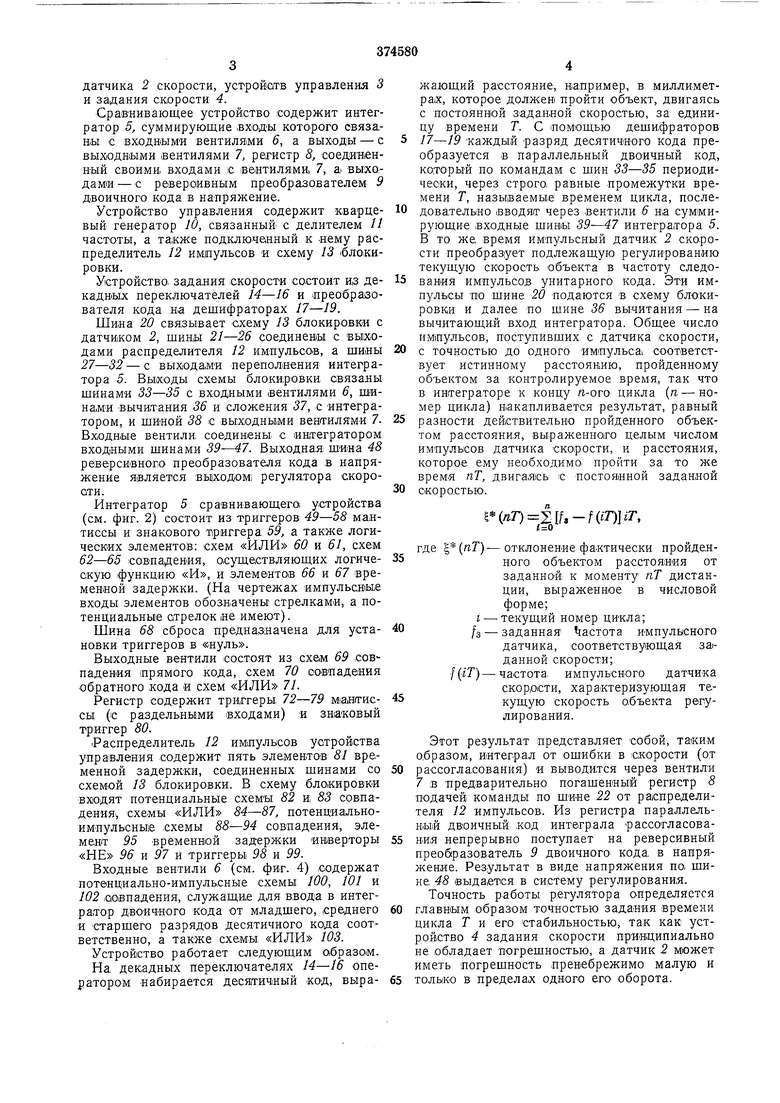

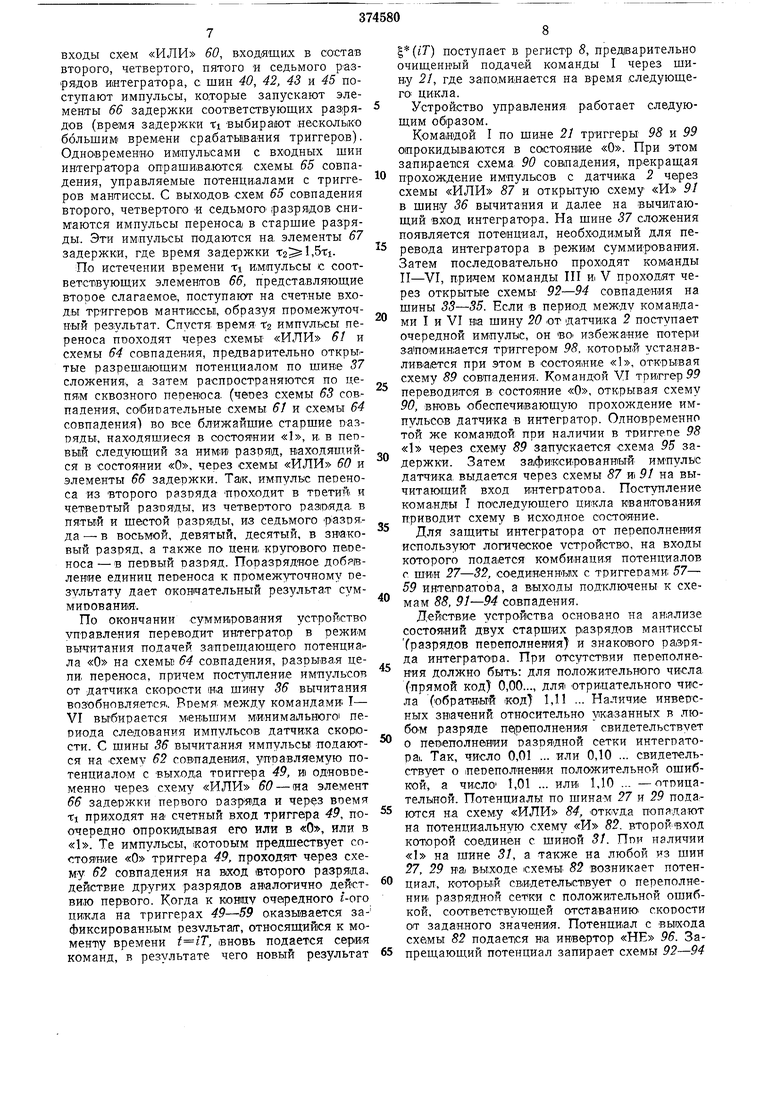

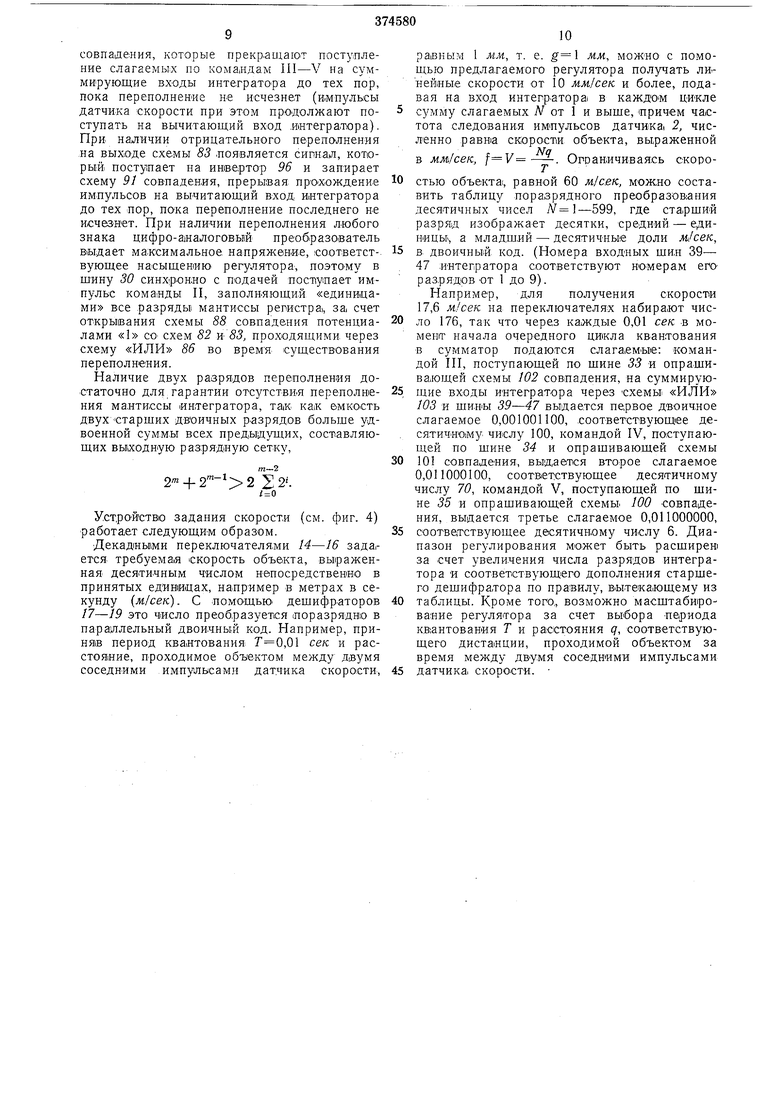

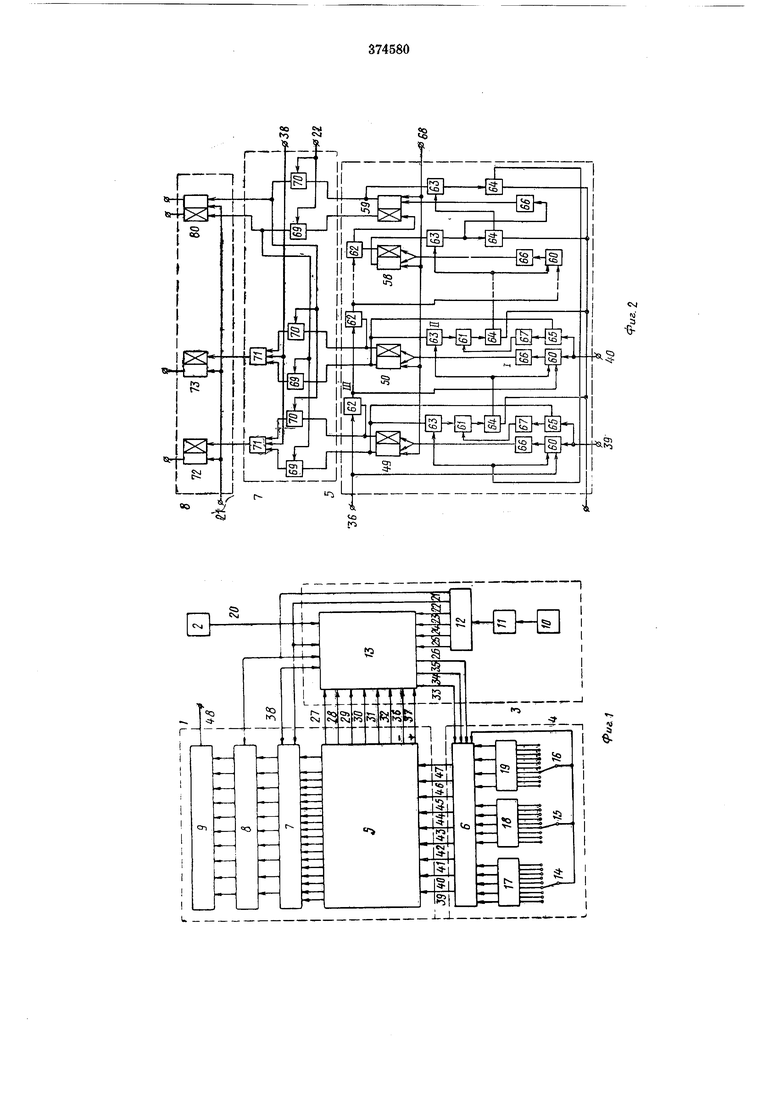

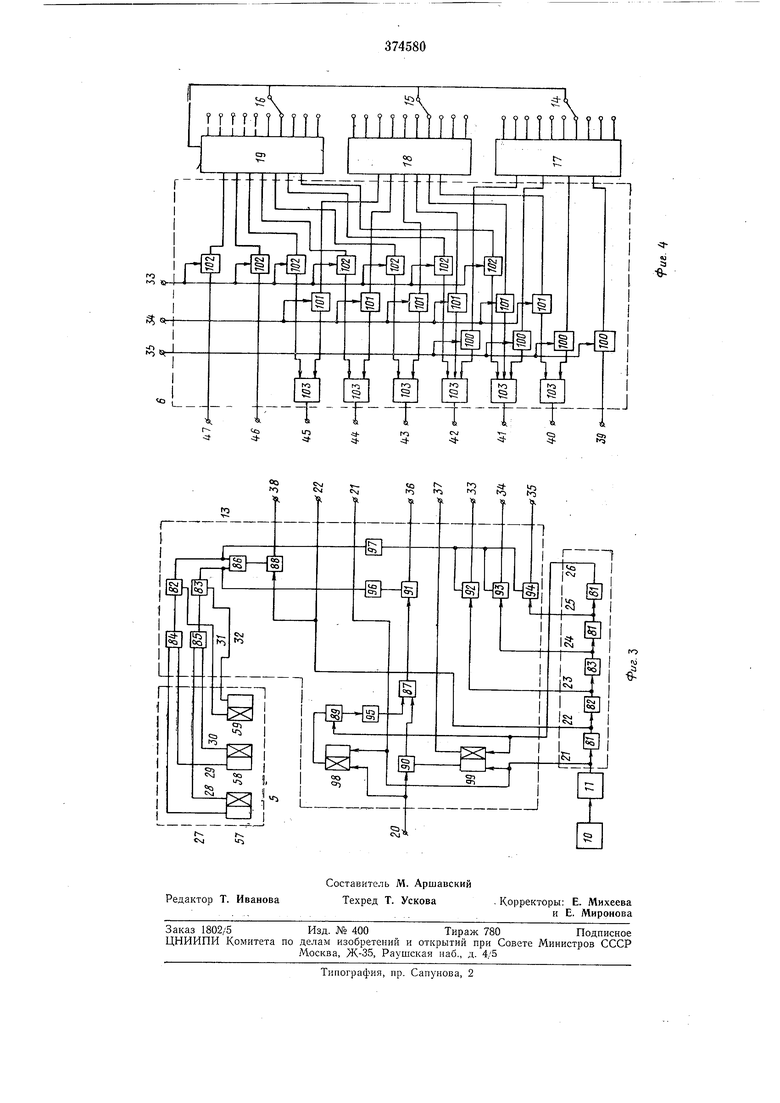

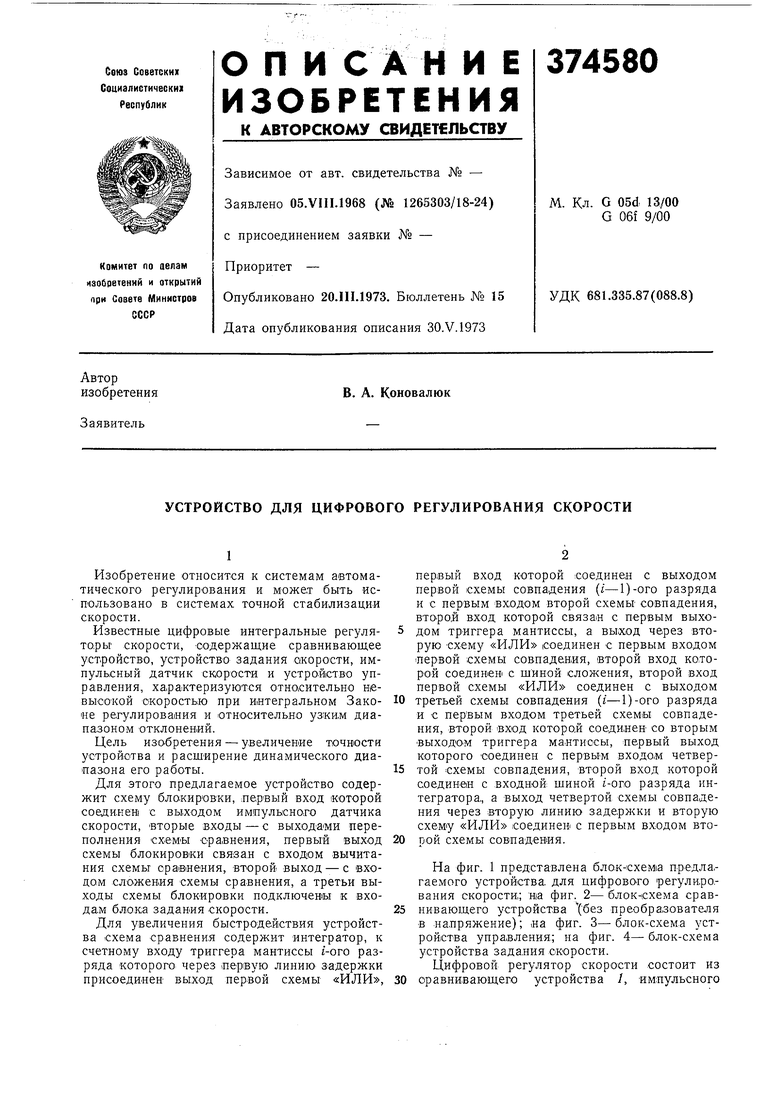

На фиг. 1 представлена блок-cxeMia предла,гаемого устройства для цифрового регулирования скорости,; Hia фиг. 2- блок-схема сравкивающего устройства без преобразователя в напряжение); на фиг. 3-блок-схема устройства управления.; на фиг. 4- блок-схема устройства задания скорости.

Цифровой регулятор скорости состоит из сравнивающего устройства /, импульсного датчика 2 скорости, устройств управления 3 и задания скорости 4. Сравнивающее устройство содержит интегратор 5, суммирующие .входЫ которого связа,Бы с входными вентилями 6, а выходы - с вых|ОДН1Ыми вентилями 7, регистр 8, соединенный своими входами ic вентилями, 7, ai выхог дамИ-с реверсивным преобразователем 9 двоичного кода в напряжение. Устройство управления содержит -кварцевый генератор 10, связанный с делителем 11 частоты, а также подключе|нный к нему распределитель 12 импульсов и схему 13 блокировки. Устройство, задания ско-рости состоит из декадных переключателей 14-16 и преобразователя кода на дешифраторах 17-19. Шина 20 связывает схему 13 блокировки с датчиком 2, щины 21-26 соединены с выходами распределителя 12 импульсов, а шины 27-32 - с выходами переполнения интегратора 5. Выходы схемы блокировки связаны шинамИ 33-35 с входными вентилями 6, шинами вычитания 36 и сложения 37, с интегратором, и шияой 38 с выходными вен1тилями 7. Входные вентили. соедин1ены с интегратором входными шинами . Выходная шина 48 реверсивного преобразователя кода в напряжение является ВЫХОДОМ регулятора скорости. Интегратор 5 сравнивающего устройства (см. фиг. 2) состоит из триггеров 49-58 мантиссы и знакового триггера 59, а также логическ1их элементов: схем «ИЛИ 60 и 61, схем 62-65 совпадения, осуществляющих логическую функцию «И, и элементов 66 и 67 временной задержки. (На чертежах импульсвые входы элементов обозначены стрелками, а потенциальные отрелО(К|Не имеют). Шина 68 сброса предназначена для установки триггеров в «нуль. Выходные вентили состоят из схе,м 69 сов падения прямого кода, схем 70 совпадения обратного кода и схем «ИЛИ 71. Регистр содержит триггеры 72-79 мйнтиссы (с раздельными входами) и зн1аковый триггер 80. Распределитель 12 импульсов устройства управления содержит пять элементов 81 вре.менной задержки, соединенных шинами со схемой 13 блокировки. В схему блокировки входят потенциальные схемы 82 и. 83 совпадения., схе.мы «ИЛИ 84-87, потенциальноимпульсньне схемы 88-94 совпадения,, элемент 95 временной задержки инверторы «НЕ 96 и 97 и триггеры 98 и 99. Входные вентили 6 (см. фиг. 4) содержат потенциально-импульсные схемы 100, 101 и 102 .совпадения, служащие для ввода в интегратор двоичного кода от младшего, среднего и старшего разрядов десятичного кода соответственно, а также схемы «ИЛИ 103. Устройство работает следующим абразом. На декадных переключателях 14-16 оператором набирается десятичный «од, вырал ающий расстояние, например, в миллиметpaix, которое должев пройти объект, двигаясь с постоянной Зада.нной скоростью, за единицу времени Т. С помощью дешифраторов 17-19 -каждый разряд десятичного кода преобразуется в параллельный двоичный код, который по командам с шин 33-35 периодически, через строго равные промежутки времени Г, называемые временем цикла, последовательно вводят через вентили 6 н,а суммирующие входные ШИВЫ 39-47 интегратора 5. В то же время импульсный датчик 2 скорости преобразует подлежащую регулированию текущую скорость объекта в частоту следования импульсов унитарного кода. Эти импульсы по шине 20 подаются в схему блокировки и далее по шине 36 вычитания - на вычитающий вход интегратора. Общее число импульсов, поступивших с датчика скорости, с точностью до одного импульса, соответствует истинному расстоянию, пройденному объектом за контролируемое время, так что в интегра.торе к концу п-ого цикла (п - номер цикла) Hfaкaпливaeтcя результат, равный разности действительно пройденного объектом расстояния, выраженно1го целым числом импульсов датчика скорости, и расстояния, которо.е ему нeoiбxoдимo пройти за то же врем.я пТ, двигаясь с постоянной заданной скоростью. (йГ)|{/.-/0-Г)гТ, где с,(пТ)-отклонение фактически пройденного объектом расстояния от заданной к моменту пТ дистанции, выраженное в числовой форме; I- текущий номер цикла; /3 - заданная lacTOTa импульсного датчика, соответствующая 3aiданной скорости; /(гТ)-частота импульсного датчика скорости, характеризующая текущую скорость о.бъекта регулирования. Этот результат представляет собой, таким .бразом, интеграл от ошибки в скорости (от ассогла.сования) и выводится через вентили в предварительно погашенный регистр 8 одачей команды по шине 22 от распределиеля 12 импульсов. Из регистра параллельый двоичный .код интеграла рассотласова.ия непрерывно поступает на реверсивный реобразователь 9 двоичного кода в напряение. Результат в виде напряжения по, шие 48 выда,ется в систему регулирования. Точность р.аботы регулятора определяется лавным образом точностью задания времени икла Г и его стабильностью, та.к как устойство 4 задания скорости принципиально е обладает погрешностью, а датчик 2 может меть погрешность пренебрежимо малую и олько в пределах одного его оборота. Устройство управления задает цикл работы регулятора и координирует действие различных его узлов. Время цикла задается стабильным кварцевым: генератором 10, частота которого уменьшается делителем частоты до необходимой величины .fo -. Имщульсы с делителя частоты периодически через время Т постуцают в распределитель 12 импульсов, причем каждый импульс с делителя 11 запускает серию команд, подаваемых с выходных шин 21-26 распределителя в соответствуюшие узлы регулятора. Последовательность и назначение команд в каждом цикле следуюш;ие:команда I (шина 21 - перевод интегратора из режима: вычитания в режим суммирования, сброс регистра в «нуль ; команда II (шина 22 - ввод в регистр двоичного кода результата из интегратора; кома-яда П1 (шина 23 -ввод в интегратор двоичного числа, соответствующего первому (старшему) разряду заданного десятичного кода; команда IV (шина 27 - ввод в интегратор двоичного числа, соответствующего второму разряду заданного десятичного кода,; команда V (шива 25 - ввод в интегратор двоичного числа, соответствующего третьему (младшему) разряду заданного десятичного кода; ко-манда VI (шина 26 - перевод интегратор;а из режима суммирования в режим вычитания. Входящая в состав устройства 3 управлеНИЛ схема 13 блокировки по .команде I прекращает поступление им-пульсов от датчика 2 через щину 36 вычитания на вычитающий вход интегратора 5; по щине 37 сложения выдает потенциал, переводящий интегратор в режим суммирования чисел входных ши.н S9-47, по шинам 33-35 выдает команды Ill, IV и V, а затем по команде VI вновь переводит интегратор в режим вычитания подачей нулевого потенциала через шину 57 сложения и восстанавливает прохождение импульсов от датчика 2 по ши.не 36 вьтитания. Если, за время между командами I и VI с датчика 2 поступает импульс, он запоминается и затем выдается в щину 36 вычитания с некото-тзой задержкой относительно команды VI. При переполнении выходной разрядной сетки интегратора с щин 27-32 в схему 13 поступает такая комбинация потенциалов, .при которой в щину 38 в момент прохождения команды П подается импульс, переводящий все триггеры мано-иссы регистра в 1состояние «1, что соответствует максимальному напряжению с выхода пр|еобразователя 9. На время существования переполнения в зависимости от его знака прекращается подача импульсов или по шине 36 вычитания (при скорости о.бъекта, больше заданной) или по щинам 33-55 (при скорости объекта, меньше задан.н.ой). Интегратор 5 (см. фиг. 2) представляет со- 6 бой комбинацию параллельного двоичного накапливающего сумматора со сквозным переносом и двоичного -вычитающего счетчика, та«же обеспечивающего сквозной перенос «единицы. Положительные числа в интеграторе представлены двоичным кодом с фиксированной запятой, отделяющей зн.аковы.й разряд от маитиссы, и сни,м.аются с незащтрияованных половин триггеров 49-59, а отрицательные числа - обратным кодом-, причем положительному числу соответствует «нуль в знаковом разряде, а отрицательному - «единица. Цикл начинается подачей команды I по щине 1, при этом триггеры 72-80 регистра устаиавливаются в «О, а интегратор переводится в режим суммирования. Одновременно прекращается подача импульсов датчика 2 на вычитающий вход интегратор а и подача разрешающего потенциала по шине 57 сложения, подготавливающей потенциально-импульсные схемы 64 совпадения к пропусканию импульсов. Сигнал команды II, поступающий по шине 22. в случае, если триггер знаj g интегратора 59 н.аходится в состоянии «О, проходит через схему 69 совпадения зна.кового разряда, входящую в состав схемы выходных вентилей S, и переводит знаковый триггер 80 в соответствующее состояние «О. Одповременно импульс со схемы 69 совпадения опрашивает все схемы 69, соединенные с выходами тоиггеров 49-56 манггиссы. Если триггер 59 находится в состоянии «1, то команда П поступает на схемы 70 совпаде„jjjj соединенные с выходами триггеров 49- 56 мантиссы., с тем, чтобы преобразовать о,братный код отридательного числа в прямой, так как для преобразователя двоичного, кода в напряжение необходимо, чтобы мантиссы отрицательных чисел были представлены прямым кодом. Та.ким образом, импульсы с выходов схем 69 или 70, проходя через схемы «ИЛИ 71 на входы триггеров 72-80 регистра 8 переносят число из интегратора в регистр. В сл Т1ае переполнения .выходной разрядной сетки интегр-атора .синхронно с командои П по щин1е 38 посылается импульс переполиения, поступающий параллельно через схемы 71 во все триггеры мантиссы регистра 8, переводя триггеры 72-79 в состоя-ние «1, что соответствует максимальному выходному напряжению преобразователя 9. Командами III, IV и V через входные шины 39-47 интегратора последовательно вводяггся параллельным кодом слагаемые, имеющие положительный знак, которые доб.авляются к числу, оста.вщем-уся в интеграторе от преды.дущего цикла вычислений, Работа интегратора в режиме суммировад .иллюстрируется На примере сложения двух чисел 1,1111001110 и 0,0001011010, перое из которых осталось в интеграторе от предыдущего цикла, а второе подается по шинам 39-47. В момент подачи второго слагаемого на

7 60,

входы схем «ИЛИ 6У, входящих в состав второго, четвертого, пятого и седьмого р азрядов интегратора, с шин 40, 42, 43 и 45 поступают импульсы, которые запускают элементы 66 задержки соответствующих разрядов (время задержки ti -выбирают несколько большим врем.ени срабатьЕва ния триггеров). Одновременно импульсами с входных шин интегратора опрашиваются, схемы, 65 совпадения, управляемые потенциалами с триггеров мантиссы. С выходов, .схем 65 совпадения второго, четверто.го И седьмого разрядов снимаются импульсы переноса в старшие разряды. Эти импульсы подаются на элементы 67 задержки, где время задержки ,5т1.

По истечении времени TI импульсы с соответствующих элементов 66, представляющие второе слагаемое, поступают на счетные входы триггеров манти|Ссы, образуя промежуточный результат. Спустя, время тг импульсы переноса пооходят через схемы «ИЛИ 61 и схемы 64 совпадения, предварительно открытые разрешающим потенциалом по шине 37 сложения, а затем распространяются по цепям сквозного переноса. (чеОез схемы 63 сов.падения, собисательные схемы 6 и схемы 64 совпадения) во все ближайшие старшие ОНЗряды, находящиеся в состоя-нии «Ь, и. в пепВЫ1Й следующий за ними разряд, ваходяцтийся в состоянии «О, через схемы «ИЛИ 60 и элементы 66 задержки. Так, импульс переноса из второго разряда проходит в третий и четвертый разряды, из четвертого раз1р1яда в пятый и тестой разряды, из седьмого р азряда -- в восьмой, девятый, десятый, в зн1аковый разряд, а также по цени, кругового переноса- в первый разряд. По.разряд ное доб 1влен1ие единиц переноса к промежуточному результату дает окончательный результат суммиоования.

По окончании .сумм рова-ния устройство управления переводит ин.теграто.р в режим вычитания подачей запрещающего потенциа ла «О на схемьс 64 со.впадения, разрыва.я цепи, переноса, причем поступление импульсов от датчика скорости та шипу 36 вычитания возобновляется,. Время между командами, I- VI выбирается Мвнъшим минимального периода следования импульсов датчика скорости. С щины S6 вычитания импульсы подакугся на схему 62 совпадени,я, управляемую потенциало.м с выхода триггера 49, VB одновременно через схему «ИЛИ 60 - яа элемент 66 задержки первого разряда и чер.ез время TI приходят на счетный вход триггера 49, поочередно опрокидывая его или в «О, или в «1. Те импульсы, КОТОРЫМ предшествует состояние «О триггера 49, проходят через схему 62 совпадения на вход второго разряда., действие других р азрядов авалотично действию первого. Когда к концу очередного г-ого ци;кла на триггерах 49-59 о.казы1вается зафиксированным результапг, относящийся к моменту времени , 1вновь подается серия команд, в результате чего новый результат

8

I (iT) поступает в регистр 8, предварительно очищенный подачей команды I через шину 21, где запоминается на время следующего, цикла.

Устройство управления р.аботает следующим образом.

Командой I по щине 21 триггеры 95 и 99 опрокидываются в састоявие «О. При этом запирается схема 90 совпадения, прекращая прохождение импульсов с датчика 2 через схемы «ИЛИ 87 и открытую схему «И 91 в шину 36 вычитания и далее на вычитающий вход интегратора. На щине 37 сложения появляется потенциал, необходимый для перево.да интегратора в режим суммирования. Затем последовательно проходят команды И-VI, причем команды П1 и V проходят через открытые схемы 92-94 совпадения на щины 33-55. Если в период между командами I и VI ва щину 20 от датчика 2 поступает очередной импульс, он во избежание потери заповдинается триггером 98, которьш усталавлив1а1ется при этом в состояние «Ь, открывая схему 89 совпадения. Командой VI триггер 99 переводится в состоя1ние «О, отк.рыва.я схему 90, вновь обеспечивающую прохождение импульсов датчика в интегратор. Одновременно той же коман1Дой при наличии в триггепе 98 «1 через схему 89 запускается схема 95 задержки. Затем зафиксированный импульс датчика, выдается через схемы 57 и: 91 на вычитаю1щий вход интегратора. Поступление кома.нды I последующего цикла квантования приводит схему в исходное состояние.

Для защиты интегратора от переполнения используют логическое устройство, на входы которого подается комби.наци.я потенциалов с щип 27-32, со.,еннЫ х с триггерами 57- 59 интегратора, а выходы подключены к схемам 88, 91-94 совпадения.

Действие устройства основано на анализе состоя,ний двух старщих разрядов мантиссы Тразрядов переполнения) и знакового разряда интегратора. При отсутствии переполнения должно быть: для положительного числа (прямой код) 0,00..., ДЛЯ1 отрицательного числа (обратный код) 1,11 ... На.личи1е инверсных зн1аче.ний относительно указанных в любом разряде пе(реполнени,я свидетельствует о переполнении разрядной сетки интегратора. Так, число 0,01 ... или 0,10 ... свидетельствует о переполпеви.и положительной ошибкой, а ЧИСЛО 1,01 ... ИЛИ1 1,10 ... -отрицательной. Потенциалы по шинам 27 и 29 подаются н.а схем.у «ИЛИ 84, откуда попя.я,ают на потенциальную схему «И 82. второйвход которой соединен с щиной 31. Ппи наличии «Ь на шине 31, а также на любой из шин 27, 29 гга выходе 1схем.ы. 82 возникает потенциа.л, который сви.детельствует о переполнении разрядной сетки с положительной ошибкой, соответствующ,ей отста.ванию. скорости от заданного значения. Потенциал с выкода схемы 82 подается ва инвертор «НЕ 96. Запрещающий потенциал запирает схемы 92-94

совпаделия, которые прекращают поступление слагаемых по комалдам III-V на суммирующие входы интегратора до тех пор, пока переполнение не исчезнет (импульсы датчика скорости при этом продолжают поступать на вычитающий вход .интегратора). При наличии отрицательного переполнения .на выходе схемы 83 .появляется силнал, который поступает на инвертор 96 и запирает схему 91 сов-падбЕия, прерывая прохождение импульсов на вычитающий вход интегратора до тех лор, пока переполнение последнего не исчезиет. При наличии переполнения любого знака цифро-аяалоговьвй преобразователь выдает максимальное, напряжение, соответст-. вующее насыщению регулятора, поэтому в Щину 30 синхронно с подачей nocTiynacT импульс команды II, заполняющий «единицами все разряды мантиссы регистра, за, счет открывания схемы 88 совпадения потенциалами «1 со схем 82 н 83, проходящими, через схему «ИЛИ 86 во время существования переполнения.

Наличие двух ра;3рядов переполнения достаточно для гарантии отсутствия переполнения ма.нтиссы интегратора, так как емкость двух старщих двоичных р.азрядов больще удвоенной сум.м.ы всех предыдущих, составляющих вы ходную разрядную сетку.

ш-2

l

2 112

1 0

Устройство задания скорости (см. фиг. 4) работает следующим образом.

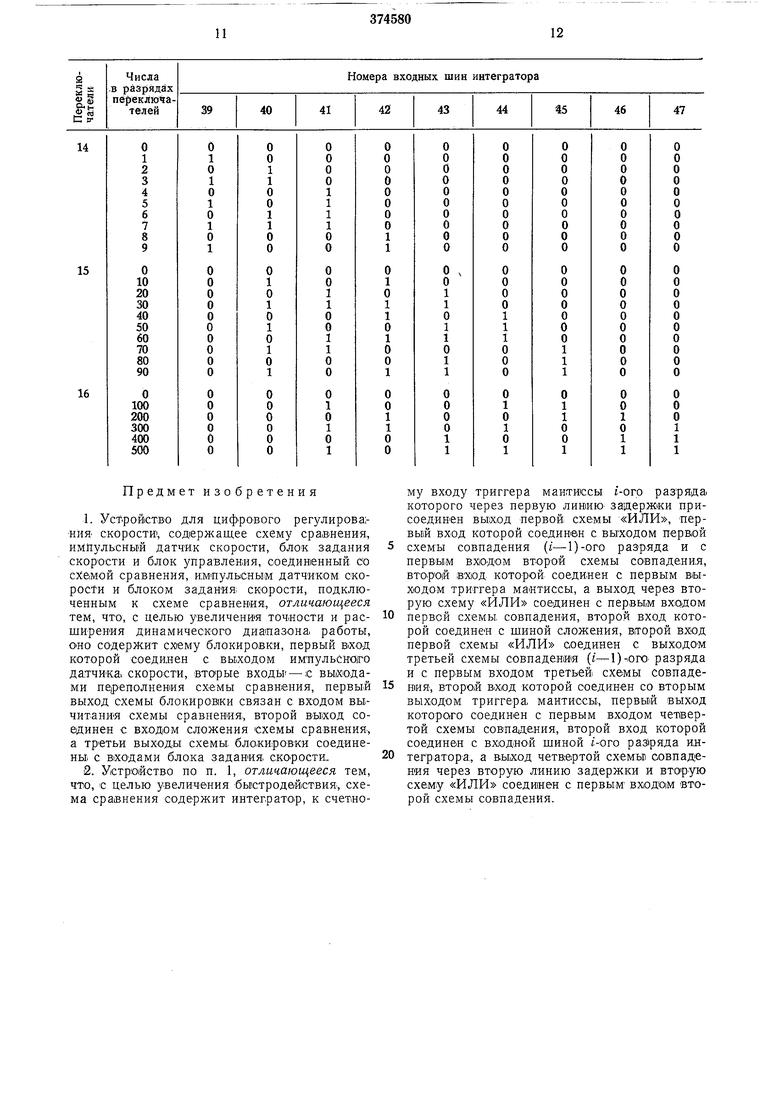

Декадньши переключателями 14-16 задаг ется требуемая скорость объекта, выраженная десятичным числом непосредственно в принятых единицах, например в метрах в секунду (м/сек). С помощью- дещифр.аторов 17-19 это число преоб.разуется поразрядно в параллельный двоичный код. Например, приняв период квантования ,01 сек и расстояние, проходимое объектом между двумя соседними импушьсами датчика скорости.

равным 1 мм, т. е. мм, можно с помощью предла.гаемого регулятора получать линейные скорости от 10 мм/сек и более, подавая на вход интегр-атора в каждом цикле сумму слагаемых .Л от 1 и выще, причем частота следования импульсов датчика 2, численно равна скорости объекта, выраженной

в мм/сек, . Огоанячиваясь скоростью объекта, равной 60 м/с.ек, можно составить таблицу поразрядного преобразов:ания десятичных чисел Л 1-599, где старщий разряд изображает десятки, средний - единицьь, а младщий - десятичные доли м.1сек,

в двоичный код. (Номера входных щин 39- 47 .интегратора соответствуют номерам era разрядов от 1 до 9).

Например, для получения скорости 17,6 м/сек на переключателях набирают число 176, так что через каждые 0,01 сек .в момевт начала очередного цикла квантования в сумматор подаются слага,емъ1е: командой III, поступающей по щине 33 и опрашивающей схемы 102 совпадения, на суммирующие входы интегратора через схемы «ИЛИ 103 и щинъ 39-47 выдается пе,рвое двоичное слагаемое 0,001001100, соответствующее деся.тичному числу 100, кома.ндой IV, поступающей по щине 34 и опращивающей схемы

101 совпадения, выдается второе слагаемое 0,011000100, соответствующее десятичному числу 70, командой V, поступающей по шине 35 и опрашивающей схемы- 100 совпадения, выдается третье слагаемое 0,011000000,

соответствующее десятичному числу 6. Диапазон регулирования может быть расширен за счет увеличения числа разрядов интегратора и соответствующего дополнения старшего дещифратора по правилу, вытекающему из

таблицы. Кроме того, возможно масщтабирование регулятора за счет выбора периода кв1антован1Ия Т и расстояния q, соответствующего дистанции, проходимой объектом за время между двумя соседними импульсами

датчика скорости.

11

12

| название | год | авторы | номер документа |

|---|---|---|---|

| Датчик времени | 1980 |

|

SU922706A2 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Устройство для допускового контроляОб'ЕКТА | 1979 |

|

SU834678A1 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Счетчик импульсов с визуальной индикацией | 1978 |

|

SU767973A1 |

| Преобразователь форматов данных | 1982 |

|

SU1092490A1 |

| Цифровой анализатор содержания углерода в жидкой стали | 1984 |

|

SU1359785A1 |

| Устройство для преобразования двоичного кода в десятичный и обратно для чисел с плавающей запятой | 1977 |

|

SU717755A1 |

Предмет изобретения 1.Устройство для цифрового регулирова;«и скорости , содержащее схему сравнения, импульсный датчик скорости, блок задания скорости и блок управления, соединенный со схемой сравнения, импульсным датчиком скорости и блоком задания; скорости, подключенным к схеме сравнения, отличающееся тем, что, с целью увеличения точиости и расширения динамического диапазона, работы, Оно содержит схему блокировки, иервый которой соединен с выходом импульсного датчика, скорости, вторые входы с выйодами пе|реполнен1ия схемы сравнения, первый выход схемы блокиров1ки связан с входом вычитания схемы сравнения, второй выход соединен с входом сложения схемы сравнения., а третьи выходы схемы блокировки соединены с В1ходами блока задания скорости,. 2.Устройство по п. 1, отличающееся тем, что, с целью увеличения быстродействия., схема сравнения содержит интегратор, к счетному входу триггера мантиссы г-ого разряда которого через первую линию задержки присоединен выход первой схемы «ИЛИ, первый вход которой соединен с выходом первой схемы совпадения (i-1)-ого разряда и с первым входом второй схемы совпадения, второй вход которой соединен с первым выходом триггера мантиссы, а выход через вторую схему «ИЛИ соединен с первым входом первой схемы, совпадения, второй вход которой соединен с шиной сложения, вггорой вход первой схемы «ИЛИ соединен с выходом третьей схемы совпадения (г-1)-ого. разряда и с первым входом третьей схемы совпадения, второй вжод которой соединен со вторым выходом триггера, мантиссы., первый выход которого соединен с первым входом чет1вертой схемы совпадения, второй вход кото.рой соединен с входной шиной г-ого разряда интегратора,, а выход четвертой схемы совпадения через вторую линию задержки и втор.ую схему «ИЛИ соединен с первым вх1одом второй схемы совпадения.

Г

во

CM

м

4-1

Авторы

Даты

1973-01-01—Публикация